Устройство для функционального контроля цифровых интегральных схем

Иллюстрации

Показать всеРеферат

Изобретение относится к контрольно-измерительной технике и может быть использовано в устройствах контроля динамического функппонировчния цифровых интегральных схем. устройстпо содержит бпок 1 анл кп глых компараторов , элементы 4 и памяти, выходной триггер 6, D-трш гсры 7, 8, 24, 25, блок 9 задержки ,Гиюк 10 коммутации , блок 26 коррекции. Устройство повыйдет частоту фупхпи.ятальн тго контроля за счет обеспечения синхронности сигналов на входах выходного триггера 6 . 2 ил .

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧШ1ИК

РЕСПУБЛИК (19) 111) 1684/ýü А (Я,.

1 °

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ is

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И (ЛНРЫТИЯМ

ПРИ ГКНТ СССР (21) 4726056/21 (22) 31 07.89 (46) 15. 10. 91. Вн>п. 9 38 (7 1) Научно-исследовательский HHc òèтут полупроводникового мап иностроения (72) В.В.Козлов и А.И.Лепехин (53) 62 1.317.799(088.8) (56) Авторское свидетельство СССР

11> 1337838, кл. С О! R 3!/28, 1986.

Авторское свидетельство СССР

И 1430915, кл. С О1 R 31!28, 1987. (54) УСТРОЙСТВО ДЛЯ сьУНК! ИОНАЛЬНОГО

КОНТРОЛЯ ИИФРОВЫХ ИНТЕГРАЛЬНЫХ СХЕМ! (57) Изобретение отн сится к контрол>-<о-измерительной технике и может быть использовано р устрой ствах к он тро l>R динамического Аункп>,онпровзния nuApoBbIx интегральных схс м, Устройство содержит <>TloK 1 àHë:t >говьгх компараторов, элемеHòû 4 и >;lëìяти, выходной триггер 6 I.-T;>è гC 1>ü> 7, 8 24, 25, блок 9 задержки.,блок 10 коммута— ции, блок 26 коррекпи». Устройство по—

Fibltt," т часто ту функ>пп>надьHëãë контроJ:ÿ за счет с беспечения ci»l>:ðî»íi>ñòè сигналов на входах выход: ого тригге— ра 6, 2 ил.

1684756

Изобретение относится к контрольноизмерительной технике и мпжет быть использовано для контроля динамического функционирования больших интеграль-5 ных схем.

Целью изобретения является повышение частоты функционального контроля за счет обеспечения синхронности сигналов на входах выходного триггера 10 устройства.

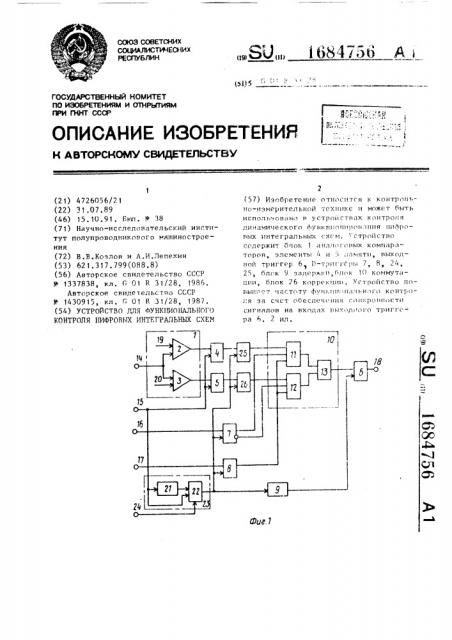

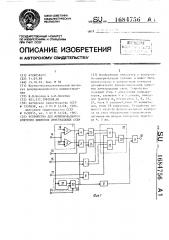

На фиг. 1 приведена схема устройства для функционального контроля цифровых интегральных схем (для одного вывода), на фиг. 2 — временные диаграммы, пояснякщие работу устройства.

Устройство содержит блок 1 аналоговых компараторов, выполненный на усилителях-компараторах 2 и 3, триггеры 4 и 5 памяти, выходной триггер

6, D-триггеры 7 и 8, первый элемент .

9 задержки, первый коммутатор 10, выполненный на логических элементах

И 11, 12 и элементе ИЛИ 13, инфор- 25 мационный вход 14, первый, второй и третий управляющие входы 15-17 устройства, выход 18 устройства, источники 19 и 20 опорных напряжений, второй элемент 2 1 задержки и второй коммутатор 22, образующие блок 23 коррекции, четвертый управляющий вход 24 устройства и D-триггеры 25 и 26.

Объединенные входы усилителей-компараторов 2 и 3 блока 1 аналоговых.. компараторов образуют информационный вход 14 устройства. Вторые входы усилителей-компараторов 2 и 3 раз- 40 дельно соединены с источниками 19 и 20 опорных напряжений, предназначеннымн для задания программируе11 11 я пс значений логических уровней 1 и " 0 " соответственно . Выходы У силн 4 5 телей -к омп ар а торо в 2 и 3 соединены с первыми входами триггеров 4 и 5 памяти, вторые входы которых соединены с первым управлякщим входом 15 устройства, входом элемента 21 задержки и первым входом коммутатора

22, второй вход которого соединен с выходом элемента 2 1 задержки, третий вход — с четвертым управлякщим входом 24 устройства а выход — с вхоЭ

55 дом элемента 9 задержки и с С-входами

D-триггеров 7, 8, 25 и 26, Выходы

D-триггера 7 соединены с первыми входами элементов 11, 12 И, образукщими первый и второй входы коммутатора

«О выходы триггеров 4 и 5 памяти соединены с D-входами триггеров 25

26, выходы которых соединены со вторыми входами элементов 11, 12 И, образукщими третий и четвертый входы коммутатора 10 пятый вход которого, образованный третьими объединенными входами элементов 11, 12 И, соединен с выходом второго D-триггера 8, °

Выходы элементов 11, 12 соединены со входами элемента 13 ИЛИ, выход которого, образующий выход коммутатора 10, соединен с первым входом выходного триггера 6, второй вход которого соединен с выходом элемента 9 задержки, а выход — с выходом 18 устройства. Первые входы D-триггеров 7 и 8 соединены со вторым и третьим управлякщими входами 16 и 17 устройства соответственно.

Блок 1 аналоговых компараторов предназначен для сравнения сигналов, поступающих с контролируемой схемы через информационный вход 14 на объединенные первые входы усилителейкомпараторов 2 и 3, с опорными напряжениями (уровнями "1" и "0"), поступающими на вторые входы усилителей-компараторов 2, 3 с выходов программируемых источников 19, 20 питания ".оответственно ° Триггеры 4 и 5 памяти предназначены для запоминания выходных состояний соответствующих усилителей-компараторов 2 и 3.

Выходной триггер 6 служит для формирования выходного сигнала, несущего информацию о результатах контроля

;"годен-брак" ), D-триггер 7 — для временного хранения сигнала управления выбором соответствукщего усилителя-компаратора блока 1, D-триггер

8 — для временного хранения сигнала разрешения прохождения информации через узлы коммутатора 10 на первый вход выходного триггера 6 (сигнала маскирования).

Элемент 9 задержки предназначен для задержки строб-импульса, поступакщего на управлякщий вход 15 устройства и проходящего через коммутатор 22 (с задержкой посредством элемента 2 1 или без задержки) на вход элемента 9 задержки. Время задержки сигнала в элементе 9 определяется временем распространения сигналов через коммутатор 10 и триггеры 7, 8, 25 и 26 °

5 16

Логические элементы 11, 12 И коммутатора «10 служат для пропускания информа :-;и с выходов D-триггеров 25, 26 на логический элемент 13 ".,1 по сигналам управления с D-триггеров 7 и 8. Логический элемент 13 ИЛИ предназначен для пропускания сигналов на первый вход выходного триггера 6.

Информационный вход 14 устройства служит для подключения контактного устройства с испытуемой цифровой интегральной схемой, Первый управляющий вход 15 служит для подключения источника строб-импульсов, вход 16 — для подключения источника эталонной информапии, вход 17 — для подключения источника управляющих сигналов (сигналон маскирования), а выход 18 — для подключения средств обработки информации.

Элемент 21 задержки служит для задержки строб-импульса, поступакще,го с управлякщего нхода 15, на величину, несколько большую максимально возможной величины зоны неопределенности эталонной информации и сигналов маскирования.

Коммутатор 22 предназначен для пропускания либо задержанного, либо незадержанного строб-импульса на входы D-триггеров 7, 8, 25, 26 и элемента 9 задержки в зависимости от сигнала управления, поступанжего на третий вход коммутатора 22 с четверто го управляющего входа 24 устройства.

Четвертый управляющий вход 24 служит для подключения источника управляющих сигналов, в качестве которого может быть использован блок памяти, подключенный к информационной шине ЭВМ.

Триггеры 25 и 26 предназначены для выравнивания во нермени информации, приходящей с блока 1 аналоговых компараторов через элементы памяти 4 и 5,, и информации, приходящей с выходов триггеров 7 и 8 (эталонной информации и сигналов маскирования).

Устройство для функционального контроля цифровых интегральных схем работает следующим, образом.

На информационный вход 14 устройства поступает выходной сигнал с испытуемой микросхемы с заданной частотой контроля Т (фиг.2, а). В блоке 1 аналоговых компараторов происходит сравнение выходных сигналов микросхемы с опорными уровнями напряже84756 !

30.35

45

50 нии 11оп1 ° 11оя о, зввавя омыли с ветственво и T(.÷ílè;!ìll 19 и 20 оп р-. ных напряжений. На выходе усилителяког=. «р=.-:о 2 9t р снРго уровня при этом фо, гицбы .,, с з "и Гнал ° пр .;iР/те h 1ый на .1иг.2 б, на вьводе усилителякомиаратор;: нижнРгс уровня ф.рмируется сиг:аг., приведенный на Фиг.2 и, гДР о — звпеРжка сигнала УсилителЯЛ ми-компарато1;.ями 2 и 3. С приходом строб-импульса на управляющий вход

15 (фиг.2 г) и. следовательно, на вторые входь. триггеров 4 и 5, в последние зепи знается информация, установленная : данный момент на выходах усилителей-компараторов 2 и 3 (фиг.2 д,е). Запись информации осуществляется по переднему фронту строб-импульса, ь, — задержка сигЛ нала триггерами 4 и 5. На управляющий вход 16 и, следовательно, на первый вход триггера 7 поступает сигнал эталонной информации (фиг.2 э), а на управляющий вход 17 — сигнал максирования (разрешения компариро нания, фиг.2 и). На управлякщий вход 24 подается сигнал управления работой коммутатора 22. Этот сигнал управляет работой коммута тора 22 таким образом, что на его выход проходит строб-импульс либо непосредственно с управляющего входа 15 (фиг.2 ж, пунктиром, момент времени t4), если его местоположение на временной диаграмме работы устройства не приходится на зону неопределенности эталонной информации и сигналов маскирования, либо через элемент 21 задержки, величина которой выбирается несколько большей максимально возможной величины зоны неопределенности эталонной информации и сигналов маскирования. На фиг.2 з,и эона неопределенности эталонной информации и сигналов маскирования имеет длительность

При установке строб-импульса в начале периода (момент времени tg, фиг.2 r) и коммутатора 22 в положен ние, при котором строб-импульс с входа 15 проходит через линию 2 1 задержки на выход коммутатора 22 (момент времени t<, фиг.2 ж) стробимпульсом с выхода коммутатора 22, задержанным на время ьg (запержка

I линии 21 задержки и коммутатора 22), осуще ствляе тся стробирона ние выходной информации триггеров 4 и 5, а

1684756 также эталонной информации, приходящей II;r управлякпяий вход 16 ((и! ." з); и сигналов маскирования, приходящих на вход 17 (фиг,2 и); при этом сигналы маскирования и эталонной ннАОрмации, синхронно поступающие на управляющие входы 17, 16, должнъ| быть установлены таким образом, чтобы передним Аронтом строб-импульса (момент 10 времени t<, см.фиг.2 ж) надежно Аиксировались указанные вьппе сигналы сразу же после их зоны неопределенности. Выходные сигналы прямых выходов триггеров 7 и 8 приведены на фиг." к,л1i соответственно. Оба эти сигнала, а также сигнал эталонной информации с инверсного выхода триггера 7 поступают в коммутатор 10, куда также поступают сигналы с выходов триггеров

25 и 26. Эти сигналы приведены на фиг.2 м н. Выравненные во времени сигналы с выходов триггеров 25, 26, 7, 8 и поступающие в коммутатор 10 обрабатываются им: сигнал " 1" на выходе коммутатора 10 формируется при условии "1" на выходе триггера 8, триггера 25 и прямом выходе триггера

7 или при условии "1" на выходе триггера 8, триггера 26 и инверсном вы- 30 ходе триггера 7. Выходной сигнал коммутатора 10 приведен на фиг,2 и, Строб-импульс с выхода коммутатора

22 через элемент 9 задержки, значение которой 2< ныбираеTñÿ нескольКо большим величины времени переKJIK чения триггеров 7, 8, 25, 26 и задержки элементов коммутатора 10, поступает на С-вход триггера 6 (фиг.2 р), фиксируя по переднему фронту инфор- 10 мацию, приходяшую с вьгэсода коммутатора 10 на первый вход триггера 6.

На вькоде триггера 6 при этом формируется сигнал, представленный на ф1 г.2 с. Если контролируемая инфор — (15 мация на выходе испытуемой схемы соответствует по своим логическим уровням заданным значениям "0" и "1", а также своему ожидаемому местоположению, то сигнал на выходе триггера 6 отсутствует. Это означает, что контролируемая цифровая микросхема функционирует верно, в противном случае на выходе триггера 6 формируется сигнал 1 — 6рак (в IlpHBpJlp.rrHov ilpH мере момент времени t<, фиг,2 с) .

При увеличении задержки строб-импульса до его положения ty (фиг.2 r) задержанный линией 21 задержки и коммутатором 22 строб-импульс (,эадержка

<) в момент времени t,. (дн: передним фронтом Аиксиру(т -; са; (-н: ю информацию и сигнал маек. .р(:;::B«rr того же цикла (фиг.2 з,и), но дальнейшее

yBcличение задержки строб-нэп(ту.тьса приведет к тому, что строб-импульсом с выхода коммутатора 22 недос"..-е--рно фиксируются эталонная информация и сигнал маскирования (строб-импульс заходит в зону неопределенности) . При этом на управляющий вход

24 подается сигнал, при котором комму (атор 22 передает строб-импульс с

BY(?crG 15 непосредственно на выход с и задержкой (q (фиг,2 ж, момент времени Г<) .для надежного фиксирования информации с выходов тригi еров 4 и 5 л величина задержки c > должна быть не=колько больше величины задержки тр(ггеров 4 и 5 (задержка С ).

Таким образом, в устройстBe обеспечивается синхроннссть всех сигналов, ноступалцих в коммутатор 10„ нсзависимо от состояния коммутатора 22, следствием чего является расширение частотного диапазона устройства (час" тата Аункционального контроля увели rvBaexcrr до 200 ИГц п(эи использовании для построения устройства микросхем серии 1500).

".э-едл;женное устройство для Аункцион.-гльногo контроля цифровых ИС планнр,ется использовать в комплексе контроля статических параметров и динамического фу|п-.ци-. .IèðoBä .Ièÿ сверхбсльших интегралыг(х схем с рабочей ч = с то той, пре выша ющей 100 N ц. формул а изобретения

Устройство для Аункционального кс1нтроля цифровых интегральных схем, сс держащее блок аналоговых компараторов, первый и втс рой триггеры памэ(ти, четыре D-тр-.ггера, выходной триг ер, блок задержки, блок коммутаЦии 6JTor:; KBPPPKIIBBэ пеРВ f юэ втоРУюэ третью, четвертую входные клеммы, выходную клемму и клемму для подключения объекта контроля, соединенн ю с входом блока аналоговых компараторов, выходы которого соединены с >отве тс твенно с первыми входами перв го и второго триггеров памяти, вторые входы которых соединены с перв;й входной клеммой, вторая и тре— тья входные клеммы соединены соотв ственно с первыми входами первого

1684756 ния частоты функционального кс. ";.Реля за счет обеспечения синхронност11

Составитель С.Петров

Техред Л,Сердюкова

Корректор А,Обручар

Редактор Н.Горват

Заказ 3506 Тирак Подписное

ВНИИПИ Государственного комитета по изрбретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.ужгород, ул . Гагарина, 101 и второго D-триггеров, вторые входы которых подключены к выходу блока коррекции, первый и второй входы которого соединены соответственно с первой и четвертой входными клеммами, выход третьего D-триггера соеди" нен с первым входом блока коммутации, выход которого соединен с первым входом выходного триггера, соединенного вторым входом с выходом

I блока задержки, а вьхслсм — с вьхорнсй клеммой, вторые входы третьего и че11вертого D-триггеров соединены с входом блока задержки, о т л и ч а ю— щ е е с я тем, что, с целью повышесигналов на входах выходного триггера, вход блока 3< )Tpðæêè соединен с выходом блока кср;:акции, прямой и инверсный выходы первого D-триггера соединены ссотяе-.:.твенно с вторым и третьим входами блока коммутации, выхол второго D-триггера соединен с четвертым входом блока коммутации, а выход четвертого D-триггера — с пятым входом блока коммутации, первые входы третьего и четвертого D-триггеров соединены со< тветстенно с выходами первого и второго триггеров памяти.