Двоичный @ -разрядный реверсивный счетчик

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной и вычислительной технике. Цель изобретения - расширение области применения. Счетчик содержит четырехразрядный реверсивный счетчик 1 и п-4 ячеек 2, состоящих из счетного триггера 4 и формирователя 3 на элементах И-НЕ и ИЛИ-НЕ. Быстродействие повышается за счет параллельного формирования по частям условия разрешения переключения разрядов счетчика. Входами устройства являются шины счетного сигнала и сигналов управления видом счета (прямой или обратный). 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

":.)s Н 0 > К 23/62

ГОСУДАРСТВЕННЫИ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗО6РЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) 1598172 (21) 4658165/21 (22) 01,03.89 (46) 15.10,91. Бюл. М 38 (72) Ю.Г.Дьяченко и С.Г,Селихов (53) 621.374,322(088.8) (56) Авторское свидетельство СССР

O 1598172, кл, Н 03 К 23/62, 1989, (54) ДВОИЧНЫЙ и-РАЗРЯДНЫЙ РЕВЕРСИВНЫй СЧЕТЧИК (57) Изобретение относится к импульсной и

Изобретение относится к импульсной и вычислительной технике и может использоваться при построении счетных, регистрирующих устройств, систем цифровой обработки информации.

Целью изобретения является расширение области применения за счет увеличения емкости.

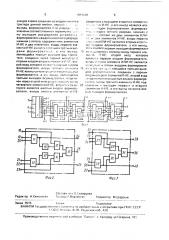

На фиг,1 изображен двоичный и-разрядный реверсивный счетчик; на фиг,2— формирователь нечетного разряда; на фиг,3 — схема формирователя четного разряда..

Схема и-разрядного счетчика содержит четырехразрядный двоичный реверсивный счетчик 1, ячейки счетчика 2-1-2-п, каждая иэ которых состоит иэ формирователя 3 и счетного триггера 4, счетный вход С счетчика 1 соединен с шиной 5 входных счетных сигналов, входы Е1 и Е2 управления счетом счетчика 1 соединены с шинами 6 и 7 входHblx сигналов управления соответственно, прямые выходы 01-04 считывания счетчика

1 и триггеров 4 ячеек устройства подключеЬО 1684928 A 2 вычислительной технике. Цель изобретения — расширение области применения. Счетчик содержит четырехразрядный реверсивный счетчик 1 и и-4 ячеек 2, состоящих из счетного триггера 4 и формирователя 3 на элементах И-НЕ и ИЛИ-НЕ. Быстродействие повышается за счет параллельного формирования по частям условия разрешения переключения разрядов счетчика, Входами устройства являются шины счетного сигнала и сигналов управления видом счета (прямой или обратный). 3 ил. ны к соответствующим шинам 8-1-8-и считывания устройства, первый выход расширения F< счетчика 1 подключен к первым входам формирователей 3 ячеек устройства, в второй выход расширения Fz счетчика 1 соединен с шестыми входами формирователей 3 ячеек 2-I устройства, второй и пятый входы формирователя 3 ячейки 2-5 подключены к шине источника логической "1", а третий и четвертый его входы соединены соответственно с выходами 04 и 04 счетчика

1, второй и пятый входы формирователя 3 каждой ячейки 2i (I - 6-и) подключены соответственно к первому и третьему выходам формирователя 3 предыдущей ячейки, третий и четвертый входы формирователя 3 каждой четной ячейки 2), ) - 6 8...п, соединены соответственно с инверсными и прямыми выходами триггера 4 предыдущей ячейки, третий и четвертый входы формирователя 3 каждой нечетной ячейки, начиная с

2-7, подключены соответственно к прямому и инверсному выходам триггера 4 предыду1684928

CI Cn Г1 01 Q?...QI <

С i Е) Q1 В . Q! 1.

25

30 )

50

55 щеи ячейки, второй выход формирователя 3 в каждой ячейке 21(l = 5.6,...,n) подключен к счетному входу триггера 4 данной ячейки, первый и третий выходы формирователя 3 ячейки 2-и соединены соответственно с flop вым 9 и вгорым 10 выходами расширения устройства, Схема формирователя нечетного разряда (фиг,2) состоит из элементов И-НЕ 11 — 15 и инверторов 16-17, имеет шесть входов

18 — 23 и три выхода 24-26, входы элемента

И-НЕ 11 являются вторым 19 и третьим 20 входами формирователя, а его выход, являющийся первым выходом 24 формирователя, через инвертор 16 соединен с первым входом элемента И-НЕ 12, второй вход которого является первым входом 18 формирователя, входы элемента И-НЕ 13 являются четвертым 21 и пятым 22 входами формирователя, а его выход, являющийся третьим выходом 26 формирователя, через инвертор 17 соединен с первым входом элемента И-НЕ 14, второй вход которого является шестым входом 23 формирователя, входы элемента И-НЕ 15 подключены к выходам элементов И-НЕ 12 и 14, à его выход является вторым выходом 25 формирователя.

Схема формирователя четного разряда (фиг,3) содержит два элемента ИЛИ-НЕ 27 и

28, элементы И-НЕ 29-31, шесть входов 32—

37 и три выхода 38--40, входы элемента

ИЛИ-НЕ 27 являются вторым 33 и третьим

34 входами формирователя, а его выход, являющийся первым выходом 38 формирователя, подкл1очен к первому входу элемента И-НЕ 29, второй вход которого является первым входом 32 формирователя, входы элемента ИЛИ-НЕ 28 являются четвертым

35 и пятым 36 входами формирователя, а его выход, являющийся третьим выходом 40 формирователя, соединен с первым входом элемента И-НЕ 30, второй вход которого является шестым входом формирователя

37, входы элемента И-HE 31 подключены к выходам элементов И-НЕ 29 и 30, а его выход является вторым выходом 39 формирователя.

Двоичный и-разрядный реверсивный счетчик работает следующим образом, На входную шину 5 поступают счетные сигналы Со, на шины 6 и 7 сигналы управления видом счета Е1 и Е2. При Е1=1, Е2=-0— прямой счет; при Е1=0, Е2=1 — обратный счет (на вычитание); при Е1=Е2=0 — блокировка счета(счетчик хранит свое состояние)

Комбинация Е1=Е2=1 является запрещенной. Выходы расширения Р1 и Fz счетчика формируют счетные сигналы соответственно нэ сложение и вычитание;1 -. вг х разрядог счетчика, начиная с пят .гз

Е1 - Со Е1QI Г1Г 0; (1) F:2 — Со Е2 Q1 Qz Q, (2) которые отрабатываются триггерами соответству1ощих разрядов при наличии на вхсдэх формирователей сигналов разреша1оы,,их переключение данного разряда. При э ом у.1рэлле11ие сче.н-., входа триггера -гс разряда пр-:дстэвляется в виде

0 Ф>енtгосгью;; :- мы является то, что сиги лы, 11;l решаю ни<: перек1ючение 1-го разряда, формиру о1ся в паузах счетных сигналов 01и Г для значений l: 72.Поэтому задерж1;э формирг1вэния счетного импульса для триггера i-го разряда (4<1 < 72) не зависит от ".-,нэчения l и равна 8 то, где To— задержка переключ ния инвертора, так как путь формирования гогого сигнала образуется дву>,яходовь и эл ментом ИЛИ-НЕ и тремя двух ходовыми ".лементами И-НЕ, .1> о р M ÷ ë J 11 з г 6 р е т е н и я

Двоичный п-рэ.-;ря,ейный реверсивный сче тчнк по а г. св. f 1598172, о т л и ч а юшийся reM, что. с целью расширения облэ.; рил ен;-ия зэ счет увеличения емкости с-етчикэ, в IIofG введены и-4 ячеек, ка>кдэя из ко орых состоит иэ счетного триггера и формировэтеля, прямые выходы счетных триггеров яче к подключены к соответствуюв1им шинам считывания устройства, первый и шестой входы формирователей всех разрядов, начиная с пятого, по,1ключены соответственно к первому и в орому выходэм расширения четырехраэрядного счетчика, второй и пятый входы формирователя каждого разряда, начиная с шестгчо, соединены соответственно с первым и третьим выходами формирователя предыдущего разряда, второй и пятый входы формирователя пятого разряда подключены к шине источника логической "1", третий и четвертый входы формирователя.каждого нечетного разряда, начиная с пятого, подключены соответственно к шинам прямого и инверсного значений выхода считывания предыдущего разряда, третий и че. вертый входы формирователя каждого че ного разряда. начиная с шестого, соединены ooI:lfoI ..твенно с инверсным и прядым выходами г иг. .рв предыдущего

paçp.=., э, второй выход формирователя в

16Н4ЫВ б

Ф9

24

22

23 б у

Фиг.2

Фаг3

Состави ель Q.Скворцова

Тех ред г, ..Моргентал Корректор М.Шароши

Редактор Н.Каменская

Заказ 3515 Ти; ак Подписное

ВНИИПИ Государственного комитетэ по изобретениям и открытиям при ГКНТ СССР

1 l0;"5 h,",; сквэ..Ж-35, Раушская наб„ /5

Производственно-издатель кий комбинат Патент", г. Ужгород, ул.Гагарина, 101 каждой ячейке соединен со входом счетного триггера данной ячейки, первый выходы формирователя и-го разряд;, ключены соответственно к первому и в; ..:;му выходам расширения устроис1;;. формирователь каждого нечетного разряда, начиная с пятого, содержит пять элементов

И-НЕ и два инвертора, входы первого элемента И-НЕ являютс,1 атаевым и тре-ьим входами формироватег:.с, а его выход, 0 являющийся первым выходом фон ««рователя, соединен через первый инвртор с первым входом второго земан "а И- "- второй вход которого яеляег. я пер=.üì сходом формирователя, входы р.тье —. эг о: .:нта 15

И-НЕ являются четвер; ым и пя ым схо„ эми формироватоля, д его выход явля,ощийся третьим выходом фсрмиг свателя, и дк. ючен через второй HHRE.ð÷îð к:.ерьсм., входу четвертого элемента И-НЕ, второ i г„.од ко- 20 торого является шесть.м входоь формирователя, входы пятого элемента И-НЕ соединены с выходами второго и четвертого

-.в И-НЕ, а его выход является вто: -.: одом формирователя, формироват -лн, .:кдого четного разряда, начиная с . состоит из двух элементов ИЛИ;::-- и рех элементов И-НЕ, входы первого ..: е. : чта ИЛИ-НЕ являются вторым и третьим входами формирователя, а его выход,

:-..-ee„-т.iv: и пятым входами формирователя. а его ь х;ц, s:,rtÿþùèéñÿ третьим выходом фсрмиго ;ателя, соединен с первым входом втс рмо элемента И-НЕ, второй вход

:-.второго является шестым входом формирога геля, влоды третьего элемента И-НЕ подкл;очс ы к выходам первого и второго

=лементов И-НЕ, à его выход является втооь м гыходом формирователя.