Пороговое устройство с порогом два

Иллюстрации

Показать всеРеферат

Изобретение относится к микроэлектронике и импульсной технике и преднззначенб для реализации пороговой функции с порогом два, зависящей от девяти двоичных переменных. Цель изобретения - расширение области применения логического модуля за счет реализации пороговой функции от девяти двоичных переменных. Поставленная цель достигается тем, что логический модуль содержит десять элементов ИЛИ-НЕ 1 - 10, два элемента равнозначности 11 и 12, четыре элемента неравнозначности 13 - 16, четыре элемента И-НЕ 17-20, элемент НЕ 21, девять входных 22 - 30 и одну выходную 31 шины. Логический модуль работает следующим образом. На входные шины подаются двоичные переменные Xi...Xg (в произвольном порядке). На выходной шине формируется мажоритарная функция с порогом два F F(Xi. X2) согласно соотношению F 1, если Xi 2: F 0 I 1 если 2, Xi 1. 7 ил i 1 (Л С

СОЮЗ СОВЕТСКИХ

СОЦИАЛ ИСТИЧЕ СКИХ

РЕСПУБЛИК (я)з Н 03 К 19/00

ГОСУДАРСТВЕ 1+1ЫЙ КОМИТЕТ

flO ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ если Xi <1,7ил (21) 4774762/21 (22) 11.10.89 (46) 23,01,92. Бюл, М 3 (72) Л,Б.Авгуль, Н.А.Егоров, О.В.Подрубный и С.M.Òåðåøêî (53) 681,325.65 (088.8) (56) Авторское свидетельство СССР

М 1598161, кл. Н 03 К 19/094, 1989.

Патент США М 4087786, кл. 340 — 146, 1978. (54) ПОРОГОВОЕ УСТРОЙСТВО С ПОРОГОМ ДВА (57) Изобретение относится к микроэлектронике и импульсной технике и предназначенб для реализации пороговой функции с порогом два, зависящей от девяти двоичных переменных. Цель изобретения — расширение области применения логического модуля за счет реализации пороговой функции от

„„Я „„1707755 А1 девяти двоичных переменных. Поставленная цель достигается тем, что логический модуль содержитдесять элементов ИЛИ-НЕ

1 — 1О, два элемента равнозначности 11 и 12, четыре элемента неравнозначности 13—

16, четыре элемента И-НЕ 17 — 20, элемент

НЕ 21, девять входных 22 — 30 и одну выходную 31 шины. Логический модуль работает следующим образом, На входные шины подаются двоичные переменные

X1...X9 (в произвольном порядке). На выходной шине формируется мажоритарная функция с порогом два F = F(X1. Х ) согласно соотношению F = 1, если Х 2: F = 0

1=1

1707755

F=

1. если Х « 2;

1=1

О, если

Х 1

40

50

Изобретение относится к микроэлектронике и импульсной технике и предназначено для реализации пороговой функции с порогом два, зависящей от девяти двоичных переменных.

Цель изобретения — расширение области применения порогового устройства за счет реализации пороговой функции от девяти двоичных переменных.

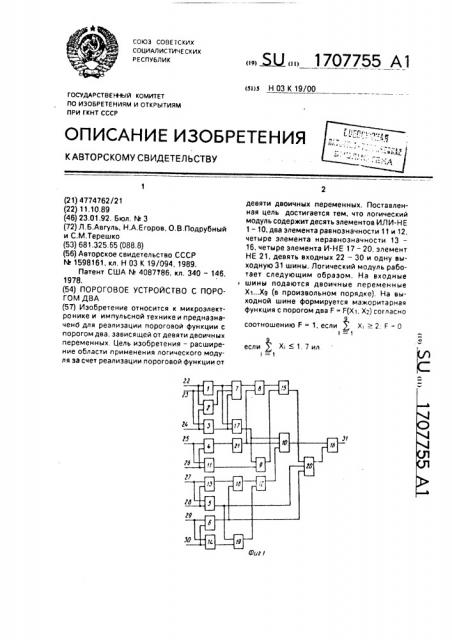

На фиг,1 приведена функциональная схема порогового устройства; на фиг.2 — 7— принципиальные схемы выполненных на

MOll-транзисторах, соответственно, логических элементов ИЛИ-НЕ на два входа, ИЛИ-НЕ на три входа, И-HE на два входа, И-НЕ на три входа, равнозначности/неравнозначности на два входа и элемента НЕ, входящих в состав модуля.

Пороговое устройство содержит (фиг.1) десять элементов ИЛИ-НЕ 1 — 10, два элемента 11 и 12 равнозначности, четыре элемента 13 — 16 неравнозначности 13 — 16, четыре элемента И-НЕ 17-20, элемент НЕ

21. девять входных шин 22 — 30 и выходную шину 31.

Двувходовый элемент ИЛИ-HE (фиг.2) собран на двух переключательных 32 и 33 и одном нагрузочном 34 MOIL-транзисторах, включенных между шинами 35 и 36 питания, Первая 37 и вторая 38 входные шины эле ента соединены соответственно с затворами транзисторов 37 и 38, выходная шина

34 (со стоками

39 — с истоком транзистора транзисторов 32 и 33).

Трехвходовый элемент ИЛИ- HE (фиг.3) собран на трех переключательных 40 — 42 и одном нагрузочном 43 МОП-транзисторах, включенных между шинами 44 и 45 питания.

Первая 46, вторая 47 и третья 48 входные шины элемента соединены соответственно с затворами транзисторов 40 — 42, выходная шина 49 — с истоком транзистора 43 (со стоками транзисторов 40 — 42).

Двувходовый элемент И-НЕ (фиг.4) собран на двух переключатальных 50 и 51 и одном нагрузочном 52 МОП-транзисторах, включенных между шинами 53 и 54 питания.

Первая 55 и вторая 56 входные шины элемента соединены соответственно с эатворами транзисторов 50 и 51, выходная шина 57 — с истоком транзистора 52 (со стоком транзистора 50).

Трехвходовый элемент И-НЕ (фиг.5) собран на трех переключательных 58 — 60 и одном нагрузочном 61 МОП-транзисторах, включенных между шинами 62 и 63 питания.

Первая 64, вторая 65 и третья 66 входные шины элемента соединены соответственно с затворами транзисторовБ8- 60, выходная

25 шина 67 — с истоком транзистора 61 (со штоком транзистора 58), Элемент равнозначности/неравнозначности (фиг,б) собран на двух переключательных 68 и 69 и трех нагрузочных 70 — 72

MOil- транзисторах, включенных между шинами 73 и 74 питания. Первая 75 и вторая 76 входные шины элемента соединены соответственно с затворами транзисторов 68 и

69, Нэ выходной шине 77 (исток транзистора 70) реализуется функция равнозначности, нэ выходной шине 78 (исток транзистора 69) — функция неравнозначности (сложения по модулю два).

Элемент НЕ (фиг.7) собран на одном переключательном 79 и одном нагрузочном

80 МОП-транзисторах, включенных между шинами 81 и 82 питания. Входная шина 83 соединена с затвором транзистора 79. выходная шина 84 — с истоком транзистора 80 (co стоком транзистора 79).

Пороговое устройство работает следующим образом, На входные шины 22 — 30 подаются двоичные переменные Х1...X9 (в произвольном порядке), на выходной шине 31 формируется пороговая функция с порогом два F=F(XI, X9) согласно соотношению в

Таким образом, пороговое устройство позволяет обнаружить наличие двух и более единиц в девятиразрядном байте двоичной информации. Это дает воэможность использовать его при построении цифровых устройств различного назначения, в том числе и блоков реконфигурации в отказно-устойчивых системах с самодиагностикой и самовосстановлением, Формула изобретения

Пороговое устройство с порогом два, содержащее четыре элемента И-НЕ и четыре элемента неравноэначности, о т л и ч аю щ е е с я тем, что, с целью расширения области применения за счет реализации пороговой функции от девяти двоичных переменных с порогом два, оно содержит элемент НЕ, два элемента равнозначности и десять элементов ИЛИ-НЕ, первая входная шина первого из которых соединена с первой входной шиной устройства и первой входной шиной второго элемента ИЛИ-НЕ, 1707755

Сс

Фиг. 3 вторая входная шина которого соединена с второй входной шиной устройства и первой входной шиной третьего элемента ИЛИНЕ, вторая входная шина которого соединена с третьей входной шиной устройства 5 и второй входной шиной первого элемента

ИЛИ-НЕ, выходная шина которого соединена с первой входной шиной четвертого элемента ИЛИ-НЕ и первой входной шиной первого элемента И-НЕ, вторая вход- 10 ная шина которого соединена с выходной шиной третьего элемента ИЛИ-НЕ и второй входной шиной четвертого элемента

ИЛИ-НЕ, третья входная шина которого соединена с выходной шиной второго элемента ИЛИ-НЕ, а выходная шина — с первой входной шиной пятого элемента 15

ИЛИ-НЕ, выходная шина которого соединена с первой входной шиной первого элемента неравнозначности, вторая входная шина которого соединена с выходной шиной шестого элемента ИЛИ-НЕ, первая 20 входная шина которого соединена с выходной шиной первого элемента равнозначности, вторая входная шина соединена с выходной шиной первого элемента И-НЕ и первой входной шиной седьмого элемента 25

ИЛИ-НЕ, вторая входная шина которого соединена с выходной шиной второго элемента равнозначности, третья выходная шина соединена с второй входной шиной пятого элемента ИЛИ-НЕ и выходной ши- 30 ной элемента НЕ, входная шина которого соединена с выходной шиной восьмого элемента ИЛИ-НЕ, 1-я (1=1,2) входная шина которого соединена с1-й входной ы ной перг ого элемента равнозначности и (1+3)-й входной шиной устройства, (I-5)-я входная шина которого соединена с I-й входной шиной девятого элемента ИЛИ-НЕ и 1-й входной шиной второго элемента неравнозначности, выходная шина которого соединена с первой входной шиной второго элемента И-НЕ, выходная шина которого соединена с первой входной шиной второго элемента равнозначности, вторая входная шина которого соединена с выходной шиной четвертого элемента И-НЕ, первая входная шина которого соединена с выходной шиной девятого элемента ИЛИНЕ и первой входной шиной третьего элемента И-НЕ, вторая входная шина соединена с выходной шиной третьего элемента неравнозначности, 1-я входная шина которого соединена с (1+7)-й входной шиной устройства и I-й входной шиной десятого элемента ИЛИ-НЕ, выходная шина которого соединена с второй входной шиной в орого элемента И-НЕ и второй входной шиной третьего элемента И-НЕ, третья входная шина которого соединена с выходной шиной первого элемента равнозначности, а выходная шина — с первой входной шиной четвертого элемента равнозначности, вторая входная шина которого соединена с выходной шиной седьмого элемента ИЛИ-НЕ, а выходная шина — с выходной шиной устройства.

1707755

ФКГ ° 4

ФКР, 6

Составитель О. Скворцов

Техред М.Моргентал Корректор С. Черни

Редактор И. Шмакова

Производственно-издательский комбинат "Патент". г. Ужгород. ул.Гагарина, 101

Заказ 275 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская нэб., 4/5