Оперативное запоминающее устройство с коррекцией ошибок

Иллюстрации

Показать всеРеферат

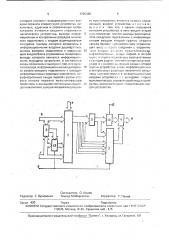

Изобретение относится к вычислительной технике, а именно к запоминающим устройствам со встроенной коррекциейошибок, и может быть использовано при создании интегральных схем. Целью изо бретения является упрощение контроля устройства. Устройство содержит накопитель.- формирователь контрольных разрядов, формирователь синдрома, дешифратор, блок управляемых инверторов, первый и второй мультиплексоры. Цель изобретения достигается за счет возможности непосредственной проверки избыточной части накопителя и исключения, отдельных циклов имитации ошибок в режимах записи для проверки схем коррекции, а также за счет совмещения в режиме считывания вывода на информационные выходы устройства контрольных разрядов и разрядов синдрома. 1 ил.Изобретение относится к вычислительной технике, а именно к запоминающим устройствам со встроенной коррекцией ошибок, и может быть использовано при создании интегральных схем.Целью изобретения является упрощение контроля устройства.На чертеже представлена структурная схема оперативного запоминающего устройства с коррекцией ошибок.Устройство содержит накопитель 1, первый мультиплексор 2, формирователь 3 контрольных разрядов, блок 4 управляемых инверторов, формирователь синдрома 5, входы 6 управления накопителем, информационные входы 7 и 8 первой и второй групп, первый 9 и второй 10 управляющие входы, информационные выходы 11, дешифратор 12 и второй мультиплексор 13.Устройство .работает следующим образом.Выбор режима работы устройства осуществляется с помощью управляющих сигналов с входов 9 и 10, а также с помощью сигнала "Запись/Считывание", поступающего на один из входов 6 устройства.Основные (рабочие) режимы работы устройства выбираются при установке на вХодах 10 и 9, положим, сигналов логической "1" и "О" соответственно! В этом случае при записи в накопитель 1 заносятся данные со входов 7 и 8, а также биты контрольных разрядов, сигналы которых снимаются с выходов формирователя 3. Положим также, что входное слово имеет восемь информационных разрядов и, следовательно, при использовании кодов Хзмминга число формируемых контрольных разрядов равно 4. При этом разбиение ворьмивходных информационных 'шин на входы 7 и 8 двух равных групп осуществляется произвольным образом.*слсVJ о о со ю о

C0fG3 СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (ЯМ G 11 С 29/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4609606/24 (22) 24,11,88

{46) 30.01,92. Бюл. N.4. (72) А.С, Березин, B.В. Маринчук, П.Б. Поплевин, С,В. Сушка, С.А. Трошин и П,Ю. Чекмазов

{53) 681.327.6(088.8) (56) Огнев И.В., Сарычев К,Ф, Надежность запоминающих устройств, М.: Радио и связь, 1988, рис. 13.5, с. 188.

Патент США hh 4561095, кл. 371/38, 1985, (54) ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С КОРРЕКЦИЕЙ ОШИБОК (57) Изобретение относится к вычислительной технике, а именно к запоминающим устройствам со встроенной коррекцией

Изобретение относится к вычислительной технике, а именно к запоминающим устройствам со встроенной коррекцией ошибок, и может быть использовано при создании интегральных схем.

Целью изобретения является упрощение контроля устройства, На чертеже представлена структурная схема оперативного запоминающего устройства с коррекцией ошибок. . Устройство содержит накопитель 1, первь:й мультиплексор 2, формирователь 3 контрольных разрядов, блок 4 управляемых инверторов, формирователь синдрома 5, входы буправления накопителем, информационные входы 7 и 8 первой и второй групп, первый 9 и второй 10 управляющие входы, информационные выходы 11, дешифратор

12 и второй мультиплексор 13.

Устройство .работает следующим образом. Ж 17О9ЗМ А1 ошибок, и может быть использовано при создании интегральных схем. Целью изо бретения является упрощение контроля устройства, Устройство содержит накопитель, ° формирователь контрольных разрядов, формирователь синдрома, дешифратор, блок управляемых инверторов, первый и второй мультиплексоры. Цель изобретения достигается за счет возможности непосредственной проверки избыточной части накопителя и исключения. отдельных циклов имитации ошибок в режимах записи для проверки схем коррекции, а также за счет совмещения в режиме считывания вывода . на информационные выходы устройства контрольных разрядов и разрядов синдрома. 1 ил.

Выбор режима работы устройства осуществляется с помощью управляющих сигналов с входов 9 и 10, а также с помощью сигнала "Запись/Считывание", поступающего на один из входов 6 устройства.

Основные (рабочие) режимы работы устройства выбираются при установке на входах 10 и -9, положим, сигналов логической

"1" и "0" соответственно. В этом случае при записи в накопитель 1 заносятся данные со входов 7 и 8, а также биты контрольных разрядов, сигналы которых снимаются с выходов формирователя 3. Положим также, что входное слово имеет восемь информационных разрядов и, следовательно, при использовании кодов Хэмминга число формируемых контрольных разрядов равно 4.

При этом разбиение восьми входных информационных шин на входы 7 и 8 двух равных групп осуществляется произвольным образом.

7709396

2ц

Р рабочем, режиме считывания второй мультиплексор 13 пропускает на информационные входы блока 4 управля8мых инверторов сигналы информационных разрядов считанного иэ накопителя 1 слова. При этом расшифровка кода синдрома дешифратором 12 разрешена, и поэтому блоки 4, 5, 12 обеспечива|от исправление возможных однократных Ошибок В счита1 ных из наког1итала словах данных, Г!Омимо основного режима работы, устройство может работать во вспомогательньх режимах, обеспечивающих Выявление устройств, имеющих скрытые дефекты, Вспомогательные режимы работы, используемые ,.а этапе, тестирования ОЭУ, вклiочз от процедуры проверки работоспост>бности ЭП хранения информационных и контрольных разрядов накопителя 1, а также совокупности схем коррекции ошибок.

Е режиме проверки ЭП хранения информационных разрядов на входах 9 и !0 поддерживаются сигналы логического "0".

Поэтому в ре>киме считывания на выходы мультиплексора 2 сигналы поступают с Выходов информационных разрядов накопителя ". и, поскольку коррекция ошибок не про .,Водится, эти же сигналы присутству.от и нз lUMHBx инфо(>мационных ВыхОДОВ 11 устройства, Другим вспомогательным режимом рабо-ы п!..едложенного устройства является ре>ким проверки ЭП хранения контрольных разрядов = Отличие от устройства-прототипа. информация в ЭП контрольных разрядов накопителя 7 записывается непосредственно с внешних выходов ОЗУ (в устройстве-прототипе запись и формации

B ЭП кОнтрольных p33pAäoo Всегда Осуществлялась с выходов формирователя контрольных разрядов). Это обеспечивается установкой на входе 9 сигнала уровня логической "1" и пропуском через первый мультиплексор 13 сигналов со входов 7 устройства, Гсли затем устройство Переводится в ре>ким считывания, то при отсутствии коррекции ошибок (сигналов логического "0" на входе 10) через второй мультиплексор 2 на информационные входы бло:a 4 управляемых инверторов поступают 4-разрядный код контрольных разрядов слова и 4-разрядный код синдрома. Так как сигнал на входе 10 переводит Все выходные сигналы д:шифратора 12 в состояние "0", то блок 4 уп,>звляемых инверторов пропускает на вых;.ды устройства 11 сигналы с выходов мультиплексора 2 без изменения, Т.е. при такой последовательности циклов работы

ОЗУ производится прямая проверка работоспособности ЭГ! контрольных разрядов накопителя 1, что делает их проверку аналогичной проверке ЭП информационных разрядов, Следовательно, не требуется изменения программных средств внешнего устройстВа контроля.

Вместе с тем прямое занесение информации со входов ОЗУ в ЭП контрольных разрядов позволяет искл очить режим (а следовательно, и технические средства) принудительной генерации ошибокдля проверки работоспособности схем коррекции ошибок, Действительно, при занесении в

ЗП контрольных разрядов кодов с информационных входов 7, а в ЗП информационных разрядов-кодов со входов 7 и о возникает несоответствие между информационными и контрольными разрядами записанных в накопитель 1 слов (под несоответствиеM понимается то, что контрольные разряды, записанные в накопитель 1, «е соответствует тем, которые были бы получены по информационным разрядам входов 7 и 8 с помощью формирователя 3 контрольных разрядов. Следовательно, при считывании таких слов из накопителя 1 на выходах форлирователя синдрома 5 будут присутствовать ненулевые коды, Т.е, нугем анализа выводимых вместе г. кон,рольными разрядами через второй мультиплексор 2 кодов синдрома мсжно сделать вь вод о работоспособности формирователя синдрома 5, который В сравнении с другими блоками 4 и

12, является наиболее сло>кной схемой, Если же возникает необходимость о провеоке дешифратора синдрома 12 и блока 4 управ ляемых инверторов, то после занесения в накопитель 1 "ошибочной" комбинации информационных и l(oHTpoflbHblx разрядов сигнал на входе 10 следует перевести в состояние логической " !" (Включение коррекции ошибок) и по тому, какие изменения претерпевает считанное из накопителя

1 информационное слово нз выходах 11, дела от вывод о работоспособности схем коррекции ошибок, Таким образом, технико-экономическое прйимущество устройства заключается В упрощении контроля 03У, что достигается за счет прямой проверки ЗП хранения контрольных разрядов, искл очения отдельных циклов генерации ошибок в режимах записи для проверки схем коррекции ошибок и совмещения в режиме считывания проверки

ЭП контрольных разрядов и блока формирования синдрома.

Формула изобретения

Оперативное запоминающее устройстоо с коррекцией ошибок, содержащее формирователь контрольных раэрядог„ входы

1709396

- 11

Составитель О. Исаев

Редактор Т. Орловская Техред M.Ìîðãåíòàë Корректор T. Палии

Заказ 430 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", r, Ужгород, ул.Гагарина, 101 которого являютс информационными входами первой и второй групп устройства, на. копитель, адресные и управляющие входы

l(oTo poi о я вл я ются входами уп ра вл е н .1я накопителем устройства, выходы информационных и контрольных разрядов накопителя подключены к входам формирователя синдрома, выходы которого соединены с информационными входами дешифратора, выходы которого подключены к управллloщим входам блока управляемых инверторов, выходы которого являются информацио.:— ными выходами устройства, а сигнальные

1 входы соединены с выходами первого мультиплексора, информационные входы первого канала которого подключень1 к выходам информационных разрядов накопителя, Mhlформационные входы первой группы второго канала первого мультиплексора соединены с выходами контрольных разрядов накопителя, а управляющий вход первоro мультиплексора является первым управляющим входом устройства, а т л и ч а ющ е е с я тем, что, с целью упрощения контроля устройства, в него введен второй

5 мультиплексор, причем выходы формирователя синдрома подключены к информационным входам второй группы второго канала tl6pBol . фльтиплексора, управляюЩИй ВХОД,а СРСго СОЕДИНЕН С УПРаВЛЯЮ10 .цим входа-; в1..рого мультиплексора, инфоом-.ö.1oí"è.. входы первой и второй групп кг,.тороо 1о, кл1очены соответственно к II iходам форми пвателя контрольных разрядов и к инфаркт;ац онным входам второй

15 I pgBI1hl QcTpoMGTBB, I ofjh! информацио! IHI lx и контрольных разрядов накопителя соединены соответственно с информационными входами устройствi .: с выходами .1-.араго мультиплексора, управля:ощий вход лешиф20 ратора являе|гся вторым управляющим входом устройства.