Пирамидальный дешифратор

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при построении легко тестируемых устройств. Цель изобретения - сокращение времени диагностики пирамидального дешифратора . Пирамидальный дешифратор строится на основе двухвходовых узлов дешифрации, каждый из которых содержит две группы элементов равнозначности и четыре группы мажоритарных элементов. С помощью четырехразрядного входа задания режима работы узла дешифрации осуществляется тестирование узла дешифрации. Этот тест применим и к пирамидальному дешифратору , построенному многоуровневым способом из узлов дешифрации. 1 табл, 2 ил.

союз советских

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

s G 06 F 11/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

-;)0ь „2 (-) „ -1 б |г в в от твн

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1 (21) 4755027/24 (22) 24.08.89 (46) 15.04.92. Бюл. М 14 (72) М. M. Татур, А. В. Драенков, Н. В. Фурашов и Л. Б. Авгуль (53) 681.3(088.8) (56) Потемкин И. С., Функциональные узлы цифровой автоматики. M.: Энергоиздат, 1988, с. 90.

Каган Б. М., Канеаский М. M. Цифровые вычислительные машины и системы, М.:

Энергия, 1970, с. 201. рис. 3 — 66. (54) ПИРАМИДАЛЬНЫЙ ДЕШИФРАТОР. (57) Изобретение относится к вычислительной технике и может быть использовано при

Изобретение относится к вычислительной технике и может быть использовано при построении легкотестируемых цифровых устройств.

Целью изобретения является сокращение времени диагностики пирамидального дешифратора.

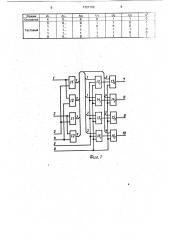

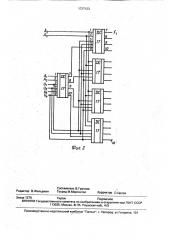

На фиг, 1 приведена функциональная .схема узла дешифрации с разрядностью информационного входа n=2; на фиг. 2 приведена функциональная схема пирамидального дешифратора с разрядностью информационного входа N.=4 и числом уровней К=2.

Узел дешифрации содержит разряды 1, 2 информационного входа узла дешифра-. ции, разряды 3-.6 входа задания режима ра, боты узла дешифрации(01-U4), выходы 7-10 узла дешифрации, группы 11, 12 элементов равнозначности, группы 13-16 мажоритарных элементов.

„„Я „„1727123 А1 построении легко тестируемых устройств.

Цель изобретения — сокращение времени диагностики пирамидального дешифратора, Пирамидальный дешифратор строится на основе двухвходовых узлов дешифрации, каждый иэ которых содержит две группы элементов равнозначности и четыре группы мажоритарных элементов. С помощью четырехразрядного входа задания режима работы узла дешифрации осуществляется тестирование узла дешифоации. Этот тест применим и к пирамидальномудешифратору, построенному многоуровневым способом иэ узлов дешифрации. 1 табл, 2 ил, Пирамидальный дешифратор содержит два уровня узлов 17 дешифрации.

Пирамидальный дешифратор работает следующим образом.

Пирамидальный дешифратор имеет два режима работы — основной и тестовый, В основном режиме на разряды 3 — 6 входа задания режима работы пирамидального дешифратора (U>-U4) поступает комбина-, ) ция 0110. При этом первые группы 11 эле- () ментов равнозначности всех узлов 17 дешифрации выполняют функции инверторов, а вторые группы 12 элементов равнозначности — функцию повторителей, Мажоритарные элементы групп 13-16 узла 17 дешифрации первого уровня реализуют функции конституент единицы, единичный сигнал с выхода узла 17 дешифрации первого уровня, поступая на разряд 5 входа задания режима работы соответствующего узла 17 дешифрации второго уровня, разрешает его

1727123 работу. Нулевой сигнал с выхода узла 17 дешифрации первого уровня блокирует работу соответствующего узла 17 дешифрации второго уровня.

На информационный вход(разряды А1—

А ) пирамидального дешифратора в основном режиме подается дешифрируемое слово.

В тестовом режиме на информационный вход пирамидального дешифратора (разряды A> — A<) подаются всего две комбинации: все нули или все единицы. На вход задания режима работы пирамидального деш иф ратора (разряды О >-0 ) подается тест, состоящий из пяти комбинаций и являющийся полным в классе одиночных константных неисправностей.

Задание режимов работы сведено в таблицу, Таким образом, пирамидальный дешифратор имеет полный проверяющий тест, состоящий из пяти наборов, при этом разрядность входа задания режима работы и состав теста не зависят от разрядности дешифрируемого слова.

Формула изобретения

Пирамидальный дешифратор, содержаN щий К уровней узлов дешифрации (К= —, где

N — разрядность дешифрируемого числа, и — разрядность информационного входа узла дешифрации, причем J-й разряд информационного входа узла дешифрации первого уровня подключен к j-му разряду информационного входа пирамидального дешифратора, J-й разряд информационного входа каждого узла дешифрации i-го уровня, подключенн к (n(l — 1)+Д-му разряду информационного входа пирамидального дешифратора (1< J <и,,2 < l «< К), выходы узлов дешифрации последнего уровня подключены к соответствующим разрядам информационного выхода пирамидального дешифратора, о тл и ч а ю шийся тем, что, с целью сокращения времени диагностики пирамидального дешифратора, каждый узел дешифрации содержит две группы элементов равнозначности и 2 групп мажоритарных элементов по и элементов в каждой, причем в каждом

20 ro элемента группы, кроме последнего, соединен со вторым входом последующего

30

40 ния режима работы (1+2"(т — 1))-го узла дешифоации (Р+ 1)-го уровня (1< 1<2"

m=2", 1 < P < К-1), четвертые разряды входа задания режима работы узловдешиф45 рации всех уровней, начиная со второго, подключены к четвертому разряду входа за5

10 узле дешифрации первые входы !-x элементов равнозначности первой и второй групп подключены к)-у разряду информационного входа узла. дешифрации, вторые входы элементов равнозначности первой группы подключены к первому разряду входа задания режима работы узла дешифрации, вторые входы элементов равнозначности второй группы подключены к второму разряду входа задания режима работы узла дешифрации, выходы элементов равнозначности первой и второй групп подключены к первым входам мажоритарных элементов каждой из групп, формируя конституенты единиц с нулевого по (2" — 1)-й наборы, вторые входы первых мажоритарных элементов всех групп подключены к третьему разряду входа задания режима работы узла дешифрации, выход каждого мажоритарномажо рита рн ого элемента груп и ы, выходы последних мажоритарных элементов всех групп подключены к соответствующим разрядам информационного выхода узла дешифрации, третьи входы всех мажоритарных элементов всех групп подключены к четвертому разряду входа задания режима работы узла дешифрации, вход задания режима работы узла дешифрации первого уровня подключен к входу задания режима работы пирамидального дешифратора, первый и второй разряды входы задания режима работы узлов дешифрации всех уровней, начиная со второго, подключены соответственно к первому и второму разрядам входа задания режима работы пирамидального дешифратора, каждый 1-й разряд информационного выхода m-го узла дешифрации P-го уровня соединен с третьим разрядом входа зададания режима работы пирамидального дешифратора.

1727123

1727123

Аг

Ag

0g

Ug

У,у

Og

Составитель В.Гречнев

Редактор В.Фельдман Техред М.Моргентал Корректор O.Ципле

Заказ 1279 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР !13035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул,Гагарина, 101