Многофункциональный логический модуль

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 Н 03 К 19/094

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

1: 1, ; с ) ! - 4

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1 (21) 4822024/21 (22) 09;04.90 (46) 07.05.92, Бюл, Гч 17 (72) Л. Б. Авгуль, В. П. Супрун, В. В, Торбунов и Э. Г. Лазаревич (53) 621.374(988.8) (56) Авторское. свидетельство СССР

И 1637020, кл. Н 03 К 19/094, 1989. Авторское свидетельство СССР

N 1598161., кл. Н 03 K 19/094, 1990. (54) МНОГОФУНКЦИОНАЛЬНЫЙ ЛОГИЧЕСКИЙ МОДУЛЬ (57) Изобретение относится к импульсной технике и микроэлектронике и может быть использовано для реализации симметрических булевых функций четырех переменных, Цель изобретения — упрощение конструкции и повышение быстродействия многофункционального логического модуля. Цель достигается тем, что многофункциональный

Изобретение относится к импульсной технике и микроэлектронике и предназначено для реализации симметрических булевых функций (с,б.ф,) четырех переменных, Известен многофункциональный логический модуль, выполненный на МОП-транзисторах и содержащий три элемента НЕ, два элемента 2-2И-ЗИЛИ, элемент 2-2И2ИЛИ, элемент 2-3И-2ИЛИ, два элемента

ИЛИ, семь входных шин и одну выходную шину.

Недостатком модуля являются ограниченные функциональные возможности, поскольку он реализует с,б.ф., зависящие только от трех переменных.

Наиболее близким техническим решением к предлагаемому является многофункциональный логический модуль, „„. Ж „„1732462 А1 логический модуль, реализующий симметрические булевы функции четырех переменных, содержит выполненные на

МОП-транзисторах два элемента НЕ, четыре элемента 2-2ИЛИ-ЗИ, два элемента 2-.

2ИЛИ-4И, элемент ИЛИ вЂ” НЕ, элемент

ИСКЛ ЮЧАЮ ЩЕ Е ИЛИ, элемент 2-4ИЛИ2И, четыре информационные шины, пять настроечных шин и выходную шину, Сложность модуля по числу МОП-транзисторов составляет 59, Многофункциональный логический модуль работает следующим образом. На информационные шины подаются двоичные переменные х1, xz. хз, х4, на настроечные шины — сигналы настройки Up.

0), U2, 0з, U4, значения которых принадлежат множеству (0,1). На выходной шине реализуется симметрическая.булева функции

F=F(x>, xz, хз, х4), огределяемая вектором настРойки U=(Up, 131, 02. ОЗ, U4). 1 табл., 7 ил, содержащий выполненные на МОП-транзисторах и (и — число переменных реализуемых булевых функций) линеек логических ячеек, каждая из которых содержит элемент

СЛОЖЕНИЕ ПО МОДУЛЮ ДВА и элемент

И.

Недостатком известного многофункционального логического модуля является высокая сложность (по числу

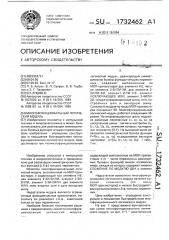

МОП-транзисторов) и низкое быстродействие при вычислении с.б.ф. четырех переменных, Цель изобретения — упрощение конст-! рукции и повышение быстродействия мно- гофункционального логического модуля, На фиг, 1 представлена функциональная. схема многофункционального логического модуля; на фиг. 2 — 7 — электрические

1732462 принципиальные схемы, выполненные на

МОЙ-транзисторах элементов 2-2ИЛИ-ЗИ, 2-2ИЛИ-4И, НЕ, 2-4ИЛИ-2И, ИСКЛЮЧАЮЩŠ— ИЛИ и ИЛИ-НЕ соответственно.

Многофункциональный логический модуль (фиг, 1} содер>кит выполненные на

МОП-транзисторах два элемента НЕ 1 и 2, четыре элемента 2-2ИЛИ-ЗИ 3-6, два элемента 2-2ИЛИ-4И 7 и 8, элемент ИЛИ вЂ” НЕ 9, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 10, элемент 2-4ИЛ И -2 И 11, четы ре ин форма ционные шины 12 — 15, пять настроечных шин

16 — 20, выходную шину 21.

Элемент 2-2ИЛИ-ЗИ (фиг. 2) собран из пяти переключательных 22-26 и одном нагрузочном 27 МОП-транзисторах, включенных между шинами питания 28 и 29, к-я (k=1,2,3,4,5) входная шина 29+k элемента соединена с затвором транзистора 21+k, выходная шина 35 элемента соединена со стоком транзистора 27 (истоками транзисторов 23 и 25).

Элемент 2-2ИЛИ-4И (фи-. 3) собран на шести переключательных 36 — 41 и одном нагрузочном 42 транзисторах, включенных между шинами питания 43 и 44, l-я (1=1,2,...,6) входная шина 44+! элемента сое.динена с затвором транзистора 35+I, выходная шина 51 элемента соединена со стоком транзистора 42 (истоками транзисторов 37 и 39).

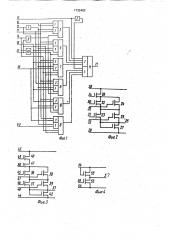

Элемент НЕ (фиг. 4) собран на одном переключательном 52 и одном нагрузочном

53 транзисторах, включенных между шинами 54 и 55 питания входная шина 56 элемента соединена с затвором транзистора 52, выходная шина 57 элемента соединена со стоком транзистора 52 (истоком транзистора 53), Элемент 2-4ИЛИ-2И (фиг. 5) собран на восьми переключательных 58 — 65 и одном нагрузочном 66 транзисторах, включенных между шинами 67 и 68 питания, s-я (э=1, 2,.„,8) входная шина 68+s элемента соединена с затвором транзистора 57+s, выходная шина 77 элемента соединена со стоком транзистора 66 (истоками транзисторов 59, 61, 63 и 65), Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ (фиг. 6) собран из трех переключательных 78 — 80 и двух нагрузочных 81 и 82 транзисторах, включенных между шинами 83 и 84 питания, первая 85 и вторая 86 входные шины элемента соединены соответственно с затворами транзисторов 85 и 86, выходная шина 87 элемента соединена со стоком транзистора

82 (истоком транзистора 79), Элемент ИЛИ-НЕ (фиг. 7) собран на двух переключательных 88 и 89 и одном нагрузочном 90 транзисторах, включенных между шинами 91 и 92 питания, первая 93 и вторая 94 входные шины элемента соединены соответственно с затворами транзисторов 88 и 89, выходная шина 95 элемента

5 соединена со стоками транзисторов 88 и 89 (с истоком транзистора 90), 10

Многофункциональный логический модуль работает. следующим образом, На информационные шины 12-15 подаются двоичные переменные х1, х2, х3. х4 (в произвольном порядке), на настроечные шины 16 — 20- сигналы настройки UO, 01, V2, U3 и U4 соответственно, значения которых принадлежат множеству (0,1). На выходной шине 21 реализуется значение с.б,ф. F=F(x1, х2, х3, х4) на данном наборе значений переменных, которая определяется вектором настройки U=(UO,U1,U2,U4), В таблице представлены значения сигналов настройки и соответствующие им двоичные номера (таблицы истинности) реализуемых модулем с.б.ф. четырех переменных, Достоиством модуля являются простая конструкция и высокое. быстродействие.

Так, для построения модуля необходимо 59

МОП-транзисторов (как это следует из фиг.

1-7). в то время как прототип при n=4 требует для своей реализации 80 МОП-транзисторов. Быстродействие модуля определяется в основном задержкой распространения сигналов через три уровня логических элементов, а быстродействие прототипа (при

n=4) определяется задержкой восьми уровней логических элементов, Указанные преимущества приведут к высокой технико-экономической эффективности при реализации модуля современными интегральными технологиями, Формула изобретения

Многофункциональный логический модуль, выполненный на Moil-транзисторах и содержащий элемент ИСКЛЮЧАЮЩЕЕ

ИЛИ, отличающийся тем, что, с целью упрощения и повышения быстродействия, содержит элемент ИЛИ вЂ” HE, элемент 24ИЛИ-2И, два элемента 2-2ИЛИ-4И, четыре элемента 2-2ИЛИ-ЗИ и два элемента НЕ, входная шина первого из которых соединена с первой информационной шиной модуля, первой входной шиной i-го (i=1,2,3,4) элемента 2-2ИЛИ-ЗИ и первой входной шиной j-ro (/=1,2) элемента 2-2ИЛИ-4И, а выходная шина соединена с второй входной шиной i-го элемента 2-2ИЛИ-ЗИ и второй входной шиной j-ro элемента 2-2ИЛИ-4И, первая настроечная шина модуля соединена с третьей входной шиной первого элемента 2-2ИЛИ-ЗИ, четвертая входная шина

1732462 которого соединена с второй настроечной шиной модуля. третьей входной шиной.второго элемента 2-2ИЛИ-ЗИ и третьей входной шиной третьего элемента 2-2ИЛИ-ЗИ, четвертая входная шина которого соединена с третьей настроечной шиной модуля. четвертой входной шиной второго элемента

2-2ИЛИ-ЗИ, третьей входной шиной четвертого элемента 2-2 ИЛ И-ЗИ и третьей входной шиной первого элемента 2-2ИЛИ-4И, четвертая входная шина которого соединена с четвертой настроечной шиной модуля. чет5

10 вертай входной шиной четвертого элемента

2-2ИЛИ-ЗИ и третьей входной шиной второго элемента 2-2ИЛИ-4И, четвертая входная шина которого соединена с пятой настроечной шиной модуля. (j+1)-я информационная шина которого соединена с (j+4)-й входной шиной j-го элемента 2-2ИЛИ-4И, j-й входной

16

17 18

U1 U2

2 3.

F(X1,Х2,Х3,Х4) О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

О

1

1

1

1

1

1

1 .1

О

О

О

О

О

О

О

О

1

1

1

1

О

О

О

О

О

О

О

О

1

1

1

О

О

О

О

1

1

О

О

О

О

1

О

О

О

О

1

1

О

О

О

О

1

О

О

1

О

О

l

О

О

1

О

О

1 .О

О

1

О

О

1

О

1

О

О

1

О

О

О

О

О

О

О

О

0

1 шиной элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и

j-й входной шиной элемента ИЛИ-НЕ, выходная шина которого соединена с пятой входной шиной (2j 1j-.ãî элемента 2-2ИЛИЗИ, выходная шина которого соединена c j-й входной шиной элемента 2-4ИЛИ-2И, +2 -я входная шина которого соединена с выходной шиной j-ro элемента 2-2ИЛИ-4И, пятая входная шина соединена с четвертой информационной шиной модуля и входной шиной второго элемента НЕ, выходная шина которого соединена с шестой входной шиной элемента 2-4ИЛИ-2И. выходная шина которого соединена с выходной ыинОЙ модуля, а егоЯ+6 -я входная мвна соединена с выходной шиной 2j-го злемеита 2-2ИЛИ-ЗИ.. пятая входная шина которого соединена с выходной шиной элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, 0Î000GG0060000O0

000000O0000O00G1

00000001000i013.1

00010110013.01000

0001011901101901

0001011101111111

01103.00010000000

0110100010000901

01101001160i0116

01101001100103.11

011113.103.1101000

0l11111011i01001

011111111ililll0

01111111113.i1lli

1000000000000001

10000001000103.10

1000000100010111

100101100i101001

1001011101111111

11101000l0000000 .

1110100010000001

1110100110010111

11111110l1101001

1111111111111111

1732462

4ÜÃ Ð

1732462

72

7ф

7б

Ю

Я

92

Фиг. 7

Составитель В. Супрун

Редактор С. Пекарь Техред М.Моргентал Корректор Ч, Максимишинец

Заказ 1589 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", r. Ужгород. уп.Гагарина. 101