Устройство для перемножения матриц

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных машинах и устройствах обработки данных. Целью изобретения является сокращение аппаратурных затрат. Устройство содержит первый, второй и третий информационные входы 1, 2, 3, вход 4 синхронизации, с первого по третий входы 5, 6, 7 режима управления , вход 8 опроса, вычислительные блоки 9, информационный выход 10, выход 11 опроса. 3 ил., 2 табл.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я>5 6 06 F 15/347, 11/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

М

C (л)

Ф О фь (21) 4823752/24 (22) 07.05.90 (46) 15.05.92. Бюл, ¹ 18 (72) М.M.Òàòóð, С.П.Яцкевич, В.П.Якуш и

Н.B.ÔóðàøoB (53) 681.325(088.8) (56) Киносита К„Асада К„Карацу О. Логическое проектирование.СБИС. M„Мир, 1988.

Авторское свидетельство СССР

N 1536399, кл, G 06 F 11/00, 15/347, 1985. (54) УСТРОЙСТВО ДЛЯ ПЕРЕМНОЖЕНИЯ

МАТРИЦ

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных машинах и устройствах обработки данных.

Известно устройство с линейной структурой для перемножения двух (n х n) матриц, содержащее 3n — 2 вычислительных блоков (ВБ), причем ВБ содержит три входных регистра и один выходной узел задержки, сумматор и умножитель.

Недостатком этого устройства является отсутствие системы тестового диагностирования.

Наиболее близким по технической сущности к предлагаемому является устройство для перемножения матриц (и х n), структура которого обеспечивает автономную проверку работоспособности.

Устройство имеет п2 ВБ, каждый из которых содержит три регистра с обратной связью, сумматор, умножитель, элемент памяти и схему сравнения.

Н.едостатками устройства являются сложность ВБ, наличие четырех дополнительных шин ввода-вывода. а > Жоо 1734104 А1 (57) Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных машинах и устройствах обработки данных.

Целью изобретения является сокращение аппаратурных затрат, Устройство содержит первый, второй и третий иНформационные входы 1, 2, 3, вход 4 синхронизации, с первого по третий входы 5, 6, 7 режима управления, вход 8 опроса, вычислительные блоки 9, информационный выход 10, выход

11 опроса. 3 ил., 2 табл.

Цель изобретения — сокращение аппаратурн ых затрат.

Поставленная цель достигается тем, что устройство, содержащее линейную структуру Зп — 2 ВБ, каждый из которых содержит четыре регистра, умножитель, сумматор, узел задержки, три информационных входа и три информационных выхода, вход синхронизации, соединенный со всеми ВБ, дополнительно содержит в каждом ВБ два входа управления и два вывода (вход и выход) опроса, входы управления соединены с входными регистрами, которые соединены в узел сдвига с обратными связями, вход и выход которого являются входом и выходом опроса и соединены с соответствующими выводами ВБ, первые входы управления всех ВБ соединены в первый вход режима управления устройством, вторые входы управления нечетных номеров ВБ — во второй вход режима управления устройством, вторые входы четных номеров ВБ — в третий вход режима управления устройством, все узлы сдвига входами и выходами опроса последовательно соединены в единый регистр

1734104 сдвига с входом и выходом опроса устройства.

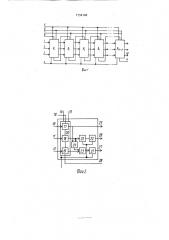

На фиг. 1 представлена структурная схема устройства для перемножения двух матриц (и х n); на фиг. 2 — функциональная схема вычислительного блока; на фиг. 3— функциональная схема узла сдвига с обратными связями и управлением.

Устройство содержит первый 1, второй

2 и третий 3 информационные входы, вход 4 синхронизации, первый 5, второй 6 и третий

7 входы режима управления (pl,p p>), вход

8 опроса (D)), вычислительные блоки 9f (i =

=1, 3п-2); информационный выход 10, выход

11 опроса (Do).

Вычислительный блок 9 (фиг. 2) содержит первый 10, второй 1, третий 12 информационные входы, вход 13 синхронизации, входы 14 и 15 управления (U>, Щ, вход 16 опроса (dl), регистры 17, 18 и 19, образующие узел 20 сдвига, регистр 21, регистры 22 узла задержки, сумматор 23, умножитель

24, первый 25, второй 26, -ретий 27 информационные выходы, выход 28 опроса (dî).

Узел 20 сдвига с обратными связями содержит (фиг. 3) информационные входы

29, вход 30 синхронизации, входы 14 и 15 управления (Ul и Uz), вход 16 опроса (d>), группу 31 двухступенчатых D-триггеров, группу 32 элементов И вЂ” НЕ, группу 33 элементов И вЂ” НЕ, группу 34 элементов сложения fio модулю 2, элемент И вЂ” НЕ 35, сумматор 36 по модулю два, элемент 2ИИЛИ вЂ” НЕ 37, инверторы 38, информационные выходы 39, выход 28 опроса (do).

Узел 20 сдвига в зависимости от сигналов настроек на входах 0, Uz — 14, 15 и входе опроса d> 16 может работать в одном из четырех режимов.

Режимы работы регистра представлены в табл. 1, Устройство имеет два режима работы— основной и режим тестирования.

В основном режиме работы устройство реализует алгоритм перемножения двух(n х

»n) матриц, основанный на реккурентных соотношениях: с (=O,j, i 1, и;

+ а кЬ, l,),k = 1, fl; с ®=cfi, Ц =1, и.

Для установки основного режима работы на входы режима управления rp„p>„p>5, 6 и 7 подаются сигналы О, 1, 1, в результате чего все регистры устройства будут работать в режиме параллельного действия. В остальном работа устройства в основном режиме ничем не отличается от работы известного устройства.

Режим тестирования, 25

40

50

5

Тестирование устройства осуществляется в несколько этапов (см. табл. 2).

Синхронизация сдвига информации в режимах 1-, 3- и 5-м, а также синхронизация тестирования осуществляется по входу 4 синхронизации, Указанная процедура тестирования позволяет определить номер отказавшего ВБ по результату сравнения выводимых сигнатур. В случае проверки работоспособности устройства третий этап является необязательным, так как сигнатуры тестирования нечетных ВБ могут являться стартовым словосостоянием этапа тестирования четных

ВБ.

Таким образом, предложенное устройство по сравнению с устройством-прототипом не содержит в каждом ВБ схему сравнения, элемент памяти и четыре дополнительных шины данных. Дополнительным положительным эффектом является возможность локализации неисправности с точностью до ВБ.

Формула изобретения

Устройство для перемножения матриц, содержащее Зп — 2 вычислительных блоков, где flxfl - размерность перемножаемых матриц, при этом первый, второй и третий входы элементов матриц устройства подключены соответственно к первому, второму и третьему информационным входам первого вычислительного блока, первый, второй и третий выходы i-ro вычислительного блока (где i = 1,...,3п — 3) подключены соответственно к первому, второму и третьему информационным входам (i+1)-ro вычислительного блока, первый, второй и третий выходы (Зп — 2)-го вычислительного блока подключены соответственно к первому, второму и третьему выходам результата устройства, вход синхронизации которого подключен к входам синхронизации всех вычислительных блоков, причем каждый вычислительный блок содержит регистр, узел задержки, сумматор и умножитель, при этом в каждом вычислительном блоке выход узла задержки подключен к первому выходу вычислительного блока, вход синхронизации которого подключен к управляющему входу узла задержки и к входу записи-счи"тывания регистра, выход которого подключен к второму выходу вычислительного блока, выход умножителя подключен к первому информационному входу сумматора, выход которого подключен к информационному входу регистра, о т л и ч а ю щ е е с я тем, что, с целью сокращения аппаратурных затрат, первый вход режима устройства подключен к первым управляющим входам

1734104

Таблица 1

Таблица 2

30 всех вычислительных блоков, второй вход режима устройства подключен к вторым управляющим входам 2k-х вычислительных блоков (где k = 1,...,m,m (3n — 2)!2), третий вход режима устройства подключен к вто- 5 рым управляющим входам (2k+1)-х вычислительных блоков, четвертый вход режима устройства подключен к входу опроса первого вычислительного блока, четвертый выход i-го вычислительного блока подключен к 10 входу опроса (i+1)-ro вычислительного блока, четвертый выход (3n — 2)-ro вычислительного блока подключен к выходу признака опроса устройства, при этом каждый вычислительный блок соде зжит узел сдвига, при- 15 чем в каждом вычислительном блоке первый, второй и третий информационные входы, вход синхронизации, первый и второй управляющие входы и вход опроса вычислительного блока подключены соответственно к первому, второму и третьему информационным входам, к входу синхронизации, к первому и второму входам режима и четвертому информационному входам узла сдвига, первый информационный выход которого подключен к третьему выходу вычислительного блока и к первому информационному узлу умножителя, второй информационный выход узла сдвига подключен к информационному входу узла задержки и к второму информационному входу умножителя, третий информационный выход переноса вычислительного блока подключен к - второму информационному входу сумматора и четвертому выходу вычислительного блока, 1734104

1734104

Составитель М.Татур

Редактор Л.Веселовская Техред М.Моргентал Корректор Т,Малец

Заказ 1671 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб„4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101