Устройство для мажоритарного декодирования

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при построении устройств для передачи и обработки информации. Цель изобретения - расширение класса решаемых задач, области применения за счет возможности декодирования циклических кодов с разным числом проверочных соотношений. Устройство содержит блок 1 управления, п элементов 2 памяти (по числу информационных символов входного кода), п мажоритарных элементов 3, каждый из которых содержит ег своем составе регистр 4 числа и анализатор 5 символов. Введение в устройство новых функциональных элементов и образование новых связей, а такжетфедложенная схема блока 1 управления обеспечивает возможность декодирования устройством циклических кодов с разным числом т, декодирования кодовых последовательностей , переданных методом дублирования, что обеспечивает достижение поставленной цели. 1 з.п., 3 ил.

COIG3 СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5!)5 Н 03 М 13/00

ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕ

ВЕДОМСТВО СССР (ГОСПАТЕНТ СССР) K АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4824726/24 (22) 14.05.90 (46) 23,12.92. Би)л. N 47 (71) Производственное объединение "ИжевcKItIIA мотозавод (72) Е.A,Øóðìóõèí (56) Авторское свидетельство СССР

N 607349, кл. Н 04 L 1/10 1975.

Авторское свидетельство СССР

N. 1436276, кл, Н 03 М 13/10, 1987. (54) УСТРОЙСТВО ДЛЯ МАЖОРИТАРНОГО

ДЕКОДИРОВАНИЙ (57) Изобретение относится к вычислительной технике и может быть использовано при построении устройств для передачи и обработки информации. Цель изобретения — расширение класса решаемых задач, области

„„ИУ„„1783624 А1 применения за счет возможностй декодирования циклических кодов с разным: числом проверочных соотношений. Устройство со= держит блок 1 управления, и элементов 2 памяти (по числу информационных символов входното кода), и мажоритарных элементов 3, каждый из которых содержит в своем составе регистр 4 числа и анализатор

5 символов. Введение в устройство новых функциональных элементов и образование новых связей, а также предложенная схема блока 1 управления обеспечивает возможность декодирования устройством циклических кодов с разным числом m, декодирования кодовых последовательностей, переданных методом дублирования, что обеспечивает достижение поставленной цели. 1 з.п., 3 ил.

1783624

25

40

Изобретение относится к вычислительной технике и может быть использовано при построении устройств для передачи и обработки информации.

Известно устройство для мажоритарного декодирования, содержащее регистр сдвига, который одновременно является и буферным регистром памяти поступающих разрядов, вход регистра является входом устройства, а разрядные выходы соединены с первыми входами группы элементов "И", предназначенных для подключения выходов регистра сдвига к первым входам блока сумматоров. Вторые входы группы элементов "И" соединены с входами блока управления, формирующего серию командных импульсов. Вторые входы блока сумматоров соединены с выходом первого триггера регистра сдвига, выходы блока сумматоров соединены с первыми входами схемы "И" узла оцейки результатов контрольных проверок блока мажоритарных элементов, вторые входы которых соединены со второй группой выходов блока управления, а выходы которых через элемент ИЛИ подключены к счетным входам двоичных счетчиков, охваченных цепью обратной связи.

Недостатком устройства является большой объем оборудования, обусловленный сложностью блока управления и наличием двух ступеней — коммутации. Кроме того, структура построения мажоритарного элемента в устройстве не обеспечивает возможность декодирования кодов с разным числом m (m — число проверочных c00THQUJBний для примененного кода), декодирования кодовой последовательности при пятикратном повторении комбинации, Наиболее близким техническим решением к предлагаемому является устройство для мажоритарного декодирования, содержащее п мажоритарных элементов (и — число информационных символов входного кода), управляющие входы которых объединены с установочным входом блока управления и являются входом "Пуск" устройства, первый и второй управляющие выходы блока управления подключены соответственно к первым и вторым управляющим входам элементов памяти, тактовый вход блока управления является тактовым входом устройства, выходы мажоритарных элементов являются соответствующими вь ходами устройства. Решающий блок, выходы которого подключены к информационным входам соответствующих мажоритарных элементов, третий управляющий выход блока управления соединен с управляющим входом решающего блока, информационный вход которого объединен с информационными входами элементов памяти и является информационным входом устройства, адресные выходы блока управления соединены с одноименными первыми адресными входами решающего блока и соответствующими адресными входами, элементов памяти; Bblходы которых подключены к соответствующим вторым адресным входам решающего блока.

Недостатком устройства является ограниченный класс решаемых задач, например, отсутствие возможности декодирования кодов с разным числом m, отсутствие возможности декодирования кодовой последовательности при пят: кратном повторении комбинации, что обусловлено наличием решающего блока и структурой построения мажоритарного элемента, что приводит к ограничению области применения устройства.

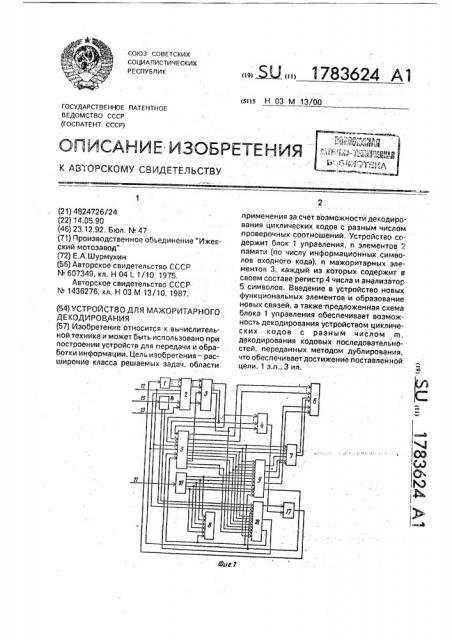

Целью предполагаемого изобретения является расширение области применения устройства за счет возможности декодирования циклических кодов с разным числом проверочных соотношений, На фиг. 1 представлена структурная схема предложенного устройства; на фиг. 2 —. схема блока управления; на фиг. 3 — временные соотношения входных сигналов и импульсов управления.

Устройство мажоритарного декодиро- вания содержит блока 1 управления, и элементов 2 памяти, и мажоритарных элементов 3, каждый из которых содержит в своем составе регистр 4 числа и анализатор

5 символа. К информационному входу 6 устройства подключены информационные входы анализаторов 5 символов, Тактовый вход

7 устройства соединен с тактовым входом блока 1 управления, установочный вход которого является входом "Пуск" 8устройства, управляющий вход 9 устройства подключен к управляющему входу блока 1 управления и управляющим входам анализаторов 5 символа, Выходы мажоритарных элементов, подключенные к первым выходам соответствующих анализаторов символов, являются выходами 10 устройства, Информационные выходы элементов 2 памяти подключены ко вторым входам анализаторов 5 символов, выходы регистров 4 подключены к третьим входам соответствующих анализаторов символов, выходы которых соединены с информационными входами регистров 4 числа.

Блок 1 управления может быть выполнен по схеме, приведенной на фиг. 2, и содержит в своем составе триггер 11, регистр

12, дешифратор 13, первый элемент 14 И, 1783624 элемент 15 задержки, второй 16, третий 17 и — сбросовый сигнал на выходе третьеэлементы И, ro элемента И 17 и на выходе 21 блока;

Первый управляющий выход 18 блока 1 к — сигналы на выходе 20 блока 1; управления подключен ко второму выходу л — сигнал на первом управляющем выдешифратора 13 и соединен с первыми уп- 5 ходе 18 блока 1 управления. равляющими входами элементов памяти, Устройство работает в двух режимах: в второй выход элемента задержки 15, являю- режиме декодирования циклических кодов щийся вторым управляющим выходом 19 и в режиме декодироваййя"кбдовь1х послеблока 1 управления соединен с первым вхо- довательностей, переданных методом дубдом второго элемента 16 И и со вторыми 10 лирования. управляющими входами элементов памяти, В режиме декодирования циклических а третий управляющий выход 20 блока 1 кодов устройство декодирует циклические управления, подключенный к первому выхо- коды, образующиеся путем умножения по ду дешифратора 13 и информационному модулю два двоичного кода длиной п {инвходурегистра12,соединен суправляющи- 15 формационная часть) на циклическую поми входами регистров 4 числа, выход треть- следовательность, постоянйую для"данного его элемента 17 И, являющийся сбросовым . кода, которая содержит все возможные пвыходом21 блока1 управления соединен со членные комбинации. сбросовыми входами соответствующих ре- В результате умножения образуется гистров 4 числа мажоритарных элементов, 20 замкнутая последовательность символов, первый выход элемента 15 задержки, явля- построенная так, что число элементов в ней ющийся тактовым выходом 22 блока 1 уп- равно числу неповторимых и-членных комравления, соединен с тактовыми входами бинаций, которые образованы отрезками регистров 4 числа, адресный выход 23 блока данной последовательности.

1 управления, соединенный с выходом реги- 25 В данных кодах слева направо располастра 12 и вторым входом дешифратора 13, гаются информационные символы, за ними соединен с адресными входами элементов — контрольные символы, длйна кода (n + К), где n — число информационных символов, К

Установочный вход 8 блока 1 управле- — число контрольных символов кода. ния подключен к установочным входам триг- 30 Декодирование осуществляется извест. " гера 11 третьего элемента 17 И, второй вход ным способом по принципу голосования которого соединен с четвертым выходом де- (мажоритарное декодирование) с использо- . шифратора 13, Второй вход триггера 11 со- ванием системы раздельных проверок. единен с выходом второго элемента 16 И, Устройство декодирует два вида кодов, второй вход которого подключен к третьему 35 код 31.5.7 с числом m = 16 и код 15.4.3 с выходу дешифратора 13. Тактовый вход 7 числом m = 8. блока управления 1 подключен ко второму Выбор декодируемого кода осуществлявходу первого элемента 14 И, к первому ется подачей соответствующегопотенциала входу которого подключены выход триггера по входу 9 устройства на третий вход де-, 11 и сбросовый вход регистра 12, вь|ход .40 шифратора 13 блока 1 управления и на четэлемента 14 И соединен с первым входом вертый вход анализатора 5 символов. дешифратора 13 и входом элемента задер- Процесс декодирования начинается"с жки 15, третий выход которого подключен к приходом на вход 8 устройства импульса тактовому входу регистра 12, а управляю- начала преобразования (фиг. Зв), который щий вход блока Iуправления подключен к 45 соответствует началу кодовой посылки,,Имтретьему входу дешифратора 13, пульс начала преобразования, поступая на

На фиг. 1,2 обозначены управляющий установочный вход блока 1 управления чевыходы 18-20, сбросовый выход 21, такто- рез нормально открытую в данном режиме вый выход 22, адресные выходы 23.: схему И 17 блока 1 управления, устанавливаНа фиг. 3 обозначены: 50 ет в нулевое состояние регистрй 4 мажориа — импульсы входного кода на входе; тарных элементов, "а триггер 11 блока 1 б — тактовые импульсы на входе 7; управления устанавливает в положение, в — сигнал "Пуск" на входе 8; разрешающее прохождение меандра тактог-е-импульсы на первом-третьем выхо- вой частоты через элемент И 14 и работу дах элемента 15 задержки блока 1; 55 регистра 12 блока 1 управления. ж — сигналы на выходах регистра 12 Импульсы тактовой частоты с выхода блока 1 и на выходе 22 блока 1; элемента И 14 поступают на первый адреса — сигнал на выходе элемента И 16 ный входдешифратора 13 и на входэлеменблока 1; та 15 задержки, который формирует на

1783624 своих выходах импульсы в соответствии с (см. фиг. Зг-3e).

Дешифратор 13 блока 1 управления на своем втором выходе формирует стробы выборки (ВК) элементов 2 памяти, которые с выхода 18 блока 1 управления поступают на первые управляющие входы элементов 2 памяти, разрешая их работу. С выхода регистра 12 информация по выходу 23 блока 1 управления поступает на адресные входы элементов 2 памяти. В регистре 12 формируется соответствующий код, содержащий признаки наличия информационных символов, которые на данный момент присутствуют в разряде последовательного кода, при этом адресными сигналами для элемента 2

ai информационного символа являются выходные разряды регистра 12 блока 1 управления, кроме разряда, содержащего признак наличия в слагаемом символа аь

С второго выхода элемента 15 задержки импульсы (см. фиг. Зд) признака операций

"Запись", "Чтение" (отрицательный потенциал — "Чтение", положительный потенциал

"Запись" ) через выход 19 блока 1 управления поступают на вторые управляющие входы элементов 2 памяти. Таким образом, при наличии отрицательного потенциала на втором управляющем входе элементов 2 памяти в течение времени следования с инхро кода элементы 2 памяти уста на вл иваются в режиме "Чтение" и тем самым обеспечивают подключение ко вторым информационным входам анализаторов 5 символов первых слагаемых, а вторые слагаемые (входной код) поступают на первые информационные входы анализаторов

5 символов со входа 6 устройства. Некото. рые особенности имеют случай декодирования последовательности (и + К) символов, представляющих информационные символы, которые не имеют второго слагаемого, B этом случае дешифратор 13 на своем втором выходе в первом полупериоде тактового интервала формирует запрещающий потенциал (см. фиг. Зл). Элементы 2 памяти закрыты и тем самым на их выходе находится нулевая информация.

Анализатор 5 символа производит сложение по модулю два поверочных символов, суммирование результата сложения с кодом предыдуЩих значений, поступающих на его третий вход с выхода регистра 4. Результат суммирования со второго выхода анэлизатора 5 поступает на первый вход регистра 4 для последующей записи его в регистр 4, Кроме того, анализатор 5 производит методом голосования по большинству анализ суммы результатов сложения, поступающей на его третий вход с выхода регистра

4 числа нэ предмет принятия решения о значении информационного символа. Результат анализа в каждом такте с первого выхода анализатора 5 символа поступает на выход устройства.

В момент наличия на информационных входах ni анализатора символа 5 обоих слагаемых в первом полупериоде тактового интервала на первом выходе дешифратора 13 и четвертом выходе блока 1 управления формируются стробы (cM. фиг. Зк) управления мажоритарными элементами 3, распределение которых определяется наличием в входном сигнале символа, входящего в уравнение поверки информационного символа, соответствующего конкретному элементу 3.. Стробы управления, поступающие на управляющий вход регистров 4 числа с третьего выхода 20 блока 1 управления переводят соответствующий и регистр 4 из режима "Хранение" в режим параллельного ввода. Задним фронтом импульса (см. фиг.

Зг), поступающего на тактовый вход регистра 4 с выхода 22 блока 1 управления результат суммирования анализатора 5. записывается в регистр 4, Положительным импульсом с второго выхода элемента 15 задержки блока 1 управления производится запись в элементы.

2 памяти входного сигнала по адресам данного такта. Во втором полупериоде тактового интервала дешифратор 13 блока 1 управления на своем втором выходе формирует код адреса следующего такта. После проведения операции "Запись" задним фронтом импульс," (см, фиг. Зе) значение кода дешифратора 13 записывается в регистр 12, Таким образом, регистр 12 подготовлен для работы в следующем такте, В следующем такте цикл повторяется. Дешифратор 13 блока 1 управления вырабатывает (n + К) адресов обращения к элементам 2 памяти. По окончании цикла декодирования (и + К) тактов в блоке 1 управления на дешифраторе 13 выделяется признак конца цикла декодирования, который после опроса на элементе И 16 импульсом со второго выхода элемента 15 задержки производит установку триггера 11 блокэ 1 управления в исходное состояние, а триггер 11 устанавливает регистр 12 в состояние, необходимое для работы в первом такте.

B режиме декодирования кодовых последовательностей, переданных методом дублирования, поступающий двухразрядный код управления со входа 9 устройства на третий вход дешифратора 13 и на четвертые входы анализаторов 5 переключает их в режиме декодирования дублирующих сообщений. Процесс декодирования также как и

1783624

5

30

55 в режиме декодирования циклических кодов начинается с приходом на вход 8 импульса начала преобразования (см. фиг. Зв), который соответствует началу кодовой посылки. Фазировка регистров 4 мажоритарных элементов импульсом начала преобразования не производится, т.к, схема 17 И в данном режиме закрыта потенциалом с четвертого выхода дешифратора 13.

Импульс начала преобразования поступает на установочный вход блока 1 управления и устанавливает триггер 11 управления в пол жение, разрешающее прохождение меандра тактовой частоты через элемент И

14 и разрешает работу регистра 12. Импульсы тактовой частоты с выхода элемента И 14 поступают на первый адресный вход.дешифратора 13 и на вход элемента 15 задержки, который формирует на третьем выходе импульсы ввода (см, фиг, 3e) в регистр 12, Регистр 12 в этом случае работает в режиме двоичного счета тактовых импульсов. Дешифратор 13 на своем первом выходе во втором полупериоде тактового интервала формирует двоичный код, который задним фронтом импульса (см. фиг. Зе) заносится в регистр 12, На втором управляющем выходе дешифратора 13 формируется запрещающий потенциал, который с первого управляющего выхода 18 блока 1 управления поступает на первый управляющий вход элементов 2 памяти, запрещая их работу и таким образом с выходов элементов 2 памяти на второй информац. Вход анализатора 5 поступает нулевое значение информации.

На третьем выходе дешифратора 13 в момент наличия на первых информационных входах ni анализатора 5 символа 1-го декодируемого символа в первом полупериоде тактового интервала формируются стробы (см. фиг. Зк}, которые поступают на управляющий вход регистра 4 числа с третьего выхода 20 блока 1 управления. Данные стробы переводят соответствующий и; регистр 4 из режима "Хранения" в режим параллельного ввода, Анализатор 5 символов в этом режиме обеспечивает работу регистров 4 числа в режиме сдвигающего регистра и производит принятие решения о значении декодируемого разряда путем анализа информации, поступающей на его 3-й вход с выхода регистра 4 числа методом голосования по большинству. . Задним фронтом импульса (см. фиг, Зг), поступающего на тактовый вход регистра 4 с тактового выхода 22 блока 1 управления содержимое регистра 4 числа сдвигается на один разряд вправо, причем в первый разряд регистра 4 записывается значение разряда с первого информационного входа анализатора 5, в 2-й ... 5-й разряды с 1-го „„4-го разрядов 1 регистра 4 соответственно. В первом такте производится обработка первого разряда входного кода, во втором такте второго разряда и так далее. После обработки последнего ni разряда дублирующей посылки на дешифраторе 13 выделяется признак конца цикла, который после опроса на элементе И 16 импульсом со второго выхода элемента 15 задержки производит установку триггера 11 блока 11 управления в исходное состояние.

Следующая дублирующая посылка обрабатывается аналогично и таким образом в

ni мажоритарном элементе будут записаны значения i-го разряда всех дублирующих посылок.

Анализатор 5 символа методом голосования по большинству принимает решение о значении декодируемого символа. Результат выхода анализатора 5 символа поступает на выход устройства, Таким образом, введение в известное устройство новых функциональных элементов и связей позволяет расширить область применения устройства в сравнении с прототипом в части обеспечения возможности декодирования циклических кодов с разным числом m, декодирования кодовых последовательностей, переданных методом дублирования.

Формула изобретения

1. Устройство для мажоритарного декодирования, содержащее блок управления, тактовый и установочный входы которого являются соответственно тактовым входом и входом "Пуск" устройства, первый и второй управляющие выходы блока управления соединены с одноименными управляющими входами и элементов памяти (n — число информационных символов входного кода), информационные входы которых объединены и являются информационным входом устройства, адресный выход блока управления соединен с адресными Входами элементов памяти, п мажоритарных элементов, Выходы KGTopblx являются Выходами устройства,отл ичаю щееся тем, что,с целью расширения области применения устройства за счет обеспечения возможности декодирования циклических кодов с разным числом проверочных соотношений, в устройстве каждый мажоритарный элемент выполнен на анализаторе символа и регистре числа, выход которого соединен с первым информационным входом анализатора символа, первый выход которого соединен с

1783624

12 информационным входом регистра числа, выход каждого элемента памяти соединен с вторым информационным входом одноименного анализатора символа, третий информационный вход которого подключен к информационному входу устройства. управляющие входы блока управления и анализаторов символов объединены и являются управляющими входом устройства, вторые выходы анализаторов символов являются выходами мажоритарных элементов, третий управляющий выход блока управления соединен с управляющими входами соответствующих регистров числа, тактовый выход и выход сброса блока управления соединены соответственно с тактовыми входами и входами. сброса регистров числа. 2. Устройство по и. 1, о т л и ч а ю щ е ес я тем, что блок управления выполнен на триггере, регистре, дешифраторе, элементе задержки и элементах И, выход триггера соединен с первыми входами регистра и первого элемента И, выход которого соединен с первым входом дешифратора и входом элемента задержки, первый выход которого соединен с вторым входом регистра, выход регистра соединен с вторым входом дешифратора и является адресным выходом блока, второй выход элемента за5 держки соединен с первым входом второго элемента И и является вторым управляющим выходом блока, первый выход дешифратора является первым управляющим выходом блока, второй и,третий выходы де10 шифратора соединены соответственно с первым входом третьего элемента И и вторым входом второго элемента И, выход которого соединен с первым входом три гера, второй вход которого объединен с вторым

15 входом третьего элемента И и является установочным входом блока, четвертый выход дешифратора соединен с вторым входом регистра и являетСя третьим управляющим выходом блока, третий вход дешифратора и

20 второй вход первого элемента И являются соответственно управляющим и тактовым входами блока, третий выход элемента задержки и выход третьего элемента И являются соответственно тактовым выходом и

25 выходом сброса блока.

1783624

13 гУ So y с о

Составитель Е.Шурмухин

Редактор Г.Бельская Техред M.Mîðãåíòàë Корректор Л,Лукач

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

Заказ 4522 Тираж Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5