Анализатор параметрических отказов и сбоев

Иллюстрации

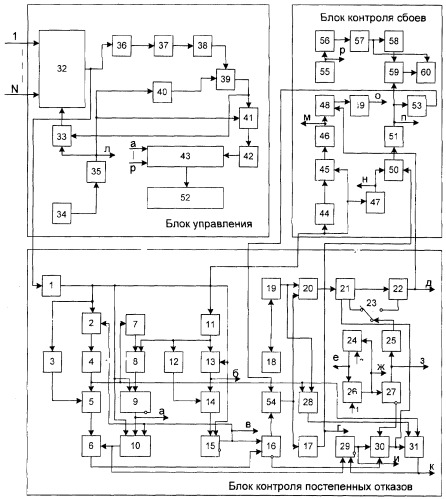

Показать всеИзобретение относится к контрольно-измерительной технике и может быть использовано при проектировании, производстве, испытаниях и эксплуатации радиоэлектронных изделий (РЭИ). Техническим результатом является расширение класса решаемых задач и повышение достоверности результатов анализа за счет введения контроля моментов возникновения сбоев и их длительности, псевдопараллельной обработки контролируемых параметров. Указанный результат достигается за счет того, что анализатор отказов содержит блок контроля постепенных отказов, блок контроля сбоев, содержащий делитель частоты, счетчики импульсов, вычитатели, элемент ИЛИ, табло отображения и блок управления, содержащий селектор данных, счетчик импульсов по модулю N, генератор тактовых импульсов, элементы задержки, блок ячеек памяти, элементы И, элементы ИЛИ. 1 ил.

Реферат

Изобретение относится к контрольно-измерительной технике и может быть использовано при проектировании, производстве, испытаниях и эксплуатации радиоэлектронных изделий (РЭИ). Техническим результатом является расширение класса решаемых задач и повышение достоверности результатов анализа за счет введения контроля моментов возникновения сбоев и их длительности, псевдопараллельной обработки контролируемых параметров.

Существуют устройства, предназначенные для определения и анализа отказов [1-3]. Основным недостатком данных устройств является их неприменимость в современных условиях для контроля микропроцессорной техники, в которой наряду с отказами возникает большое число сбоев [5]. Также все они предназначены для контроля одного электронного изделия.

Устройство-прототип содержит пороговый блок, формирователи импульса, элементы задержки, элементы И, элементы ИЛИ, дифференцирующий элемент, триггеры, инверторы, формирователи паузы, счетчики импульсов, переключатель, регистр.

Недостатком данного устройства является то, что оно фиксирует только постепенные отказы и не учитывает сбои в работе и предназначено для контроля только одного электронного изделия. В случае, если контролируемое устройство восстанавливается после произошедшего отказа, устройство простаивает и не выполняет никаких функций. Поэтому использование данного устройства затруднено из-за того, что оно должно изготавливаться для каждого РЭИ. Кроме того, оно не может быть использовано для контроля современных РЭИ, которые включают в себя вычислительную технику, подверженную не только отказам, но и сбоям.

Анализатор отказов, содержащий первый пороговый блок, формирователь импульса, первый элемент задержки, первый инвертор, первый элемент И, второй элемент ИЛИ, дифференцирующий элемент, четвертый элемент И, первый триггер, третий элемент И, второй инвертор, второй элемент задержки, формирователь паузы, шестой элемент И, третий триггер, четвертый триггер, второй счетчик, генератор импульсов, делитель частоты, второй элемент И, первый элемент ИЛИ, первый счетчик, переключатель, регистр, пятый элемент И, третий счетчик, второй триггер, седьмой элемент И, пятый триггер, восьмой элемент И, четвертый счетчик, при этом вход порогового блока является информационным входом анализатора, а выход соединен с единичным входом третьего триггера, входом первого элемента задержки, нулевым входом первого триггера, третьим входом третьего элемента И, входом сброса формирователя пауз, входом второго инвертора и входом запуска формирователя импульса, выход которого соединен с входом первого инвертора, выход которого подключен к входу дифференцирующего элемента, первому входу седьмого элемента И, входу сброса четвертого счетчика и второму входу первого элемента И, первый вход которого соединен с выходом первого элемента задержки, а выход - со вторым входом второго элемента ИЛИ, выход которого подключен к единичному входу четвертого триггера, инверсный выход которого связан с третьим входом восьмого элемента И, а прямой выход соединен с первым входом пятого элемента ИЛИ, выход которого подключен к счетному входу второго счетчика и второму входу второго элемента И, выход которого соединен с первым входом первого элемента ИЛИ, выход которого подключен к суммирующему входу первого счетчика, выход генератора импульсов соединен с первым входом пятого элемента И и входом первого делителя частоты, выход которого - с первым входом второго элемента И и вторым входом седьмого элемента И, выход которого соединен с входом сложения четвертого счетчика, а его выход обнуления - с нулевым входом пятого триггера, единичный вход которого соединен с первым входом второго элемента ИЛИ и выходом третьего элемента И, второй вход которого, нулевой вход четвертого триггера и вход сброса формирователя импульса связаны с прямым выходом третьего триггера, нулевой вход которого подключен к выходу шестого элемента И, первый и второй входы которого подключены к выходам второго элемента задержки и формирователя паузы, первый вход третьего элемента И соединен с прямым выходом первого триггера, единичный вход которого подключен к выходу четвертого элемента И, первый вход которого связан с выходом дифференцирующего элемента, а второй вход четвертого элемента И, вход второго элемента задержки и вход запуска формирователя паузы соединены с выходом второго инвертора, первый и второй информационные выходы переключателя связаны с вторым входом первого элемента ИЛИ и входом вычитания первого счетчика, а информационный вход переключателя - с выходом пятого элемента И, третий вход первого элемента ИЛИ и вход вычитания четвертого счетчика соединены с выходом восьмого элемента И, первый вход которого подключен к прямому выходу пятого триггера, а второй вход - к инверсному выходу второго триггера, первый установочный вход третьего счетчика связан с выходом регистра, выход обнуления третьего счетчика - с входом считывания регистра и с нулевым входом второго триггера, а второй установочный вход третьего счетчика и вход записи регистра являются соответственно первым и вторым установочными входами блока контроля постепенных отказов, прямой выход второго триггера подключен к второму входу пятого элемента И, отличающийся тем, что с целью обеспечения точности контроля и одновременного контроля N подключенных устройств в него введены генератор тактовых импульсов, подключенный к суммирующему входу пятого счетчика импульсов, выход которого подключен к первому входу третьего элемента ИЛИ, входу четвертого элемента задержки и первому входу четвертого элемента ИЛИ, выход которого соединен со входом счетчика импульсов по модулю N, последовательно соединенного с управляющим входом блока ячеек памяти, соединенного с табло отображения, селектор данных, выход которого соединен с входом первого порогового блока, второго порогового блока, последовательно соединенного с входом третьего инвертора, выход которого соединен с входом третьего элемента задержки, соединенного с первым входом девятого элемента И, второй вход которого связан с выходом четвертого элемента задержки, а выход девятого элемента И подключен к вторым входам четвертого элемента ИЛИ и третьего элемента ИЛИ, выход которого соединен с управляющим входом селектора данных, информационные входы блока ячеек памяти соединены с первым, вторым, третьим, четвертым, пятым, шестым, седьмым, восьмым, девятым счетчиками импульсов, регистром, первым, вторым, третьим, четвертым, пятым триггерами, формирователя паузы, формирователя импульсов, второй делитель частоты, вход которого соединен с выходом первого порогового блока, а выход с первым входом десятого элемента И, второй вход которого соединен с выходом первого порогового блока и суммирующим входом седьмого счетчика, выход десятого элемента И связан с суммирующим входом шестого счетчика, выход которого соединен с первым входом первого вычитателя, второй вход которого соединен с выходом первого счетчика, а выход с суммирующим входом восьмого счетчика, выход обнуления седьмого счетчика соединен с первым входом второго вычитателя, второй вход которого подключен к выходу обнуления второго счетчика, а выход второго вычитателя связан с суммирующим входом девятого счетчика, выход которого подключен к первому входу одиннадцатого элемента И и суммирующему входу десятого счетчика, выход которого соединен с вторым входом пятого элемента И, формирователь импульса, выход которого соединен с входом третьего делителя частоты, выход которого связан с суммирующим входом одиннадцатого счетчика импульсов, выход которого подключен к обнуляющему входу двенадцатого счетчика импульсов и входу четвертого инвертора, выход которого соединен со вторым входом одиннадцатого элемента И.

Принцип функционирования устройства состоит в следующем. При попадании среза эталонного импульса, соответствующего максимально допустимой длительности выхода параметра за границу области работоспособности, на период пребывания параметра в области работоспособности осуществляется анализ длительности этого периода и, если он меньше, чем минимальное время выполнения задачи, то считается, что при первоначальном пересечении параметром границы произошел отказ. Этот отказ фиксируется, и длительность рассмотренного эталонного импульса входит в суммарную продолжительность отказов. Кроме того, решение о том, что параметр вернулся в область работоспособности, принимается анализатором только после того, как время после пересечения параметром границы в направлении области работоспособности станет равным минимальной длительности выполнения задачи. В этот момент происходит сброс формирователя эталонного импульса, и устройство готовится к анализу нового факта пересечения параметра границы. Если параметр находился в области неработоспособности более короткий период времени, то анализатор фиксирует факт возникновения и длительность сбоя. Если число сбоев достигло порогового значения, то анализатор фиксирует факт отказа.

Целью изобретения является расширение класса решаемых задач за счет повышения точности результатов анализа путем введения контроля сбоев и введения одновременной обработки параметров контроля нескольких РЭИ.

Эта цель достигается тем, что в устройство [1] введены блок управления, содержащий селектор данных, счетчик импульсов по модулю N, генератор тактовых импульсов, элементы задержки блока ячеек памяти, элементы И, элементы ИЛИ и блок контроля сбоев, содержащего делитель частоты, счетчики импульсов, вычитатели, элемент ИЛИ, табло отображения (см. чертеж). Введение в прототип новых отличительных признаков позволяет устройству повысить точность контроля за счет фиксации сбоев и их продолжительности, вести псевдопараллельную обработку параметров поступающих на N входов, которая позволит сократить затраты, необходимые для создания N анализаторов для контроля N устройств.

Проведенный анализ уровня техники позволил установить, что аналоги, тождественные признакам заявленного технического решения, отсутствуют, что указывает на соответствие заявленного устройства условию патентоспособности «новизна». Введенные отличительные признаки - селектор данных, счетчик по модулю N, формирователи паузы, блок ячеек памяти, табло отображения не встречаются в них. Следовательно, заявляемое устройство удовлетворяет критерию «существенное отличие». Промышленная воспроизводимость введенных элементов обусловлена наличием элементной базы, на основе которой они могут быть выполнены.

На чертеже обозначено:

1 - Первый пороговый блок.

2 - Формирователь импульса.

3 - Первый элемент задержки.

4 - Первый инвертор.

5 - Первый элемент И.

6 - Второй элемент ИЛИ.

7 - Дифференцирующий элемент.

8 - Четвертый элемент И.

9 - Первый триггер.

10 - Третий элемент И.

11 - Второй инвертор.

12 - Второй элемент задержки.

13 - Формирователь паузы.

14 - Шестой элемент И.

15 - Третий триггер.

16 - Четвертый триггер.

17 - Второй счетчик.

18 - Генератор импульсов.

19 - Первый делитель частоты.

20 - Второй элемент И.

21 - Первый элемент ИЛИ.

22 - Первый счетчик.

23 - Переключатель.

24 - Регистр.

25 - Пятый элемент И.

26 - Третий счетчик.

27 - Второй триггер.

28 - Седьмой элемент И.

29 - Пятый триггер.

30 - Восьмой элемент И.

31 - Четвертый счетчик.

32 - Селектор данных.

33 - Третий элемент ИЛИ.

34 - Генератор тактовых импульсов.

35 - Пятый счетчик.

36 - Второй пороговый блок.

37 - Третий инвертор.

38 - Третий элемент задержки.

39 - Девятый элемент И.

40 - Четвертый элемент задержки.

41 - Четвертый элемент ИЛИ.

42 - Счетчик импульсов по модулю N.

43 - Блок ячеек памяти.

44 - Второй делитель частоты.

45 - Десятый элемент И.

46 - Шестой счетчик импульсов.

47 - Седьмой счетчик импульсов.

48 - Первый вычитатель.

49 - Восьмой счетчик импульсов.

50 - Второй вычитатель.

51 - Девятый счетчик импульсов.

52 - Табло отображения.

53 - Десятый счетчик импульсов.

54 - Пятый элемент ИЛИ.

55 - Формирователь импульса.

56 - Третий делитель частоты.

57 - Одиннадцатый счетчик импульсов.

58 - Четвертый инвертор.

59 - Одиннадцатый элемент И.

60 - Двенадцатый счетчик импульсов.

Анализатор работает следующим образом.

Устройство состоит из следующих блоков: блока контроля постепенных отказов, блока контроля сбоев и блока управления.

Принцип работы блока контроля постепенных отказов описан в [1]. Он состоит в сравнении времени нахождения параметра в отказовой области и максимально допустимого времени нахождения параметра в отказовой области. Если время нахождения параметра в отказовой области превысит данный предел, то фиксируется отказ и его длительность. Общее число зафиксированных отказов хранится в счетчике 17, а длительность фиксируется в счетчике 22.

Опишем функционирование блока управления, содержащего селектор данных 32 [4] (с.97), третий элемент ИЛИ 33, генератор тактовых импульсов 34 [4] (с.24), пятый счетчик 35, второй пороговый блок 36, третий инвертор 37, третий элемент задержки 38, девятый элемент И 39, четвертый элемент задержки 40, четвертый элемент ИЛИ 41, счетчик импульсов по модулю N 42, блок ячеек памяти 43, табло отображения 52.

Блок ячеек памяти 43 представляет собой матрицу ячеек размером Nх17. В качестве блока ячеек памяти может быть использовано запоминающее устройство с произвольной выборкой [4] (с.255).

В ячейке [i, 1] записано число, равное абсолютной величине , где - максимально допустимое время пребывания параметра в отказовой области, при превышении которого фиксируется отказ объекта контроля; - минимально необходимое для выполнения задачи время пребывания параметра в области работоспособности состояний, i - число, содержащееся в счетчике импульсов 42. При переключении селектора данных с i-го входа на i+1-ый в ячейку [1, 2] записывается число, соответствующее текущему значению счетчика 26, в регистр 24 и счетчик 26 записываются числа из ячеек [i+1,1] и [i+1,2] соответственно, в ячейку [i, 3] записывается содержимое счетчика 22, а в счетчик 22 записывается число из ячейки [i+1,3], в ячейку [i, 4] записывается содержимое счетчика 31, а в счетчик 31 записывается число из ячейки [i+1,4], в ячейку [i, 5] записывается содержимое счетчика 17, а в счетчик 17 записывается число из ячейки [i+1,5], в ячейку [i, 6] записывается содержимое счетчика 46, а в счетчик 46 записывается число из ячейки [i+1,6], в ячейку [i, 7] записывается содержимое счетчика 47, а в счетчик 47 записывается число из ячейки [i+1,7], в ячейку [i, 8] записывается содержимое счетчика 49, а в счетчик 49 записывается число из ячейки [i+1,8], в ячейку [i, 9] записывается содержимое счетчика 51, а в счетчик 51 записывается число из ячейки [i+1,9], в ячейку [i, 10] записывается состояние триггера 9, а состояние триггера 9 становится равным значению ячейки [i+1,10], в ячейку [i, 11] записывается состояние триггера 15, а состояние триггера 15 становится равным значению ячейки [i+1,11], в ячейку [i, 12] записывается состояние триггера 16, а состояние триггера 16 становится равным значению ячейки [i+1,12], в ячейку [i, 13] записывается состояние триггера 27, а состояние триггера 27 становится равным значению ячейки [i+1,13], в ячейку [i, 14] записывается состояние триггера 29, а состояние триггера 29 становится равным значению ячейки [i+1,14]. Длительность паузы, формируемой формирователем паузы 13, хранится в ячейке [i, 15] и равно i-го абонента.

Соответственно при переключении селектора данных с i-го входа на i+1-ый значение из длительность паузы, формируемой формирователем паузы 13, становится равной числу из ячейки [i+1,15], соответствует для i-го абонента. При переключении на следующего абонента длительность импульса на выходе формирователя 2 становится равной числу из ячейки [i+1,15]. В ячейку [i, 16] записывается содержимое счетчика 53, а в счетчик 53 записывается число из ячейки [1+1,16]. На табло отображения 52 выводятся значения из ячеек памяти с адресами [i, 5] (количество отказов устройства, подключенного к i-му входу), [1,3] (суммарная длительность отказов контролируемого устройства), [i, 9] (количество сбоев контролируемого устройства), [i, 8] (суммарная продолжительность сбоев), [i, 17] (наработка на сбой за требуемый период времени).

Генератор тактовых импульсов 34 заполняет счетчик импульсов 35, имеющий емкость К. Длительность опроса одного устройства будет определяться как Т0=К-Тт, где Тт - период следования тактовых импульсов. Селектор данных 32 коммутирует вход №1 с входом анализатора. При заполнении счетчика 35 на его выходе появляется импульс переполнения, который, поступая на управляющий вход селектора данных 32, дает команду на переключение на следующий вход. Этот же импульс, проходя через четвертый элемент ИЛИ 41, увеличивает число, хранимое в счетчике 42, на единицу, которое определяет номер элемента, который будет опрашиваться в этот период опроса, и номер строки в матрице ячеек памяти, соответствующей этому элементу. При поступлении на вход счетчика 42 N-го импульса он обнуляется. Селектор данных 32 переключается на вход с номером №1.

В случае, если на выходе селектора данных 32 присутствует напряжение, отличное от нуля, второй пороговый блок 36 формирует положительный импульс, который, инвертируясь на третьем инверторе 37 и проходя через четвертый элемент задержки 40, запрещает прохождение импульса через девятый элемент И 39. Если на выходе селектора данных 32 отсутствует напряжение, второй пороговый блок 36 формирует отрицательный импульс, который, инвертируясь на третьем инверторе 37 и проходя через четвертый элемент задержки 40, разрешает прохождение импульса от счетчика 35, задержанного на элементе задержки 40 через девятый элемент И 39. Этот импульс, проходя через элемент ИЛИ 41, увеличивает на единицу содержание счетчика 42 и проходя через элемент ИЛИ 33, дает команду селектору данных 32 на переключение на следующий вход. Время, на которое задерживают импульсы элементы задержки 38 и 40, равно времени срабатывания счетчика импульсов 42.

Опишем функционирование блока контроля сбоев, содержащего второй делитель частоты 44, десятый элемент И 45, шестой счетчик импульсов 46, седьмой счетчик импульсов 47, первый вычитатель 48 [4, с.218], восьмой счетчик импульсов 49, второй вычитатель 50, девятый счетчик импульсов 51, десятый счетчик импульсов 53, формирователь импульса 55, третий делитель частоты 56, одиннадцатый счетчик импульсов 57, четвертый инвертор 58, одиннадцатый элемент И 59, двенадцатый счетчик импульсов 60.

Импульс с первого порогового блока 1 поступает на второй делитель частоты 44, на вход десятого элемента И 45. Шестой счетчик импульсов 46 будет фиксировать общую продолжительность нахождения параметра в отказовой области. На вход первого вычитателя 48 поступает число из шестого счетчика импульсов 46 и с первого счетчика импульсов 22. В восьмой счетчик 49 запишется время продолжительности сбоев. Седьмой счетчик импульсов 47 содержит число всех фактов выхода параметра в отказовую область. Из этого значения на втором вычитателе 50 вычитается значение, содержащееся во втором счетчике 17. Значение с выхода второго вычитателя 50 записывается в девятый счетчик импульсов 51 и соответствует количеству произошедших сбоев. При поступлении положительного импульса с выхода девятого счетчика импульсов 51, сигнализирующего о том, что значение счетчика увеличилось на единицу, увеличивается значение десятого счетчика импульсов 53, емкость которого соответствует пороговому количеству сбоев, после которого фиксируется отказ. Импульс переполнения с выхода десятого счетчика импульсов 53, проходя через пятый элемент ИЛИ 54, увеличивает значение счетчика 17, содержащего общее число отказов. Формирователь импульса 55 формирует положительный импульс, поступающий на вход третьего дифференцирующего элемента 56, который заполняет одиннадцатый счетчик импульсов 57, емкость которого определяет требуемое время для определения наработки на сбой. До тех пор пока одиннадцатый счетчик импульсов 57 не заполнится, то есть на его выходе будет отрицательный потенциал, четвертый инвертор 58 разрешает прохождение положительного импульса с выхода девятого счетчика импульсов 51, сигнализирующего о том, что значение счетчика увеличилось на единицу через одиннадцатый элемент И 59, который заполняет двенадцатый счетчик импульсов 60. При переполнении одиннадцатого счетчика импульсов 57 импульс переполнения с его входа поступает на управляющий вход двенадцатого счетчика импульсов 60, сигнализирующего о том, что значение из двенадцатого счетчика импульсов 60 должно записаться в ячейку памяти [i, 17], и он должен обнулиться. Таким образом, в ячейке памяти [i, 17] будет содержаться значение наработки на сбой за требуемое значение времени.

На табло отображения для каждого устройства выводятся следующие параметры:

- число постепенных отказов (содержимое счетчика 17);

- суммарная продолжительность постепенных отказов (содержимое счетчика 22);

- суммарная продолжительность сбоев (содержимое счетчика 49);

- число сбоев (содержимое счетчика 51);

- наработки на сбой (содержимое ячейки [1,17]).

При дальнейшей обработке данные параметры позволяют найти статистические оценки показателей надежности контролируемого объекта (средней наработки на отказ, вероятности безотказной работы, коэффициента готовности и др.).

Таким образом, за счет реализации одновременного контроля N РЭИ, подключенных к анализатору, повышается эффективность использования данного устройства относительно прототипа в N раз и нет необходимости в отключении анализатора от одного РЭИ для контроля другого. Повышена точность контроля за счет введения процесса фиксации сбоев РЭИ и их продолжительности. На основе полученных данных принимается решение о работоспособности или неработоспособности контролируемого РЭИ. Блок управления разрешает опрос только активных устройств, работающих на данный момент. Если устройство не работает, то анализатор не контролирует данное устройство. Табло отображения позволяет наблюдать за изменением контролируемых параметров всех подключенных устройств одновременно.

Источники информации

1. Изобретение «Анализатор параметрических отказов»: авторское свидетельство СССР №4162818/24-24 опубл. 23.06.88.

2. Авторское свидетельство СССР №1005073, кл. G 06 F 15/46, опубл. 1981.

3. Авторское свидетельство СССР №1302298, кл. G 06 F 15/46, опубл. 1985.

4. Токхейм Р. «Основы цифровой электроники»: Пер. с англ. - М.: Мир, 1998, - 392 с.

5. Шубинский И.Б. и др. «Активная защита от отказов управляющих модульных вычислительных систем». - СПб: Наука, 1993, - 284 с.

Анализатор параметрических отказов и сбоев, состоящий из анализатора отказов, отличающийся тем, что в него введены генератор тактовых импульсов, подключенный к пятому счетчику импульсов, выход которого подключен к третьему элементу ИЛИ, входу четвертого элемента задержки и четвертому элементу ИЛИ, выход которого соединен с входом счетчика импульсов по модулю N, последовательно соединенного с управляющим входом блока ячеек памяти, соединенного с табло отображения, селектор данных, выход которого соединен с входом первого порогового блока анализатора отказов и второго порогового блока, соединенного с входом третьего инвертора, выход которого соединен с третьим элементом задержки, который соединен с девятым элементом И, причем импульс от пятого счетчика импульсов проходит через четвертый элемент задержки на девятый элемент И, выход которого подключен к входам четвертого и третьего элементов ИЛИ, выход которого соединен с управляющим входом селектора данных, ячейки блока ячеек памяти соединены соответственно с первого по четвертый счетчиками импульсов анализатора отказов, с пятого по девятый счетчиками импульсов, регистром анализатора отказов, с первого по пятый тригерами анализатора отказов, формирователем паузы анализатора отказов, формирователем импульсов анализатора отказов, второй делитель частоты, вход которого соединен с выходом первого порогового блока анализатора отказов, а выход - с первым входом десятого элемента И, другой вход которого соединен с выходом первого порогового блока анализатора отказов, причем седьмой счетчик импульсов фиксирует число всех фактов выхода параметра в отказовую область, из которого во втором вычитателе вычитается значение, содержащееся во втором счетчике импульсов анализатора отказов, выход десятого элемента И связан с входом шестого счетчика, выход которого соединен с первым вычитателем, второй вход которого соединен с выходом первого счетчика импульсов анализатора отказов, а выход - с входом восьмого счетчика, второй вход второго вычитателя подключен к выходу второго счетчика анализатора отказов, а выход второго вычитателя связан с входом девятого счетчика импульсов, выход которого подключен к первому входу одиннадцатого элемента И и десятому счетчику, импульс переполнения с выхода которого проходит через пятый элемент ИЛИ анализатора отказов, формирователь импульсов, выход которого соединен с входом третьего делителя частоты, выход которого связан с входом одиннадцатого счетчика импульсов, выход которого подключен к обнуляющему входу двенадцатого счетчика импульсов и входу четвертого инвертора, выход которого соединен с входом одиннадцатого элемента И.