Контур дискретного считывания (варианты)

Иллюстрации

Показать всеИзобретение относится к контуру дискретного считывания аналогового сигнала, именуемого семплирующим контуром. Технический результат заключается в повышении точности за счет уменьшения влияния шумовых компонентов. Если конденсатор (С), используемый в семплирующем контуре для семплирования напряжения, периодически заряжается в повторяющиеся периоды семплирования, процесс заряда конденсатора не достигает равновесного состояния вследствие его разряда токами утечки, который происходит между периодами семплирования. Согласно изобретению в период семплирования цепь (10) заряда/разряда осуществляет заряд или разряд конденсатора током, зависящим от разности входного напряжения Vin и выходного напряжения Vout. Цепь (18) хранения напряжения хранит значение опорного напряжения, получаемого путем АЦ-преобразования последнего значения выходного напряжения Vout, соответствующего завершению периода семплирования. До начала следующего периода семплирования цепь (12) подзаряда заряжает или разряжает конденсатор током, определяемым разностью выходного напряжения и напряжения, полученного ЦА-преобразованием значения опорного напряжения, поступающего из цепи (18) хранения напряжения. Благодаря этому цепь подзаряда компенсирует разряд конденсатора, происходивший между периодами семплирования, т.е. восстанавливает заряд, который имелся на конденсаторе в конце предшествующего периода семплирования. В результате достигается быстрая сходимость выходного напряжения Vout к целевому семплируемому напряжению. 2 н. и 6 з.п. ф-лы, 6 ил.

Реферат

Область техники, к которой относится изобретение

Настоящее изобретение относится в широком смысле к контуру дискретного считывания (далее для краткости именуемого семплирующим контуром) для осуществления дискретного считывания (семплирования) входного аналогового сигнала. Более конкретно, изобретение относится к выделению с высокой точностью дискретно считываемого (семплируемого) сигнала, который периодически появляется во входном сигнале, благодаря устранению влияния шумовых компонентов, имеющихся в считываемом сигнале.

Уровень техники

Известно применение контура выборки/хранения в качестве контура для выполнения операции семплирования аналогового сигнала. Контур выборки/хранения выполняет две операции: операцию семплирования напряжения входного сигнала и операцию хранения считанного напряжения с выдачей его в качестве выходного сигнала. Для осуществления выборки/хранения используется конденсатор. Интегральные схемы выборки/хранения реализуются в двух вариантах: со встроенным конденсатором, в котором конденсатор встроен в интегральную схему, и с внешним конденсатором, в котором конденсатор находится вне интегральной схемы.

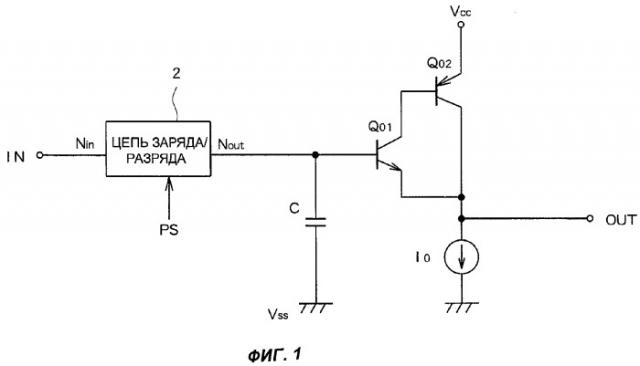

Фиг.1 представляет собой схему, иллюстрирующую принцип работы традиционного контура выборки/хранения. Между входным выводом (входом) IN контура выборки/хранения и конденсатором С включена цепь 2 заряда/разряда. Включение/отключение цепи 2 заряда/разряда производится управляющим сигналом PS. Находясь во включенном состоянии, цепь 2 заряда/разряда формирует ток, соответствующий разности напряжений на входном и выходном выводах Nin, Nout данной цепи. Этот ток соответственно заряжает или разряжает конденсатор С. С целью уменьшить влияния входного и выходного импедансов на входной сигнал Vin, подаваемый на входной вывод IN, выходной импеданс цепи 2 заряда/разряда делается низким, а ее входной импеданс высоким. Для того чтобы сохранять считанное напряжение, конденсатор С присоединен к выходному выводу OUT контура выборки/хранения через повторитель напряжения. Повторитель напряжения обеспечивает высокий входной импеданс для конденсатора С и низкий выходной импеданс для выходного вывода OUT. Кроме того, благодаря повторителю напряжения напряжение, которое хранится на конденсаторе С, может считываться с выходного вывода OUT в виде выходного напряжения Vout.

Как показано на фиг.1, повторитель напряжения образован транзисторами Q01 и Q02, включенными в виде пары Дарлингтона. Схема Дарлингтона, образованная транзисторами Q01 и Q02, способна обеспечить более высокий импеданс, чем схема с заземленным эмиттером на базе единственного транзистора. Как следствие, она способна предотвратить разряд конденсатора С через выходной вывод OUT. В одном из вариантов выполнения транзистор Q01 относится к npn-типу, причем конденсатор С и выходной вывод Nout цепи 2 заряда/разряда присоединены к его базе. Коллектор и эмиттер транзистора Q01 присоединены соответственно к базе транзистора Q02 и к выходному выводу OUT. Транзистор Q02 является транзистором pnp-типа, причем его эмиттер и коллектор присоединены соответственно к источнику VCC напряжения и к выходному выводу OUT. Источник I0 тока, включенный между коллектором транзистора Q02 и потенциалом VSS земли, обеспечивает протекание тока Ice в коллекторно-эмиттерной цепи транзистора Q02.

Если при семплировании сигнала в форме напряжения установить большой ток заряда/разряда, протекающий в цепи 2 заряда/разряда, время, необходимое для осуществления заряда или разряда конденсатор С, может быть сокращено, т.е. скорость (частота) семплирования может быть увеличена. С другой стороны, контур выборки/хранения становится чувствительным к шумовым компонентам, которые входят в состав входного сигнала Vin и изменяются с относительно малыми постоянными времени. В связи с этим возникает проблема, связанная с точностью и надежностью дискретно считываемого (семплируемого) напряжения. Одна из мер, направленная на решение этой проблемы, состоит в том, чтобы сделать ток заряда/разряда в цепи 2 заряда/разряда малым и производить семплирование входного сигнала в течение времени, которое является значительным по сравнению с постоянными времени шумовых компонентов.

Однако при этом возникает следующая проблема. Если сигнал, подлежащий семплированию, присутствует во входном сигнале только в дискретные интервалы времени, невозможно каждый раз обеспечивать длительное время семплирования и, следовательно, представляется затруднительным реализовать стабильное семплирование за счет усиления противодействия шумам путем выбора малого тока заряда/разряда. Одна из мер, направленная на решение данной проблемы, состоит в том, чтобы задавать в разные моменты времени различные периоды считывания сигнала синхронно с появлениями семплируемого сигнала. Более конкретно, необходимо поочередно осуществлять операцию заряда/разряда конденсатора С цепью 2 заряда/разряда согласованно с присутствием семплируемого сигнала в период считывания сигнала и операцию удерживания результирующего напряжения на конденсаторе С в течение периода хранения (т.е. в интервале между периодами считывания). При этом суммарный период считывания будет кумулятивно возрастать, так что в ходе описанного процесса считываемое напряжение будет постепенно приближаться к целевому семплируемому напряжению.

Однако, хотя описанная мера направлена на то, чтобы подавить ток, протекающий между конденсатором С и выходным выводом OUT, на практике весьма трудно добиться полного подавления этого тока. Например, в случае использования рассмотренной пары Дарлингтона, через транзистор Q01 протекает ток базы, который в (1/hFE1×1/hFE2) раз превышает ток Ice, протекающий в коллекторно-эмиттерной цепи транзистора Q02 (hFE1 и hFE2 - это коэффициенты усиления по току транзисторов Q01 и Q02 соответственно). При этом возникает опасность, что конденсатор С будет со временем разряжаться указанными токами при соответствующем изменении напряжения Vout. В частности, если весь рассматриваемый контур, включая конденсатор С, реализован в виде единой интегральной схемы, представляется затруднительным обеспечить достаточно большую емкость конденсатора С в связи с требованиями по сокращению площади чипа. В связи с этим выходное напряжение Vout может существенно изменяться даже при относительно малом разрядном токе.

В описанном способе, в соответствии с которым сходимость к целевому семплируемому напряжению осуществляется постепенно с использованием многократного семплирования в течение дискретных периодов и соответственно влияние процесса разряда конденсатора С во время периодов хранения напряжения является значительным (т.е. периоды хранения являются длительными), скорость заряда в периоды семплирования является недостаточно высокой. Это приводит к тому, что сходимость к целевому семплируемому напряжению не достигается или для достижения данного напряжения требуется длительное время.

Раскрытие изобретения

Настоящее изобретение направлено на преодоление рассмотренных проблем. Таким образом, техническая задача, на решение которой направлено изобретение, заключается в создании семплирующего контура, который позволяет быстро сформировать целевое семплируемое напряжение в том случае, когда операция семплирования выполняется порциями в течение множества дискретных периодов, следующих друг за другом.

В соответствии с первым аспектом изобретения семплирующий контур содержит:

конденсатор для подачи на выходной вывод выходного напряжения, соответствующего находящемуся на нем заряду,

цепь заряда/разряда для периодического инициирования периодов семплирования и для осуществления заряда или разряда конденсатора в зависимости от напряжения семплируемого сигнала, появляющегося в составе входного сигнала в течение каждого из периодов семплирования,

цепь хранения опорного напряжения для определения значения опорного напряжения на основе последнего значения, которое принимает выходное напряжение в момент завершения периода семплирования, и для хранения определенного таким образом значения опорного напряжения,

цепь генерирования целевого напряжения для генерирования, на основе значения опорного напряжения, восстанавливаемого целевого напряжения,

цепь восстановления выходного напряжения для инициирования периодов восстановления, которые предшествуют, по меньшей мере, частично, соответствующим периодам семплирования, и для осуществления заряда или разряда конденсатора в соответствии с уровнем восстанавливаемого целевого напряжения в каждом из периодов восстановления с формированием выходного напряжения, соответствующего последнему значению напряжения для периода семплирования, непосредственно предшествующего соответствующему периоду восстановления.

В данном семплирующем контуре последнее выходное напряжение, т.е. напряжение, соответствующее концу первого периода семплирования, хранится в качестве значения, именуемого далее значением опорного напряжения. Цепь восстановления выходного напряжения заряжает или разряжает конденсатор в зависимости от значения опорного напряжения в период восстановления, который, по существу, предшествует следующему (в данном случае второму) периоду семплирования. Тем самым данная цепь компенсирует потерю заряда при разряде конденсатора, обусловленном прерыванием процесса заряда или разряда посредством цепи заряда/разряда, во временном интервале между двумя периодами семплирования (т.е. осуществляет операцию восстановления). Посредством данной операции заряд, находящийся на конденсаторе, восстанавливается до заряда, который имелся на нем в конце первого периода семплирования. После этого во время второго периода семплирования снова осуществляется процесс заряда или разряда конденсатора посредством цепи заряда/разряда. Таким образом, обеспечивается возможность быстрого семплирования сигнала путем выполнения частичного считывания сигнала во время последовательности кратковременных периодов семплирования.

При осуществлении периодов восстановления необходимо выполнить требование, состоящее в том, что каждая операция восстановления должна быть завершена до конца соответствующего (следующего) периода семплирования. При условии, что это требование выполняется, каждый период восстановления может частично перекрываться во времени с соответствующим ему периодом семплирования. Однако в этом случае эффективный период семплирования будет соответствовать периоду, начинающемуся после окончания периода восстановления. По этой причине для того, чтобы операция семплирования эффективно выполнялась в каждый период семплирования, желательно, чтобы взаимное перекрывание периода восстановления и периода семплирования было как можно меньшим. Особенно желательно, чтобы каждый период восстановления заканчивался непосредственно перед началом соответствующего ему периода семплирования.

Цепь восстановления выходного напряжения может обеспечивать более высокую скорость процесса заряда/разряда, чем цепь заряда/разряда.

В рассматриваемом семплирующем контуре каждая операция восстановления может быть быстро завершена, т.е. периоды восстановления могут быть короткими. Чтобы избежать опасности того, что шум, содержащийся во входном сигнале, влияет на операцию семплирования, нельзя увеличить скорость выполнения операции заряда/разряда цепью заряда/разряда. В отличие от этого, скорость выполнения операции заряда/разряда цепью восстановления выходного напряжения можно увеличить до желательного значения, поскольку восстанавливаемое целевое напряжение представляет собой фиксированное напряжение, которое генерируется на основе значения опорного напряжения и в принципе не изменяется под влиянием шумов или аналогичных факторов.

В соответствии с первым аспектом изобретения, с учетом того, что восстанавливаемое целевое напряжение может быть сгенерировано независимо от входного сигнала, длительность периодов восстановления может быть установлена независимо от длительности периодов семплирования. Использование длительных периодов восстановления позволяет реализовать эффективные операции восстановления без увеличения скорости заряда/разряда, обеспечиваемой цепью восстановления выходного напряжения.

В предпочтительном варианте изобретения входной сигнал основан на телевизионном (ТВ) сигнале и включает в себя в качестве семплируемого сигнала характерный сигнал, который появляется в составе телевизионного сигнала в периоды вертикального обратного хода луча. В этом случае цепь заряда/разряда инициирует периоды семплирования таким образом, что они находятся в пределах соответствующих периодов вертикального обратного хода луча.

При этом предпочтительно также, чтобы цепь восстановления выходного напряжения инициировала периоды восстановления таким образом, чтобы они находились в пределах соответствующих периодов строчной развертки ТВ сигнала.

В соответствии со вторым вариантом осуществления изобретения семплирующий контур содержит:

конденсатор для подачи на выходной вывод выходного напряжения, соответствующего находящемуся на нем заряду,

цепь заряда/разряда для периодического инициирования n видов периодов Si семплирования, которые соответствуют n типам семплируемых сигналов Ui, появляющихся в составе входного сигнала, и для осуществления заряда или разряда конденсатора в зависимости от напряжения семплируемого сигнала Ui каждого типа, появляющегося в составе входного сигнала в течение периода Si семплирования, ассоциированного с указанным семплируемым сигналом, причем n представляет собой целое число, равное или превышающее 2, a i - целое число, удовлетворяющее соотношению 1≤i≤n,

цепь хранения опорного напряжения для определения значений опорных напряжений Vi, соответствующих n типам семплируемых сигналов Ui, на основе последних значений, которые принимает выходное напряжение в момент завершения n видов периодов Si семплирования, и для хранения определенных таким образом значений опорных напряжений Vi,

цепь генерирования целевого напряжения для генерирования восстанавливаемых целевых напряжений Wi на основе соответствующих значений опорных напряжений Vi и

цепь восстановления выходного напряжения для инициирования для каждого из периодов Si семплирования каждого вида периода Рi восстановления, который начинается после завершения предшествующего периода Si семплирования и завершается до начала, по меньшей мере, части соответствующего ему периода семплирования, и для осуществления заряда или разряда конденсатора в зависимости от соответствующего целевого напряжения Wi, восстановленного во время периода Pi восстановления, с получением тем самым выходного напряжения, соответствующего последнему значению напряжения для периода семплирования, непосредственно предшествующего соответствующему периоду восстановления.

В семплирующем контуре согласно данному варианту изобретения операции семплирования осуществляются во время последовательности периодов семплирования для каждого из нескольких семплируемых сигналов, которые периодически (т.е. поочередно) появляются во входном сигнале. Это позволяет реализовать семплирование, которое обладает повышенной устойчивостью по отношению к шумам и, следовательно, является стабильным.

В предпочтительном варианте цепь хранения опорного напряжения содержит: аналого-цифровой преобразователь для осуществления аналого-цифрового преобразования (АЦ-преобразования) последних значений выходного напряжения в цифровые значения и цепь хранения для хранения цифровых значений в качестве значений опорных напряжений. При этом цепь генерирования целевого напряжения содержит цифроаналоговый преобразователь для генерирования восстанавливаемых целевых напряжений путем цифроаналогового преобразования (ЦА-преобразования) цифровых значений, хранящихся в цепи хранения, в аналоговые значения.

В таком семплирующем контуре операция семплирования осуществляется в период семплирования тока после того, как разряд конденсатора в период хранения, продолжающийся от завершения предыдущего периода семплирования до начала текущего периода семплирования, был скомпенсирован путем подзаряда посредством цепи восстановления выходного напряжения. Такое решение позволяет быстрее достичь уровня целевого семплируемого напряжения.

Краткое описание чертежей

На фиг.1 представлена схема, иллюстрирующая принцип действия традиционного контура выборки/хранения.

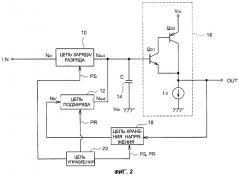

Фиг.2 - это схема, используемая для описания принципа действия семплирующего контура согласно изобретению.

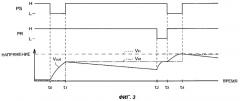

На фиг.3 схематично представлена временная диаграмма, иллюстрирующая работу контура выборки/хранения в соответствии с первым вариантом изобретения.

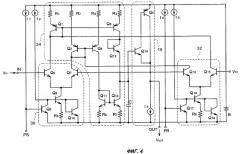

На фиг.4 представлена схема контура выборки/хранения по первому варианту изобретения, в которую не включены цепь хранения напряжения и цепь управления.

На фиг.5 приведена упрощенная блок-схема контура в соответствии со вторым вариантом изобретения, предназначенного для декодирования цветного ТВ сигнала в системе СЕКАМ.

На фиг.6 схематично представлена временная диаграмма, иллюстрирующая работу контура выборки/хранения в соответствии со вторым вариантом изобретения.

Осуществление изобретения

Далее со ссылками на прилагаемые чертежи будут описаны предпочтительные варианты осуществления изобретения.

Вариант 1

Данный вариант относится к контуру выборки/хранения, использующему семплирующий контур согласно изобретению. Принцип действия данного контура выборки/хранения (включая семплирующий контур) иллюстрируется схемой, представленной на фиг.2. Представленный здесь контур содержит цепь 10 заряда/разряда, цепь 12 подзаряда, конденсатор 14 (конденсатор С), повторитель 16 напряжения, цепь 18 хранения напряжения и цепь 20 управления.

Цепь 10 заряда/разряда включена между входным выводом IN контура выборки/хранения и одной из обкладок конденсатора С. Включение/отключение цепи 10 заряда/разряда производится управляющим сигналом PS, который поступает от цепи 20 управления. Находясь во включенном состоянии, цепь 10 заряда/разряда формирует ток, соответствующий разности напряжений на входном и выходном выводах Nin, Nout данной цепи. Этот ток соответственно заряжает или разряжает конденсатор С. Выходной импеданс цепи 10 заряда/разряда сделан низким, а ее входной импеданс высоким, чтобы избежать влияния на входной сигнал Vin, подаваемый на входной вывод IN, влияния этих импедансов.

Цепь 12 подзаряда присоединена к конденсатору С параллельно цепи 10 заряда/разряда, причем к входному выводу Nin' этой цепи приложено выходное напряжение цепи 18 хранения напряжения. Включение/отключение цепи 12 подзаряда производится управляющим сигналом PR, который поступает от цепи 20 управления. Находясь во включенном состоянии, цепь 12 подзаряда формирует ток, соответствующий разности напряжений на ее входном выводе Nin' и на выходном выводе Nout'. Этот ток соответственно заряжает или разряжает конденсатор С.

Одна обкладка конденсатора С соединена с выходными выводами Nout и Nout' цепи 10 заряда/разряда и цепи 12 подзаряда, а также с базой транзистора Q01. Его вторая обкладка находится под потенциалом VSS земли. Напряжение на конденсаторе С соответствует накопленному на нем заряду (количеству электричества), причем данное напряжение прикладывается к базе транзистора Q01.

Повторитель 16 напряжения включен между конденсатором С и выходным выводом OUT контура выборки/хранения и обеспечивает преобразование импеданса. Более конкретно, в то время как входной импеданс повторителя 16 напряжения (т.е. его импеданс со стороны конденсатора С) является высоким, повторитель 16 напряжения имеет низкий выходной импеданс. Это позволяет снимать напряжение на конденсаторе С в качестве выходного напряжения Vout с выходного вывода OUT, предотвращая при этом падение напряжения на конденсаторе С вследствие его разряда через выходной вывод OUT. Преобразование импеданса может быть реализовано, например, с использованием транзисторов Q01 и Q02, включенных по схеме Дарлингтона. В конкретном варианте транзистор Q01 относится к npn-типу, причем конденсатор С присоединен к его базе. Коллектор и эмиттер транзистора Q01 присоединены соответственно к базе транзистора Q02 и к выходному выводу OUT. Транзистор Q02 является транзистором pnp-типа, причем его эмиттер и коллектор присоединены соответственно к источнику VCC напряжения и к выходному выводу OUT. Источник I0 тока, включенный между коллектором транзистора Q02 и потенциалом VSS земли, обеспечивает протекание тока Ice в коллекторно-эмиттерной цепи транзистора Q02.

Цепь 18 хранения напряжения состоит из аналого-цифрового преобразователя для осуществления АЦ-преобразования, т.е. преобразования выходного напряжения Vout аналогового сигнала в цифровое значение (значение опорного напряжения); регистра для хранения значения опорного напряжения и цифроаналогового преобразователя для осуществления ЦА-преобразования, т.е. преобразования значения опорного напряжения в аналоговый сигнал (восстанавливаемое целевое напряжение). АЦ- и ЦА-преобразования производятся в цепи 18 хранения напряжения в соответствии с управляющими сигналами PS и PR, которые подаются от цепи 20 управления. Построенная описанным образом цепь 18 хранения напряжения функционирует в качестве цепи хранения опорного напряжения и цепи восстановления выходного напряжения.

Цепь 20 управления обеспечивает управление цепью 10 заряда/разряда, цепью 12 подзаряда и цепью 18 хранения напряжения посредством генерирования управляющих сигналов PS и PR. На фиг.3 представлена схематичная временная диаграмма, иллюстрирующая работу контура выборки/хранения в соответствии с рассматриваемым вариантом изобретения. Когда управляющий сигнал PS или PR находится на своем нижнем уровне L, цепь 10 заряда/разряда и цепь 12 подзаряда осуществляют операцию заряда/разряда конденсатора С. Когда же управляющий сигнал PS или PR находится на своем верхнем уровне Н, данная операция заряда/разряда конденсатора С не производится. Более конкретно, период семплирования и указанная операция заряда/разряда, выполняемая цепью 10 заряда/разряда, начинаются, когда уровень управляющего сигнала PS становится равным L (т.е. в момент t0). При этом выходное напряжение Vout начинает изменяться, приближаясь к уровню входного сигнала Vin.

По завершении периода семплирования (в момент t1) уровень управляющего сигнала PS повышается до Н и операция заряда/разряда, производимая цепью 10 заряда/разряда, соответственно прекращается. Цепь 18 хранения напряжения производит АЦ-преобразование выходного напряжения Vout и сохраняет результирующее цифровое значение синхронно с повышением уровня управляющего сигнала PS. Далее цепь 18 хранения напряжения выдает сигнал Vst напряжения, который получен ЦА-преобразованием соответствующего цифрового значения. На фиг.3 показано, что в момент окончания периода семплирования (t1) выходное напряжение Vout не достигает уровня входного сигнала Vin.

Тогда как (в период t1-t2) сигнал Vst напряжения, который формируется на выходе цепи 18 хранения напряжения, остается постоянным, выходной сигнал Vout медленно уменьшается по мере того, как конденсатор С разряжается током базы транзистора Q02. Как следствие, возникает различие между сигналом Vst напряжения и выходным напряжением Vout.

Период подзаряда (период восстановления выходного напряжения) инициируется до начала следующего периода семплирования (t3-t4). Более конкретно, он начинается, когда уровень управляющего сигнала PR станет равным L (т.е. в момент t2). Когда уровень управляющего сигнала PR понизится до L, цепь 12 подзаряда начинает осуществлять операцию заряда/разряда, так что выходное напряжение Vout начинает изменяться, приближаясь к уровню сигнала Vst. В рассматриваемом варианте цепь 12 подзаряда обеспечивает более быстрый (интенсивный) процесс заряда/разряда, чем цепь 10 заряда/разряда. Соответственно, как это показано на фиг.3, в период подзаряда выходное напряжение Vout изменяется быстрее, чем в период семплирования. Операция заряда/разряда, осуществляемая цепью 12 подзаряда, компенсирует разряд конденсатора С в период t1-t2. К моменту t3 (т.е. к моменту завершения периода подзаряда и начала второго периода семплирования) уровень выходного напряжения восстановлен до его уровня в момент t1 (т.е. в момент завершения первого периода семплирования) или до уровня, близкого к этому значению.

Во второй период семплирования (в период t3-t4) процесс заряда/разряда конденсатора С цепью 10 заряда/разряда осуществляется с уровня, соответствующего восстановленному значению Vout. Как следствие, к моменту t4 (к завершению второго периода семплирования) уровень выходного напряжения Vout будет ближе к входному сигналу Vin, чем к моменту t1 (к моменту завершения первого периода семплирования). Пример, проиллюстрированный на фиг.3, соответствует ситуации, когда выходное напряжение Vout достигает уровня входного сигнала Vin во второй период семплирования. Однако, даже если за время второго периода семплирования уровень входного сигнала Vin не будет достигнут, будет иметь место постепенное приближение уровня выходного напряжения Vout к уровню входного сигнала Vin по мере повторных выполнений своих функций цепью 12 подзаряда и цепью 10 заряда/разряда.

Таким образом, поскольку, как это было описано выше, операция подзаряда, выполняемая цепью 12 подзаряда, компенсирует процесс разряда конденсатора С, имеющий место после завершения предшествующего периода семплирования, повторяющиеся в соответствующие дискретные периоды операции семплирования способны обеспечить приближение выходного напряжения Vout к уровню входного сигнала Vin. Такое решение позволяет уменьшить скорость процесса заряда/разряда, обеспечиваемую цепью 10 заряда/разряда, без необходимости специального учета процесса разряда конденсатора С между периодами семплирования. Это, в свою очередь, позволяет повысить устойчивость по отношению к шумам и стабильность процесса семплирования.

На фиг.4 представлена схема контура выборки/хранения, в которую не включены цепь 18 хранения напряжения и цепь 20 управления. Представленный контур содержит биполярные pnp-транзисторы Q1-Q5, биполярные npn-транзисторы Q6-Q19, источники I1-I5 тока, резисторы R1-R8, конденсатор С и источник В напряжения.

В данном контуре блок 30 является частью дифференциального усилителя, входящего в состав цепи 10 заряда/разряда, тогда как блок 32 является частью дифференциального усилителя, входящего в состав цепи 12 подзаряда. Блок 34, который предусмотрен на стороне нагрузки и является общим для обоих дифференциальных усилителей цепи 10 заряда/разряда и цепи 12 подзаряда, генерирует ток, соответствующий разности между входными напряжениями указанных дифференциальных усилителей, и обеспечивает соответственно заряд или разряд конденсатора С. Напряжение на конденсаторе С соответствует накопленному на нем заряду, причем данное напряжение подается в качестве выходного напряжения Vout на выходной вывод OUT через повторитель 16 напряжения.

Транзисторы Q6 и Q7 в дифференциальном усилителе, входящем в состав цепи 10 заряда/разряда, используются в качестве дифференциальной пары, причем к эмиттерам этих транзисторов Q6 и Q7 присоединен общий контур постоянного тока. Этот контур состоит из транзисторов Q9 и Q10 и резистора R5. Коллектор транзистора Q9 соединен с транзисторами Q6 и Q7, тогда как эмиттер этого транзистора соединен с потенциалом VSS земли через резистор R5. Потенциал базы транзистора Q9 определяется напряжением Vbe база-эмиттер транзистора Q10, включенного по схеме диода. При этом через транзистор Q9 течет постоянный ток.

Транзистор Q8, который включен между базой транзистора Q9 и потенциалом VSS земли, действует как ключ для включения/отключения контура постоянного тока в соответствии с управляющим сигналом PS. Пока управляющий сигнал PS, который подается на базу транзистора Q8, имеет уровень Н, транзистор Q8 npn-типа открыт. Поэтому база транзистора Q9, по существу, короткозамкнута транзистором Q8 на потенциал VSS земли, т.е. транзистор Q9 выключен. Контур постоянного тока не может функционировать. Когда же управляющий сигнал PS имеет уровень L, транзистор Q8 npn-типа заперт. В этом случае к базе транзистора Q9 приложено напряжение Vbe база-эмиттер транзистора Q10, так что транзистор Q9 открыт и контур постоянного тока находится в рабочем состоянии.

Коллекторы транзисторов Q1 и Q2 соединены с коллекторами транзисторов Q6 и Q7 соответственно. Транзисторы Q1 и Q2, включенные по схеме диода, зеркально соединены с транзисторами Q3 и Q4 соответственно. Эмиттеры транзисторов Q1-Q4 присоединены к источнику напряжения VCC соответственно через резисторы R1-R4. Напряжение VCC представляет собой заданное положительное напряжение, обеспечиваемое источником В напряжения.

Коллектор транзистора Q3 соединен с конденсатором С через транзистор Q13, включенный по схеме диода. Благодаря использованию схемы включения, зеркальной по току, такой же ток, что и ток J1 коллектора-эмиттера, текущий через транзистор Q1, течет также через транзистор Q3.

Транзистор Q11, включенный по схеме диода, подключен к коллектору транзистора Q4. Транзисторы Q11 и Q12 образуют зеркальную схему по току, тогда как коллектор транзистора Q12 подключен к конденсатору С. Эмиттеры транзисторов Q11 и Q12 заземлены через резисторы R6 и R7 соответственно. Благодаря использованию двухкаскадной схемы, зеркальной по току, такой же ток, что и ток J2 коллектора-эмиттера, текущий через транзистор Q2, течет также через транзистор Q12.

Конденсатор С заряжается или разряжается результирующим током J (≡J1-J2), который определяется током J1, поступающим от транзистора Q13, и током J2, подаваемым в транзистор Q12. Одна обкладка конденсатора С соединена с базой транзистора Q14, а его вторая обкладка заземлена.

Транзисторы Q14 и Q5 выполняют функции, аналогичные функциям соответственно транзисторов Q01 и Q02, показанных на фиг.2, образуя пару Дарлингтона. Более конкретно, база транзистора Q14 соединена с конденсатором С, его коллектор соединен с базой транзистора Q5, а его эмиттер соединен с выходным выводом OUT. Эмиттер транзистора Q5 соединен с источником напряжения VCC, а его коллектор соединен с выходным выводом OUT. Источник I3 тока, который включен между коллектором транзистора Q5 и потенциалом VSS земли, обеспечивает ток Ice в цепи коллектор-эмиттер транзистора Q5.

Дифференциальный усилитель, входящий в состав цепи 12 подзаряда, имеет такую же конфигурацию, что и описанный дифференциальный усилитель, входящий в состав цепи 10 заряда/разряда. Более конкретно, дифференциальный усилитель цепи 12 подзаряда содержит транзисторы Q15 и Q16, которые используются в качестве дифференциальной пары, и общий контур постоянного тока, связанный с эмиттерами этих транзисторов. Данный контур постоянного тока состоит из транзисторов Q18 и Q19 и резистора R8. Коллектор транзистора Q18 соединен с транзисторами Q15 и Q16, тогда как эмиттер этого транзистора соединен с потенциалом VSS земли через резистор R8. Потенциал базы транзистора Q18 определяется напряжением Vbe база-эмиттер транзистора Q19, включенного по схеме диода. При этом через транзистор Q18 течет постоянный ток.

Транзистор Q17, который включен между базой транзистора Q18 и потенциалом VSS земли, действует как ключ для включения/отключения контура постоянного тока в соответствии с управляющим сигналом PR. Пока управляющий сигнал PR, который подается на базу транзистора Q17, имеет уровень Н, транзистор Q17 npn-типа открыт. Поэтому база транзистора Q18, по существу, короткозамкнута транзистором Q17 на потенциал VSS земли, т.е. транзистор Q18 выключен. Контур постоянного тока не может функционировать. Когда же управляющий сигнал PR имеет уровень L, транзистор Q17 npn-типа заперт. В этом случае к базе транзистора Q18 приложено напряжение Vbe база-эмиттер транзистора Q19, так что транзистор Q18 открыт и контур постоянного тока находится в рабочем состоянии.

Коллекторы транзисторов Q1 и Q2 соединены с коллекторами транзисторов Q15 и Q16 соответственно. Таким образом, подобно тому, как это было описано выше, дифференциальный усилитель цепи 12 подзаряда использует блок 34 совместно с дифференциальным усилителем цепи 10 заряда/разряда.

База одного из транзисторов, входящих в дифференциальную пару цепи 10 заряда/разряда, а именно транзистора Q6, соединена с входным выводом IN, тогда как база другого транзистора этой пары (транзистора Q7) соединена с выходным выводом OUT. Поэтому, когда управляющий сигнал PS имеет уровень L и, следовательно, контур постоянного тока находится в рабочем состоянии, течет результирующий ток J, определяемый разностью между входным сигналом Vin и выходным напряжением Vout. При этом ток J заряжает или разряжает конденсатор С.

Выходное напряжение цепи 18 хранения напряжения (т.е. сигнал Vst напряжения) прикладывается к базе транзистора Q15 дифференциальной пары цепи 12 подзаряда, тогда как база транзистора Q16 этой пары соединена с выходным выводом OUT. Поэтому, когда управляющий сигнал PR имеет уровень L и соответственно контур постоянного тока находится в рабочем состоянии, течет результирующий ток J, определяемый разностью между сигналом Vst напряжения и выходным напряжением Vout. При этом ток J заряжает или разряжает конденсатор С. Тем самым осуществляется операция подзаряда.

Более конкретно, конденсатор заряжается, если Vin (или Vst) >Vout, и разряжается, если Vin (или Vst) <Vout. При таком построении с течением времени выходное напряжение Vout приближается к входному сигналу Vin в период семплирования и к сигналу Vst напряжения в период подзаряда.

Как уже упоминалось, на фиг.3 представлен случай, когда скорость заряда/разряда, обеспечиваемого цепью 12 подзаряда, превышает соответствующую скорость применительно к цепи 10 заряда/разряда. Более конкретно, эта скорость определяется полным током, который обеспечивается контуром постоянного тока, имеющимся в соответствующем дифференциальном усилителе цепей 10, 12 заряда/разряда и подзаряда. При этом каждый контур постоянного тока обеспечивает подачу тока, равного сумме токов J1 и J2, протекающих через транзисторы Q1 и Q2 соответственно. Следовательно, силу токов J1 и J2 можно уменьшить путем уменьшения тока, поступающего из контура постоянного тока цепи 10 заряда/разряда. В результате появляется возможность уменьшить ток J заряда/разряда конденсатора С и соответственно повысить устойчивость по отношению к шумам. С другой стороны, выходное напряжение Vout, соответствующее концу предшествующего периода семплирования, может быть быстро восстановлено путем установления большого тока, обеспечиваемого контуром пос