Устройство считывания заряда (варианты) и запоминающее устройство с матричной адресацией, снабженное таким устройством

Иллюстрации

Показать всеИзобретение относится к устройству считывания заряда и к энергонезависимому запоминающему устройству с пассивной матричной адресацией. Техническим результатом является улучшение сбалансированности по заряду, контроль выходного сигнала и обеспечение автоматического смещения в синфазном режиме, автоматическая коррекция смещения нулевого уровня. Устройство считывания заряда содержит два опорных средства по заряду, два псевдодифференциальных опорных считывающих усилителя (RSA1; RSA2) и псевдодифференциальный считывающий усилитель (SA). Другой вариант этого устройства предназначен для считывания зарядов с множества средств (701) хранения заряда и содержит, по меньшей мере, две пары опорных средств по заряду, два псевдодифференциальных опорных считывающих усилителя (RSA1; RSA2) и, по меньшей мере, два псевдодифференциальных считывающих усилителя (SA). Энергонезависимое запоминающее устройство с пассивной матричной адресацией содержит электрически поляризуемый диэлектрический запоминающий материал, обладающий гистерезисом, и описанную выше систему считывающих усилителей. 3 н. и 17 з.п. ф-лы, 10 ил.

Реферат

Область техники

Настоящее изобретение относится к устройству считывания заряда, содержащему опорные средства по заряду и систему считывающих усилителей (называемых также усилителями считывания). Устройство по изобретению преимущественно предназначено для считывания заряда с пассивно адресуемых средств хранения заряда. Изобретение относится также к устройству считывания заряда, предназначенному для считывания заряда с множества пассивно адресуемых средств хранения заряда.

Кроме того, изобретение относится к энергонезависимому запоминающему устройству с пассивной матричной адресацией, содержащему электрически поляризуемый диэлектрический запоминающий материал, обладающий гистерезисом, в частности ферроэлектрический или электретный материал. Этот запоминающий материал образует слой, контактирующий с первым массивом и со вторым массивом электродов адресации, взаимно параллельных в пределах массива. При этом электроды первого массива, которые образуют управляющие линии запоминающего устройства, расположены перпендикулярно электродам второго массива, образующим линии данных запоминающего устройства. В зонах скрещивания управляющих линий и линий данных в запоминающем материале задаются ячейки памяти с конденсатороподобной структурой. С использованием соответствующих управляющей линии и линии данных может быть осуществлена селективная адресация к каждой ячейке памяти для осуществления операции записи/считывания. Операция записи в ячейку памяти осуществляется путем придания этой ячейке требуемого состояния поляризации посредством приложения к ней напряжения по управляющей линии и линии данных, задающим указанную ячейку. Прилагаемое напряжение способно либо установить в ячейке памяти заданное состояние поляризации либо произвести переключение состояния поляризации данной ячейки. Операция считывания осуществляется путем приложения напряжения к ячейке памяти и детектирования, по меньшей мере, одного электрического параметра выходного тока на линии данных. При этом одно или более устройств считывания заряда согласно изобретению служит (служат) для определения указанных состояний поляризации ячеек памяти в процессе операции считывания.

Уровень техники

Ферроэлектрики, образующие, строго говоря, подкласс электретов, представляют собой электрически поляризуемые материалы, которые в отсутствие внешнего электрического поля обладают, по меньшей мере, двумя равновесными ориентациями вектора спонтанной поляризации и в которых вектор спонтанной поляризации может быть переключен между этими двумя ориентациями посредством приложения электрического поля. Эффект памяти, проявляемый материалами с подобными бистабильными состояниями остаточной поляризации, может быть использован в запоминающих устройствах. При этом одно из состояний поляризации рассматривается как представляющее логическую "1", а второе - логический "0". Типичные приложения с использованием пассивно адресуемой матричной памяти реализуются с применением двух массивов параллельных электродов, которые скрещиваются (обычно под прямым углом) с образованием матрицы зон скрещивания. Индивидуальный доступ к каждой такой зоне осуществляется электрическим путем, посредством селективного возбуждения соответствующего электрода с одного из краев матрицы. Между массивами электродов расположен ферроэлектрический материал, в котором образуются конденсатороподобные структуры. Благодаря этому зоны скрещивания способны функционировать в качестве ячеек памяти. Когда между двумя электродами создана разность потенциалов, ферроэлектрический материал в ячейке памяти подвергается воздействию электрического поля. В результате материал генерирует поляризационный отклик, который в общем случае следует кривой гистерезиса или ее части. Управляя направлением и величиной электрического поля, ячейки памяти можно привести в желаемое логическое состояние. Использование пассивной адресации в устройствах описанного типа обеспечивает простоту изготовления при высокой плотности зон скрещивания.

Параллельные электроды одного массива обычно именуются управляющими линиями, а электроды второго массива - линиями данных. Соответствующие электронные контуры обеспечивают выполнение драйверных операций и операций считывания (детектирования) в отношении матричной памяти за счет использования временной последовательности сигналов, соответствующих протоколу подачи напряжений во времени. Потенциалы на выбранных управляющих линиях и линиях данных контролируются таким образом, чтобы при осуществлении драйверных операций и операций считывания они были близки или совпадали с несколькими заданными уровнями потенциала. Линии данных, кроме того, подключены к контуру, который детектирует (считывает) заряды, текущие между линиями данных и ячейками памяти, подключенными к этим линиям данных, в течение определенной части указанной временной последовательности. Данный контур имеет в своем составе считывающие усилители.

Считывающие усилители обычно осуществляют сравнение поляризационного отклика ячеек памяти с некоторым опорным значением напряжения или заряда. Для формирования опорного значения могут быть использованы различные методы. В предположении, что условия считывания являются стабильными и предсказуемыми, вклад паразитных компонентов может быть в принципе устранен путем вычитания фиксированного заряда из значения, зарегистрированного считывающим усилителем во время цикла считывания. Однако во многих случаях значительный уровень и непостоянство шумовых составляющих делают такой подход неприемлемым. В дополнение к различиям между ячейками памяти в одном запоминающем устройстве, обусловленным допусками на их изготовление, возможны значительные вариации в отношении усталостных характеристик и "импринтинга". Кроме того, паразитный ток, ассоциированный с активной линией данных, может зависеть от реальных логических состояний неадресованных ячеек памяти на этой линии данных. В связи с этим для решения рассматриваемой проблемы уровни опорного напряжения целесообразно получить от соседних ячеек памяти.

Контур опорного напряжения, используемый при определении состояния поляризации ферроэлектрического конденсатора, описан в патенте США №5218566. Известный контур содержит пару ферроэлектрических конденсаторов, которые имеют взаимно противоположные направления поляризации. Заряды, хранящиеся на этих конденсаторах, считываются соответствующими считывающими конденсаторами. За счет закорачивания считывающего конденсатора можно получить опорное напряжение, которое может быть использовано для сравнения сигналов от других ячеек памяти, т.е. сигналов, генерированных другими ферроэлектрическими конденсаторами. Аналогичный подход, описанный в патенте США №5999439, предусматривает использование мультиплексирующего считывающего усилителя для сравнения данных, хранящихся в ячейках памяти, с опорным напряжением, генерируемым парой опорных ячеек памяти. Однако оба известных контура содержат активно адресуемую матричную память, что делает требования к используемым в них считывающим усилителям менее критичными. Уровень входных сигналов в пассивно адресуемой матричной памяти является существенно более низким, и ни в одном из названных патентов не приводится решение данной проблемы.

В патенте США №5572474 описан псевдодифференциальный считывающий усилитель, который считывает состояние ячейки памяти в соответствующем массиве путем сопоставления с опорной ячейкой памяти, находящейся в известном состоянии. Используемый считывающий усилитель имеет входной каскад, подключенный к ячейке памяти из анализируемого массива. Этот каскад формирует сигналы, подаваемые на дифференциальный каскад, который генерирует выходные сигналы. Входной каскад содержит каскодные схемы, включенные на опорной стороне и на стороне массива и образованные взаимно согласованными компонентами для того, чтобы исключить влияние непостоянства внешних факторов, включая схемные и температурные факторы, на выходной дифференциальный сигнал. Однако известный контур основан на эффекте использования усиления МОП-транзистора и не обеспечивает автоматической коррекции смещения нулевого уровня и высококачественного баланса по заряду.

Патент США №5638322 описывает псевдодифференциальный считывающий усилитель, обеспечивающий эффективное подавление синфазного шума. Считывающий усилитель подключается через цепь, связанную с массивом ячеек памяти, и генерирует выходной сигнал, характеризующий состояние соответствующих ячеек памяти. При этом считывающий усилитель содержит нагрузочное устройство, подключенное к цепи, связанной с массивом, через узел массива, опорное нагрузочное устройство, подключенное к опорной цепи через опорный узел, дифференциальный каскад, имеющий первый вход, связанный с опорным узлом, второй вход, связанный с узлом массива, и выходную цепь, генерирующую выходной сигнал. Считывающий усилитель дополнительно содержит балансное устройство, связанное с опорным узлом, для компенсации изменения в уровне сигнала, обусловленного шумовым событием на узле массива, и для сокращения тем самым задержки в отклике считывающего усилителя, когда имеет место изменение состояния ячейки памяти. Однако запоминающим элементом в известной схеме является полевой МОП-транзистор, причем в указанном патенте не поясняется, каким образом можно построить псевдодифференциальный считывающий усилитель, обладающий коэффициентом усиления и точностью, отвечающими требованиям ферроэлектрической памяти.

Раскрытие изобретения

Таким образом, основная задача, на решение которой направлено настоящее изобретение, состоит в создании устройства считывания заряда с системой считывающих усилителей, специально рассчитанного на использование совместно с полимерным ферроэлектрическим запоминающим материалом в форме тонкой пленки. Изобретение направлено также на создание энергонезависимого запоминающего устройства с пассивной матричной адресацией, использующего подобную систему считывающих усилителей.

Конкретной задачей, решаемой настоящим изобретением, является создание устройства считывания заряда с системой считывающих усилителей, обладающего улучшенной сбалансированностью по заряду, в котором опорное напряжение генерируется с использованием пары ферроэлектрических конденсаторов, имеющих взаимно противоположные состояния поляризации.

Кроме того, задача, решаемая настоящим изобретением, заключается в создании системы считывающих усилителей, которая будет способна контролировать выходной сигнал в синфазном режиме и обеспечивать автоматическое смещение в синфазном режиме и автоматическую коррекцию смещения нулевого уровня.

Решение перечисленных задач, а также новые признаки и преимущества достигнуты согласно изобретению с помощью нового устройства считывания заряда. Устройство по изобретению содержит пару опорных средств, состоящую из параллельно соединенных первого и второго опорных средств по заряду. Опорные средства по заряду выполнены аналогично средству хранения заряда, т.е. представляют собой конденсаторы, например ферроэлектрические (в том случае, когда средство хранения заряда представляет собой ферроэлектрический конденсатор). Первое опорное средство по заряду имеет поляризацию, противоположную поляризации второго опорного средства по заряду. При этом первое и второе опорные средства по заряду и средство хранения заряда имеют общий входной узел. Устройство по изобретению содержит далее первый и второй псевдодифференциальные опорные считывающие усилители, каждый из которых соединен с выходным узлом соответствующего опорного средства по заряду через один из входных узлов, совместно используемых указанными опорными считывающими усилителями, и выполнен с возможностью генерирования выходного опорного сигнала, подаваемого на общий опорный узел.

В состав устройства входит также псевдодифференциальный считывающий усилитель, имеющий первый вход, соединенный с общим опорным узлом для приема общего опорного входного сигнала, и второй вход для приема выходного сигнала от средства хранения заряда. Данный псевдодифференциальный считывающий усилитель выполнен с возможностью генерирования дифференциального положительного или отрицательного выходного сигнала, который соответствует интегрированной разности зарядов в конце цикла считывания между активной линией данных и входными узлами, связанными с опорными средствами по заряду. При этом выходной сигнал данного псевдодифференциального считывающего усилителя преобразуется в цифровой (логический) уровень, характеризующий состояние поляризации средства хранения заряда в зависимости от знака указанного выходного сигнала.

Оба псевдодифференциальных опорных считывающих усилителя и псевдодифференциальный считывающий усилитель в устройстве считывания заряда предпочтительно являются идентичными псевдодифференциальными считывающими усилителями.

Каждый считывающий усилитель (т.е. каждый псевдодифференциальный считывающий усилитель и каждый опорный псевдодифференциальный считывающий усилитель) предпочтительно содержит дифференциальную пару входных транзисторов, соединенную с парой каскодных транзисторов, и пару транзисторов, обеспечивающих смещение тока, генерируемого источником тока, и подключенных к паре транзисторов, включенных по каскодной схеме. Использование пар каскодных транзисторов в обоих случаях обеспечивает повышение коэффициента усиления разомкнутой цепи считывающего усилителя. При этом входные транзисторы могут являться транзисторами с р-каналом, а транзисторы, обеспечивающие смещение тока, - транзисторами с n-каналом или наоборот.

В предпочтительном варианте выполнения устройства каждый из указанных считывающих усилителей содержит полусбалансированный сдвоенный вход и сбалансированный сдвоенный выход. Он предпочтительно содержит, кроме того, синфазную цепь обратной связи на основе переключаемого конденсатора для управления выходным напряжением в синфазном режиме, а также средства для обеспечения автоматического смещения для переключаемого конденсатора в синфазном режиме, интегральную защелку положительной обратной связи и средства автоматической коррекции смещения нулевого уровня.

Решение перечисленных задач, а также новые признаки и преимущества достигнуты согласно изобретению и с помощью другого варианта устройства считывания заряда. В данном варианте устройство считывания заряда содержит, по меньшей мере, две пары опорных средств, каждая из которых состоит из первого и второго опорных средств по заряду. Как и в первом варианте устройства, данные средства выполнены как опорные конденсаторы, аналогичные средствам хранения заряда, причем в каждой паре опорных средств первое опорное средство по заряду имеет поляризацию, противоположную поляризации второго опорного средства по заряду. Каждая из пар опорных средств по заряду имеет общий входной узел и пару общих выходных узлов, соединенных соответственно с первым и со вторым опорными средствами по заряду в каждой из пар опорных средств по заряду, а каждый общий входной узел, по меньшей мере, двух пар опорных средств по заряду соединен также, по меньшей мере, с двумя средствами хранения заряда.

Устройство по изобретению содержит далее первый и второй псевдодифференциальные опорные считывающие усилители, соединенные соответственно с первым общим выходным узлом и со вторым общим выходным узлом опорных средств по заряду. Данные считывающие усилители выполнены с возможностью генерирования выходных опорных сигналов, подаваемых на общий опорный узел.

В состав устройства входят также, по меньшей мере, два псевдодифференциальных считывающих усилителя. Каждый из них имеет первый вход, соединенный с общим опорным узлом для приема общего опорного входного сигнала, и второй вход, соединенный с общим выходным узлом одного из, по меньшей мере, двух средств хранения заряда для приема выходного сигнала от соответствующего средства хранения заряда. Каждый из данных псевдодифференциальных считывающих усилителей выполнен с возможностью генерирования дифференциального положительного или отрицательного выходного сигнала, который соответствует интегрированной разности зарядов в конце цикла считывания между активной линией данных и входными узлами, связанными с опорными средствами по заряду. Данный выходной сигнал каждого из данных псевдодифференциальных считывающих усилителей преобразуется в цифровой (логический) уровень, характеризующий состояние поляризации средства хранения заряда в зависимости от знака разностного сигнала.

В данном варианте осуществления изобретения общие входные узлы образуют части электродов, соответствующих управляющим линиям в массиве ячеек памяти с матричной адресацией для хранения заряда. Общие выходные узлы опорных средств по заряду образуют пару опорных электродов, соответствующих опорным линиям данных, а общие выходные узлы средств хранения заряда образуют электроды, соответствующие линиям данных указанного массива с матричной адресацией. Каждый из опорных электродов поставлен в соответствии с первым или со вторым псевдодифференциальным опорным считывающим усилителем, а каждый из остальных электродов, соответствующих линиям данных, поставлен в соответствии с одним из псевдодифференциальных считывающих усилителей. При этом в цикле считывания состояние поляризации соответствующих выбранных ячеек памяти может быть детектировано либо в последовательном либо в параллельном режимах и сопоставлено с опорным значением.

Кроме того, в данном варианте устройство считывания заряда предпочтительно выполнено в виде субблока в блоке, содержащем более одного устройства считывания заряда указанного типа. При этом опорные считывающие усилители и считывающие усилители субблока связаны с соответствующим количеством электродов, соответствующих линиям данных в массиве с матричной адресацией, а пара опорных линий данных субблока распределена среди линий данных указанного массива.

Альтернативно устройство содержит мультиплексор, связанный с электродами, соответствующими линиям данных массива с матричной адресацией, а заданное количество последовательных линий данных в массиве задает сегмент общего количества электродов, соответствующих управляющим линиям указанного массива. Это заданное количество линий данных равно количеству псевдодифференциальных считывающих усилителей в устройстве считывания заряда. В этом варианте в каждом сегменте управляющей линии пара электродов, соответствующих опорным линиям данных, расположена смежно с электродами, соответствующими линиям данных, и соединяет пары опорных средств по заряду. В результате ячейки памяти, предназначенные для хранения заряда и расположенные на одном электроде, соответствующем управляющей линии в указанном сегменте управляющей линии, могут быть считаны параллельно при аналогичном последовательном считывании сегментов управляющей линии путем выполнения соответствующего протокола адресации и мультиплексирования электродов, соответствующих линиям данных в пределах сегмента управляющей линии, для параллельного подключения указанных электродов к соответствующим псевдодифференциальным считывающим усилителям устройства считывания заряда.

Кроме того, решение перечисленных задач, а также новые признаки и преимущества достигнуты согласно изобретению с помощью энергонезависимого запоминающего устройства с матричной адресацией. Данное устройство характеризуется тем, что в его состав входит устройство считывания заряда, представляющее собой систему псевдодифференциальных считывающих усилителей. Указанная система содержит, по меньшей мере, один субблок, который содержит, по меньшей мере, один псевдодифференциальный считывающий усилитель для определения состояния поляризации, по меньшей мере, одной ячейки памяти при выполнении операции считывания и два псевдодифференциальных опорных считывающих усилителя для определения состояния поляризации двух опорных ячеек памяти при выполнении операции считывания. Данный, по меньшей мере, один считывающий усилитель связан с указанными двумя псевдодифференциальными опорными считывающими усилителями через общий узел.

В предпочтительном варианте выполнения запоминающего устройства согласно изобретению указанный, по меньшей мере, один субблок содержит множество указанных считывающих усилителей для определения при выполнении операции считывания состояния поляризации множества ячеек памяти.

В соответствии с другим предпочтительным вариантом указанный первый и второй опорные считывающие усилители предпочтительно выполнены с возможностью генерировать сигнал, соответствующий среднему выходных сигналов первой и второй опорных ячеек памяти, и подавать его на указанный общий узел. При этом, по меньшей мере, один указанный считывающий усилитель, связанный с указанным общим узлом, выполнен с возможностью осуществлять сравнение выходного сигнала на общем узле с выходным сигналом ячейки памяти.

Представляется желательным, чтобы указанные, по меньшей мере, один считывающий усилитель и, по меньшей мере, один опорный считывающий усилитель были выполнены с идентичными усилительными контурами. В этом случае указанные идентичные усилительные контуры предпочтительно имеют опорную сторону и сторону массива, причем опорная сторона выполнена как зеркальное отражение стороны массива.

В другом предпочтительном варианте запоминающего устройства система псевдодифференциальных считывающих усилителей содержит множество указанных субблоков. В этом случае каждый субблок предпочтительно содержит множество считывающих усилителей для считывания состояния поляризации соответствующего количества ячеек памяти.

Краткое описание чертежей

Далее настоящее изобретение будет описано более подробно на примерах конкретных вариантов его осуществления и со ссылками на прилагаемые чертежи.

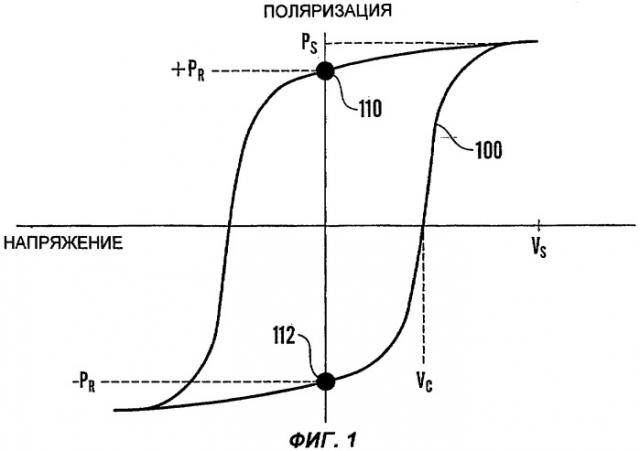

На фиг.1 схематично изображена кривая гистерезиса для ферроэлектрического запоминающего материала.

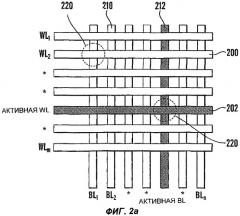

Фиг.2а иллюстрирует принцип пассивной матричной адресации при использовании скрещивающихся электродов.

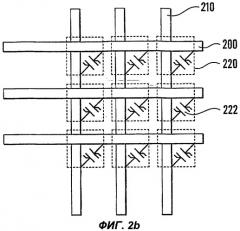

Фиг.2b представляет собой принципиальную схему пассивной матрицы с ячейками памяти, содержащими ферроэлектрический материал и локализованными в зонах взаимного наложения скрещивающихся электродов.

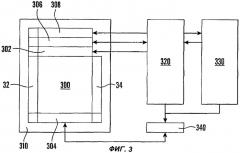

Фиг.3 - блок-схема запоминающего устройства согласно изобретению.

На фиг.4 приведена электрическая схема предпочтительного варианта псевдодифференциального считывающего усилителя, входящего в состав запоминающего устройства по изобретению.

Фиг.5 представляет собой блок-схему системы псевдодифференциальных считывающих усилителей, входящей в состав запоминающего устройства по изобретению.

Фиг.6 - блок-схема устройства считывания заряда согласно изобретению.

На фиг.7 представлено устройство считывания заряда согласно изобретению, входящее в состав запоминающего устройства с пассивной матричной адресацией, аналогичного показанному на фиг.2а, со средствами хранения заряда, включенными между скрещивающимися электродами.

Фиг.8 иллюстрирует первый вариант выполнения пассивно адресуемой матричной памяти согласно изобретению, которая включает в себя устройство считывания заряда согласно изобретению.

Фиг.9 иллюстрирует второй вариант выполнения пассивно адресуемой матричной памяти согласно изобретению, которая включает в себя устройство считывания заряда согласно изобретению.

Осуществление изобретения

Перед тем как настоящее изобретение будет рассмотрено со ссылками на предпочтительные варианты его осуществления, предлагается краткое описание его основных принципов, касающихся преимущественно гистерезиса в ферроэлектрических материалах и структуры ферроэлектрических запоминающих устройств с матричной адресацией.

На фиг.1 приведена кривая 100 гистерезиса, которая из соображений удобства построена с откладыванием по оси абсцисс не напряженности электрического поля, а напряжения. Как показано на фиг.1, ферроэлектрический материал, обладающий гистерезисом, изменяет направление своей поляризации при приложении к нему напряжения VC, создающего электрическое поле, которое превосходит коэрцитивное поле. Значения напряжения рассчитываются путем умножения значений напряженности на толщину слоя ферроэлектрического материала. Поляризация PS насыщения достигается каждый раз, когда ячейка памяти, расположенная в зоне скрещивания электродов, подвергается воздействию номинального переключающего напряжения VS. Как только приложенное напряжение будет снято, поляризация возвращается соответственно к одному из двух состояний РR и -PR остаточной поляризации, которые дополнительно обозначены как точки 110 и 112 соответственно на гистерезисной кривой.

На фиг.2а изображена матрица, образованная ортогональными скрещивающимся электродами. В соответствии с принятой терминологией горизонтальные электроды (строки матрицы) будут далее именоваться управляющими линиями 200 (или WL - word lines), а вертикальные электроды (столбцы матрицы) будут далее именоваться линиями 210 данных (или BL - bit lines). При осуществлении драйверных операций и операций считывания производится активация выбранной управляющей линии 202, а также одной или более линий 212 данных. При этом следует выбирать прилагаемые напряжения достаточно большими для того, чтобы обеспечить переключение заданной ячейки 220 памяти (см. фиг.2b) с целью либо задания определенного направления поляризации (запись) либо для определения направления поляризации в данной ячейке (считывание). Слой ферроэлектрического материала, находящийся между электродами 200, 210, функционирует как ферроэлектрический конденсатор 222. Таким образом, ячейка 220 выбирается путем задания таких потенциалов на соответствующих данной ячейке управляющей линии 202 и линии 212 данных (на активных линиях), что разность этих потенциалов равняется номинальному напряжению Vs переключения. В то же время потенциалы на многочисленных управляющих линиях 200 и линиях 210 данных, которые, скрещиваясь, задают неадресуемые ячейки 220 памяти, должны контролироваться таким образом, чтобы возмущающие напряжения на данных ячейках 220 памяти удерживались на минимальном уровне.

Представляется целесообразным кратко рассмотреть со ссылкой на фиг.3 общие принципы действия и структуру запоминающего устройства с пассивной матричной адресацией. В качестве примера данное устройство будет рассматриваться как ферроэлектрическая память, хорошо известная специалистам в данной области техники. В этом случае в соответствии с изобретением псевдодифференциальные считывающие усилители будут использоваться для считывания состояний поляризации ферроэлектрических ячеек памяти.

Фиг.3 иллюстрирует в форме упрощенной блок-схемы структуру и функциональные элементы ферроэлектрического запоминающего устройства с матричной адресацией. Блок 310 памяти содержит массив 300 ячеек памяти, декодеры 32 и 302 строк и столбцов соответственно, считывающие усилители 306, защелки 308 данных и избыточные управляющие линии и линии данных 304, 34. Массив 300 ячеек памяти образует матрицу управляющих линий 200 и линий 210 данных. Декодеры 32, 302 строк и столбцов декодируют адреса ячеек памяти, тогда как считывание осуществляется посредством считывающих усилителей 306. Защелки 308 данных удерживают считанные данные до тех пор, пока их часть или все данные не будут перенесены в управляющий (логический) блок 320. Данные, считанные из блока 310 памяти, будут характеризоваться некоторой частотой появления ошибок по битам, которая может быть уменьшена путем замены дефектных управляющих линий и линий данных в запоминающей матрице 300 на избыточные управляющие линии и линии данных 304, 34. Для того чтобы осуществлять обнаружение ошибок, блок 310 памяти может иметь поля данных, содержащих код с исправлением ошибок.

Управляющий блок 320 обеспечивает цифровой интерфейс для блока 310 памяти и осуществляет управление операциями записи и считывания в запоминающей матрице 300. В управляющем блоке 320 имеются также средства инициализации памяти и логические средства для замещения дефектных управляющих линий и линий данных избыточными управляющими линиями и линиями данных. Контроллер 330 связывает управляющий блок 320 с внешними шинами. Может быть предусмотрен также генератор 340 подкачки заряда для генерирования некоторых из напряжений, которые необходимы для выполнения операций записи и считывания в ячейках памяти.

Описанные выше конкретные и предпочтительные варианты записи данных в ферроэлектрические ячейки памяти и считывания данных из этих ячеек далее будут описаны применительно к более общей проблеме считывания слабых сигналов, которые имеют место при считывании из ячеек памяти в запоминающих устройствах с пассивной матричной адресацией. Особенности такого считывания наиболее заметно проявляются в различиях в уровнях фоновых токов, текущих в активной линии данных, и заряда, поступающего из считываемой активной ячейки памяти.

Общее решение проблемы неточного усиления очень малых входных сигналов, предлагаемое настоящим изобретением, состоит в использовании переключаемого конденсатора, обеспечивающего высокий коэффициент усиления, а также в автоматической коррекции смещения нулевого уровня и в обеспечении отличного баланса зарядов. Обеспечение этих свойств предполагает использование пары ферроэлектрических конденсаторов, которые имеют взаимно противоположные состояния поляризации. Поскольку в этом случае достигается более легкая компенсация фоновых токов, появляется возможность использовать одностороннее (несимметричное) опорное напряжение, генерируемое опорными ячейками памяти, для того чтобы облегчить сравнение сигналов, генерируемых другими ферроэлектрическими конденсаторами (ячейками памяти).

Далее со ссылками на фиг.4 и 5 будет более подробно описано устройство считывания заряда с системой считывающих усилителей, которое используется с запоминающим устройством согласно изобретению. На фиг.4 приведена электрическая схема псевдодифференциального считывающего усилителя, который используется в системе считывающих усилителей согласно изобретению, представленной на фиг.5. При этом на фиг.5 данные считывающие усилители представлены в виде блоков 500, 502, 504 операционных усилителей. Блоки 502 и 504 операционных усилителей на фиг.5 соответствуют двум опорным считывающим усилителям, включенным параллельно. Две опорные линии 508, 510 данных подключены к двум входным узлам INR, совместно используемым двумя опорными считывающими усилителями 502, 504.

Непосредственно перед выполнением операции считывания в один из двух элементов 514а; 516а опорной линии данных записывается логическая 1, тогда как в другой элемент записывается логический 0. Благодаря этому во время выполнения операции считывания результирующее напряжение на узле CHREF будет соответствовать среднему значению состояний логической 1 и логического 0. Результирующий, так называемый опорный заряд на узле CHREF далее усиливается основным считывающим усилителем 500. Коэффициент усиления цепи между узлом CHREF и выходным дифференциальным сигналом Voutdiff=SAOUTP-SAOUTM задан таким, что уровень опорного сигнала, задаваемый дифференциальным сигналом Voutdiff, будет приводить к смещению заряда, поданного активным элементом на узел INR, на величину, равную половине разности напряжений, соответствующих логической 1 и логическому 0. В предположении о хорошем соответствии между емкостью линии данных и зарядом, снимаемым с ферроэлектрика, напряжение Voutdiff, соответствующее среднему значению напряжений, соответствующих логической 1 и логическому 0 на активной линии BL данных, будет симметричным относительно 0 В. В этом случае запоминающий элемент в состоянии, соответствующем логической 1, будет иметь Voutdiff>0, а запоминающий элемент в состоянии, соответствующем логическому 0, будет иметь Voutdiff<0. Далее напряжение Voutdiff защелкивается для того, чтобы определить логическое состояние, соответствующее считываемому биту данных.

Должно быть понятно, что система считывающих усилителей, представленная на фиг.5, может содержать большое количество (n) считывающих усилителей 500. Поэтому элемент 530 на фиг.5 представляет емкость нагрузки неизображенных n-1 считывающих усилителей, идентичных считывающему усилителю 500. В реальном варианте система считывающих усилителей, которая иллюстрируется фиг.5, содержит единственный узел CHREF, связанный, например, с 32 активными считывающими усилителями 500. Иными словами, на фиг.5 представлен блок в виде одного узла CHREF, связанного с n активными считывающими усилителями 500. При этом должно быть понятно, что n может быть выбрано достаточно большим, так что система считывающих усилителей, используемая в устройстве по изобретению, может включать в себя очень большое количество считывающих усилителей 500, совместно использующих один узел CHREF, и два опорных считывающих усилителя 502, 504. Кроме того, каждое запоминающее устройство может содержать множество блоков, соответствующих системам считывающих усилителей, идентичным представленной на фиг.5.

Далее будет рассмотрена представленная на фиг.4 электрическая схема псевдодифференциального считывающего усилителя, подобного одному из операционных усилителей 500, 502, 504 по фиг.5. Должно быть понятно, что контур, показанный на фиг.4, представлен довольно схематично и при этом включает некоторые паразитные элементы, которые не участвуют в выполнении его основных функций. В частности, в качестве таких паразитных элементов могут быть указаны диоды 470а, 470b, 470с, 470d, 470e, 470f, которые связаны с потенциалом земли соответственно в точках 460а, 460b, 460с, 460d, 460e, 460f и которые не вносят никакого существенного вклада в работу представленного на фиг.4 считывающего усилителя как такового.

В соответствии с предпочтительным вариантом настоящего изобретения проблема присутствия значительных фоновых токов при малых входных сигналах решается применением псевдодифференциальных считывающих усилителей, которые имеют хорошо сбалансированную и симметричную конструкцию. Это станет понятно из дальнейшего описания схемы псевдодифференциального считывающего усилителя, представленной на фиг.4. Следует отметить, что в этом описании обозначения различных узлов, показанных на данной фигуре, будут использоваться также для ссылки на напряжения, имеющиеся на этих узлах.

На затвор транзистора 400, включенного в цепь источника тока, подано напряжение Vbiasp смещения. Исток этого транзистора 400, который относится к р-типу, подключен к источнику напряжения по линии V33. Со стока транзистора 400 ток смещения поступает на соединенные истоки транзисторов 402, 404 р-типа, образующих дифференциальную пару. Для того чтобы способствовать уменьшению размеров электронных компонентов, компоненты с р-каналом совместно используют карманы n-типа во всех случаях, когда это совместимо с требованиями по обеспечению заданного смещения. Таким образом, транзисторы 400, 402 и 404 имеют общую подложку, присоединенную к линии V33. Входные линии INP и INM подсоединены соответственно к затворам транзисторов 402 и 404, образующих входную дифференциальную пару. Истоки транзисторов 402 и 404 связаны со стоками соответственно транзисторов 410 и 412 каскодной схемы. Данная каскодная схема значительно улучшает коэффициент усиления разомкнутой цепи считывающего усилителя. Аналогичным образом транзисторы 438 и 440 с n-каналом, обеспечивающие смещение тока, генерируемого источником тока, подключены соответственно к каскодным транзисторам 434 и 436 с n-каналом. Такое включение также повышает коэффициент усиления разомкнутой цепи считывающего усилителя.

Выходной сигнал считывающего усилителя определяется как разность напряжений между узлами OUTP и OUTM. Данный разностный сигнал (OUTP-OUTM) представляет собо