Энергонезависимый многопороговый триггер кмоп с управлением утечкой

Иллюстрации

Показать всеИзобретение относится к многопороговым цепям КМОП и к устройствам, функционирующим в активном и ждущем режимах. Интегральная цепь содержит мультипороговый триггер КМОП (МПКМОП), комбинирующий цепи КМОП с низким пороговым уровнем (LVT) с цепями КМОП с высоким пороговым уровнем (HVT). Цепи LVT составляют основную часть цепей тракта сигнала триггера для гарантии высокой производительности триггера. Триггер содержит далее цепи HVT для снижения токов утечки в цепях с низким пороговым уровнем, когда триггер находится в ждущем режиме. Представлены однофазный триггер и двухфазный триггер. Каждый из триггеров реализован с ведущим и ведомым регистрами. Данные хранятся в либо в ведущем, либо в ведомом регистре в зависимости от фазы или фаз сигналов синхронизации. В альтернативном случае перед ведущим регистром может быть включен мультиплексор для управления трактом входного сигнала в течение ждущего и активного режимов триггера и для обеспечения второго тракта входного сигнала для тестирования. 6 н. и 18 з.п. ф-лы, 10 ил.

Реферат

Область техники, к которой относится изобретение

Данное изобретение относится к области интегральных цепей на комплементарных металл-оксидных полупроводниках (КМОП). Более конкретно данное изобретение относится к многопороговым цепям КМОП и устройствам, способным функционировать в активном и ждущем режимах.

Уровень техники

Современные интегральные цепи (IC) разрабатываются с целью обеспечения реализации огромного количества функций на малой площади. IC очень большого масштаба способны осуществлять практически все функции, требуемые во многих электронных устройствах. Возможность совмещать огромные мощности обработки с выполнением множества функций делают IC практически незаменимыми в портативных электронных устройствах. Такие портативные электронные устройства, как ноутбуки, карманные персональные компьютеры и сотовые телефоны, требуют использования IC для получения возможности выполнения задач высокой сложности. Разработчики портативных электронных устройств, в свою очередь, вынуждены наращивать функциональность таких устройств при уменьшении их физических размеров.

Одним из способов повышения функциональности портативного электронного устройства является увеличение числа функций, выполняемых IC. Однако для сохранения приемлемых размеров IC разработчики IC должны уменьшать физические размеры транзисторов, используемых в цепях. Размеры используемых в типичных IC транзисторов ограничиваются технологиями, используемыми для их создания. В настоящее время транзисторы IC имеют размеры субмикронного порядка. Например, в субмикронной технологии IC длина (L) металл-оксидного полупроводникового (МОП) транзистора может быть менее 1 мкм.

Физический размер портативных электронных устройств не может быть уменьшен простым повышением функциональности IC. Повышение сложности и функциональности IC приводит к пропорциональному увеличению энергопотребления IC. Так как большая часть портативных электронных устройств запитывается от батарей, энергопотребление играет важнейшую роль в определении полезного времени функционирования портативного устройства. Повышением емкости батареи можно добиться увеличения времени функционирования портативного устройства, однако данный вариант вступает в конфликт с желанием уменьшить физические размеры и вес портативных устройств. Таким образом, существует потребность в снижении энергопотребления портативными электронными устройствами. Снижение энергопотребления позволит разработчику использовать батареи меньшей емкости, имеющие, как правило, меньшие размеры.

Электронные устройства могут также сохранять электроэнергию посредством реализации ждущего режима в некоторых либо всех цепях устройства. Например, устройство пейджинга может находиться в ждущем режиме в течение определенных периодов времени и осуществлять мониторинг пейджинговых сообщений только в течение присвоенных ему временных слотов. Таким же образом мобильный телефон может переводить некоторые части своего устройства в ждущий режим в те моменты, когда питание включено, но связь не осуществляется. Электронные устройства, как правило, осуществляют выбор между активным и ждущим режимами в зависимости от потребностей устройства. Можно утверждать, что практически все портативные электронные устройства должны содержать ждущий режим. Например, устройства пейджинга, телефоны, ноутбуки, устройства беспроводной связи, карманные персональные компьютеры и другие электронные устройства могут содержать ждущий режим, при котором по меньшей мере часть цепей переводится в режим пониженного энергопотребления.

Таким образом, перед разработчиками IC стоит задача повышения сложности IC при одновременном снижении энергопотребления. Одним из способов снижения энергопотребления IC является разумный выбор типа технологии, используемой при реализации IC. IC может быть реализована с использованием различных технологий. Например, цепи могут быть реализованы с использованием биполярных транзисторов, транзисторов на металл-оксидных полупроводниках (МОП), n-МОП транзисторов, а также комплементарных МОП (КМОП) транзисторов. Реализация на КМОП транзисторах предпочтительна при разработке цифровых устройств, так как затвор КМОП теоретически не потребляет электроэнергию в статическом состоянии.

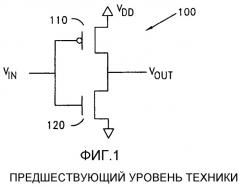

Схема типичного КМОП инвертора 100 приведена на Фиг. 1. Технология КМОП использует цепи как n-каналов, так и p-каналов в одном чипе. Исток n-канального МОП транзистора 120 подключен к цепи обратного напряжения, которую можно также назвать общим проводом, опорной цепью по напряжению, цепью обратного напряжения либо заземлением. Можно считать, что цепь обратного напряжения может быть также одной из линий питания. Цепь обратного напряжения обеспечивает подключение к соответствующей линии электропитания, Vdd. Цепь обратного напряжения может быть изолирована от других цепей либо может быть общей цепью обратного напряжения для других цепей. Затвор n-канального МОП транзистора 120 электрически соединен с затвором p-канального МОП транзистора 110. Подключение с общим затвором служит также входом для КМОП инвертора 100. Исток p-канального МОП транзистора 110 электрически соединен с линией электропитания Vdd. Сток p-канальной цепи 110 электрически соединен со стоком n-канальной цепи 120. Подключение с общим стоком является выходом инвертора 100.

Принцип работы инвертора 100 относительно прост. Когда входной сигнал, Vin, имеет низкий уровень, n-канальный транзистор 120 не проводит ток, то есть закрыт. Однако p-канальная цепь 110 работает таким образом, что напряжение источника питания, Vdd, подводится к выходу, Vout, инвертора 100. В обратном случае, когда входной сигнал, Vin, имеет высокий уровень, p-канальный транзистор 110 не проводит ток, а n-канальная цепь 120 открыта, закорачивая выход инвертора 100 на цепь обратного напряжения. При каждом из двух состояний инвертора 100 один транзистор из комплементарной пары транзисторов является непроводящим. Непроводящий транзистор создает высокий импеданс между линией электропитания и цепью обратного напряжения, ограничивая таким образом рассеивание мощности инвертором 100 при статическом состоянии выхода. Уровень рассеивания мощности в статическом состоянии в значительной степени определяется током утечки закрытого транзистора.

Мощность потребляется КМОП инвертором 100, как и цепями КМОП в целом, при переключении цепи между логическими состояниями. Рассеивание мощности инвертором 100 пропорционально объему энергии, обеспечиваемому емкости нагрузки на каждом уровне перехода. Таким образом, рассеивание мощности КМОП инвертором 100 пропорционально значению CL·Vdd2·f. В данном выражении CL представляет собой емкость нагрузки, Vdd - напряжение источника питания, а f - скорость изменения данных.

Можно считать, что для синхронизируемых последовательных цепей рассеиваемая мощность пропорциональна частоте синхронизации. Хотя частота синхронизации в высокой степени зависит от требований к пропускной способности по передаче данных, сигнал синхронизации для некоторого числа цепей может быть остановлен на периоды времени, в течение которых активность этих цепей не требуется. Данные периоды отсутствия активности могут содержать ждущий режим, при котором часть IC отключается от питания для экономии электроэнергии. В значительной степени частота сигнала синхронизации не может быть снижена для уменьшения энергопотребления без ущерба для возможностей обработки.

Видимо, наиболее значительное снижение энергопотребления КМОП может быть достигнуто снижением напряжения питания. Как следует из приведенной выше формулы, рассеивание мощности пропорционально квадрату напряжения питания, Vdd. Таким образом, снижение напряжения питания обеспечивает большую экономию электроэнергии, нежели сравнимое снижение рабочей частоты или емкости нагрузки.

Однако снижение напряжения питания приводит к ухудшению параметров задержки распространения в цепях КМОП. Если напряжение питания снижается до порогового напряжения транзистора МОП, Vth, задержка распространения возрастает. Возрастание задержки распространения в значительной степени снижает возможность функционирования затвора КМОП в высокоскоростных цепях.

Одним из способов снижения задержки распространения и, таким образом, повышения работоспособности затвора в высокоскоростных цепях является снижение порогового напряжения, Vth, МОП транзисторов. Однако снижение порогового напряжения приведет к увеличению подпорогового тока утечки МОП транзистора. Результатом станет нарастание статического тока, а следовательно, рассеивания мощности в течение статического периода.

Энергопотребление цепей КМОП может быть также снижено без существенного ухудшения скоростных характеристик цепи внедрением как транзисторов с высоким пороговым напряжением, так и транзисторов с низким пороговым напряжением в одной и той же конструкции IC. Такие цепи получили название многопороговых КМОП (МПКМОП) цепей.

В предыдущих вариантах осуществления МПКМОП цепи с низким пороговым напряжением подключались к виртуальным линиям питания и виртуальным общим линиям напряжения. Виртуальные линии питания и виртуальные общие линии напряжения электрически соединялись с реальными линиями питания и общими линиями напряжения с использованием транзисторов с высоким пороговым напряжением. В течение активного режима транзисторы с высоким пороговым напряжением открывались и подключали транзисторы с низким пороговым напряжением к реальной линии питания и к реальной общей линии напряжения. Во время ждущего режима транзисторы с высоким пороговым напряжением отключались. Виртуальные линии питания эффективно обесточивались, таким образом отключая все транзисторы с низким пороговым напряжением, подключенные к виртуальным линиям питания.

Неблагоприятный эффект отключения всех транзисторов с низким пороговым напряжением заключается в том, что все состояния цепей КМОП с низким пороговым напряжением утрачиваются. В некоторых ситуациях потеря всех данных в цепях с низким пороговым напряжением не является проблемой. К таким ситуациям относятся те, в которых цепи восстанавливают все состояния при возвращении в активный режим. Однако в других ситуациях переход в ждущий режим требует сохранения данных в некоторых или всех отключаемых цепях. Например, может оказаться желательным, чтобы по возвращении в активный режим цепь возобновила функционирование из того состояния, которое имело место на момент, предшествующий переходу в ждущий режим. Восстановление функционирования цепи не представляется возможным, если цепи с низким пороговым напряжением утратят все состояния цепей при переходе в ждущий режим.

Таким образом, существует потребность в цепи, функционирующей с низким напряжением питания и имеющей низкую задержку распространения цепей с низким пороговым напряжением в активном режиме, но сохраняющей состояния цепей в ждущем режиме. Более того, данная цепь не должна требовать каких-либо дополнительных цепей для сохранения состояний при переходе в ждущий режим. Цепь должна иметь низкие характеристики утечки цепей с высоким пороговым напряжением для минимизации статического энергопотребления. В активном режиме цепь должна иметь высокие скоростные характеристики цепей КМОП с низким пороговым напряжением, а в ждущем режиме цепь должна иметь энергонезависимость и низкий ток утечки цепей с высоким пороговым напряжением.

Раскрытие изобретения

Изобретен многопороговый триггер КМОП (МПКМОП), содержащий цепи с низким пороговым напряжением в качестве большей части, если не всех, цепей тракта сигнала триггера для повышения производительности триггера. Далее триггер содержит цепи с высоким пороговым напряжением для устранения каналов утечки через цепи с низким пороговым напряжением, когда триггер находится в ждущем режиме. Цепи с высоким пороговым напряжением размещаются таким образом, чтобы каналы утечки в цепях с низким пороговым напряжением были последовательны с каналами утечки цепей с высоким пороговым напряжением. Таким образом, цепи с высоким пороговым напряжением определяют ток утечки триггера.

Изобретены однофазный и двухфазный триггеры. Однако изобретение не ограничивается только этими конструкциями. Предпочтительные варианты осуществления триггеров содержат ведущие и ведомые регистры. Данные содержатся либо в ведущих, либо в ведомых регистрах в зависимости от фазы или фаз сигналов синхронизации. Перед ведущим триггером может устанавливаться мультиплексор, обеспечивающий дополнительные входные сигналы и тестируемость конструкции.

В одном из вариантов осуществления триггер МПКМОП содержит первый передаточный вентиль, ведущий регистр КМОП со входом, электрически соединенным с выходом первого передаточного вентиля, второй передаточный вентиль, электрически соединенный с выходом ведущего регистра КМОП, а также ведомый регистр со входом, электрически соединенным с выходом второго передаточного вентиля. Второй передаточный вентиль содержит КМОП транзисторы с низким пороговым напряжением.

В однофазном триггере переход в ждущий режим может произойти при любой фазе сигнализации. Размещение цепей с низким пороговым напряжением (LVT) может быть оптимизировано для определенной фазы синхронизации, в течение которой осуществляется переход в ждущий режим. Таким же образом в двухфазном триггере цепи LVT могут размещаться с учетом оптимизации прохождения сигнала в течение функционирования в активном режиме, при обеспечении энергонезависимости данных и низкого тока утечки в ждущем режиме.

Краткое описание чертежей

Особенности и преимущества изобретения станут более понятны из приведенного ниже детального описания вкупе с чертежами, на которые ссылается текст и которые содержат:

Фиг. 1 - функциональная блок-схема прототипа КМОП инвертора.

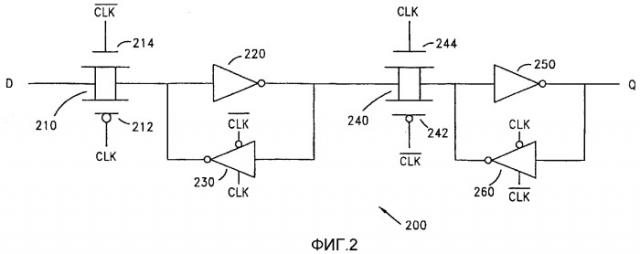

Фиг. 2 - функциональная блок-схема ведущего/ведомого регистра.

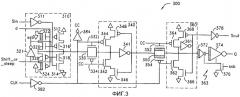

Фиг. 3 - блок-схема однофазного МПКМОП триггера.

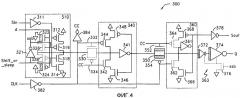

Фиг. 4 - блок-схема однофазного МПКМОП триггера в ждущем режиме с высоким уровнем сигнала синхронизации.

Фиг. 5 - блок-схема каналов утечки однофазного триггера МПКМОП в ждущем режиме с высоким уровнем сигнала синхронизации.

Фиг. 6 - блок-схема однофазного МПКМОП триггера в ждущем режиме с низким уровнем сигнала синхронизации.

Фиг. 7 - блок-схема каналов утечки однофазного триггера МПКМОП в ждущем режиме с низким уровнем сигнала синхронизации.

Фиг. 8 - блок-схема двухфазного триггера МПКМОП в активном режиме.

Фиг. 9 - блок-схема двухфазного триггера МПКМОП в ждущем режиме с низким уровнем phi 1.

Фиг. 10 - блок-схема каналов утечки двухфазного триггера МПКМОП в ждущем режиме с низким уровнем phi 1.

Осуществление изобретения

Данное изобретение описывает некоторое количество вариантов осуществления триггера, реализованного на МПКМОП таким образом, чтобы они могли функционировать с использованием низкого напряжения питания порядка 1 вольта. Изобретенные триггеры обеспечивают высокую скорость функционирования, характерную для триггеров, реализованных на КМОП с низким пороговым напряжением, при низких характеристиках тока утечки, свойственных триггерам, реализованным исключительно на цепях КМОП с высоким пороговым напряжением. Изобретенные триггеры могут быть реализованы с использованием глубокой субмикронной (например, L<=0,18 мкм) технологии. Можно рассчитывать, что сконструированные в соответствии с данным изобретением триггеры могут быть включены в состав IC, являющихся специализированными интегральными схемами (ASIC), процессорами, программируемыми логическими устройствами, памятью или другими цепями.

Можно также рассчитывать, что сконструированные в соответствии с данным изобретением триггеры могут быть использованы в таких устройствах, как мобильные телефоны, пейджеры, карманные персональные компьютеры, ноутбуки либо любые другие электронные устройства, в которых существенный выигрыш даст использование высокопроизводительных триггеров с низким напряжением питания, имеющих низкий ток утечки и позволяющих энергонезависимое хранение данных в ждущем режиме. Например, такой триггер может быть использован в коммуникационном устройстве, имеющем радиочастотный интерфейс, подключенный к низкочастотному блоку обработки. Данный триггер может быть частью РЧ интерфейса либо частью низкочастотного блока обработки. Низкочастотный блок обработки может содержать также процессор, цифровой сигнальный процессор, память и другие цепи. Коммуникационное устройство может быть беспроводным телефоном, пейджером, радиоприемником или каким-либо другим устройством.

На Фиг. 2 приведена функциональная блок-схема варианта осуществления триггера МПКМОП 200. На всех чертежах цепи с низким пороговым напряжением показаны с заштрихованным входом или с заштрихованной частью между истоком и стоком, тогда как цепи с высоким пороговым напряжением приведены без всякой штриховки. Входной сигнал подводится к первому передаточному вентилю 210, состоящему из p-канальной цепи 212 и n-канальной цепи 214. Передаточный вентиль, например 210, иначе называется транзисторами доступа, содержащими n-канальную цепь, например 214, и p-канальную цепь, например 212, подключенными параллельно и управляемыми инверсными напряжениями вентиля. Если напряжение вентиля цепи n-канала 214 низкое, цепь 212 p-канала имеет соответствующее напряжение вентиля, равное или близкое к напряжению источника питания, и обе цепи являются непроводящими. С другой стороны, если напряжение вентиля цепи 214 n-канала равно или близко к напряжению источника питания, а напряжение вентиля цепи p-канала 212 низкое, обе цепи являются проводящими. Если напряжение истока близко к напряжению источника питания, Vdd, существует падение напряжения в цепи 214 n-канала, но практически отсутствует падение напряжения в цепи 212 p-канала.

Первый передаточный вентиль 210 включен или находится в активном состоянии, когда сигнал синхронизации (CLK) имеет низкий уровень. Когда первый передаточный вентиль 210 активен, входной сигнал подается на вход первого инвертора 220. Выход первого инвертора электрически соединен со входом первого инвертора 230 обратной связи. Выход первого инвертора 230 обратной связи, в свою очередь, электрически подключен обратно ко входу первого инвертора 220.

Выход первого инвертора 220 электрически соединен со вторым передаточным вентилем 240. Второй передаточный вентиль 240 состоит из цепи 242 p-канала и цепи 244 n-канала. Как и в случае первого передаточного вентиля 210, цепи второго передаточного вентиля 240 управляются сигналом CLK. Однако второй передаточный вентиль 244 сконструирован таким образом, чтобы быть активным в фазе сигнала CLK, противоположной используемой для активации первого передаточного вентиля 210. В то время как сигнал CLK подводится к цепи 212 p-канала первого передаточного вентиля 210, сигнал/CLK, или инверсный сигнал синхронизации, подводится к цепи p-канала 242 второго передаточного вентиля 240. Таким же образом сигнал/CLK подводится к цепи n-канала 214 первого передаточного вентиля 210, а сигнал CLK подводится к цепи 244 n-канала второго передаточного вентиля 240. Реальная фаза сигнала CLK в момент активности первого передаточного вентиля 210 может быть любой в зависимости от сигналов, подводимых к цепям p-канала и n-канала. Как правило, второй передаточный вентиль 240 сконструирован таким образом, чтобы быть активным в течение фазы CLK, когда первый передаточный вентиль 210 не активен.

Выход передаточного вентиля 240 электрически соединен со входом второго инвертора 250. Выход второго инвертора 250 является выходом триггера 200. Выход второго инвертора 250 также электрически соединен со входом второго инвертора 260 обратной связи. Выход второго инвертора 260 обратной связи электрически соединен со входом второго инвертора 250.

Функционирование триггера 200 может быть описано следующим образом. Логический сигнал подводится ко входу первого передаточного вентиля 210. В течение первой фазы, или состояния, CLK первый передаточный вентиль 210 является активным, и входной сигнал поступает на вход первого инвертора 220. При необходимости выход первого инвертора 220 переходит в состояние отображения инверсии входного сигнала. Первый инвертор 230 обратной связи неактивен в течение фазы синхронизации, при которой активен первый передаточный вентиль 210. Таким образом, во время активности первого передаточного вентиля 210 на выходе первого инвертора 220 наличествует инверсия входного сигнала.

При переходе CLK от первой фазы ко второй фазе, или состоянию, первый передаточный вентиль 210 становится неактивным, а второй передаточный вентиль 240 становится активным. Активируется первый инвертор 230 обратной связи и передает инверсную версию сигнала с выхода первого инвертора 220 на вход первого инвертора 220. Таким образом, сигнал фиксируется в ведущем регистре. Уровень сигнала, сохраняемый в ведущем регистре и формируемый первым инвертором 220 и первым инвертором 230 обратной связи, подводится ко второму инвертору 250 и к выходу триггера 200. Ведомый регистр, состоящий из второго инвертора 250 и второго инвертора 260 обратной связи, поддерживает уровень на выходе триггера 200 в течение последующего цикла синхронизации. Второй инвертор 260 обратной связи неактивен в течение фазы сигнала CLK, когда активен второй передаточный вентиль 240. Второй инвертор 260 обратной связи становится активным, когда сигнал CLK возвращается к той фазе, в которой второй передаточный вентиль 240 неактивен. Сигнал, или бит данных, фиксируется в ведомом регистре в течение времени активности второго инвертора 260 обратной связи.

Таким образом, можно считать, что вариант осуществления триггера 200 в данной конфигурации может содержать цепи с низким пороговым напряжением только в тракте сигнала, а также может содержать цепи с высоким пороговым напряжением в трактах обратной связи и некритичных трактах триггера. Например, на Фиг. 2 инверторы 230 и 260 обратной связи могут быть полностью реализованы на цепях с высоким пороговым напряжением, тогда как инверторы 220 и 250 в тракте прямого сигнала, а также передаточные вентили 210 и 240 могут быть реализованы с использованием цепей с низким пороговым напряжением. В альтернативном варианте некоторые цепи тракта прямого сигнала могут быть цепями с низким пороговым напряжением, тогда как другие - цепями с высоким пороговым напряжением. Цепи с высоким пороговым напряжением могут размещаться таким образом, чтобы обеспечить низкий ток утечки для цепей с низким пороговым напряжением.

На Фиг. 3 приведена детальная блок-схема одного из вариантов осуществления однофазного МПКМОП триггера 300. Триггер 300 содержит четыре основных функциональных блока: скан-мультиплексор 310, ведущий регистр 340, ведомый регистр 360 и выходной буфер 363. Скан-мультиплексор 310 подключен ко входу ведущего регистра 340 с использованием первого передаточного вентиля 330. Выход ведущего регистра 340 подключен ко входу ведомого регистра 360 с использованием второго передаточного вентиля 350. Выход ведомого регистра 360 электрически подключен к буферу 363 перед выходом триггера 300.

Скан-мультиплексор 310 может рассматриваться как часть конструкции триггера 300, но не обязательно должен включаться во все варианты конструкции триггера 300. Скан-мультиплексор 310 используется для функций тестирования в процессе производства и проверки IC. Скан-мультиплексор 310 оборудован сканирующим входом, Sin, предназначенным для сканирующих тестовых сигналов. Кроме того, скан-мультиплексор 310 оборудован входом данных, d. При нормальных условиях эксплуатации триггера 300 используется только вход данных d скан-мультиплексора 310. Хотя сканирующий вход обычно не используется в нормальных условиях эксплуатации, триггер 300 обычно содержит скан-мультиплексор 310 ввиду необходимости тестирования и поверки IC.

Скан-мультиплексор 310 оборудован также входом управляющего сигнала, обозначаемого здесь как Shift_or_sleep. Вход управляющего сигнала используется для выбора, какой из входов мультиплексора будет электрически соединен с выходом скан-мультиплексора 310. Для конфигурации скан-мультиплексора 310, показанной на Фиг. 3, сигнал, подводимый ко входу Sin, электрически соединяется с выходом скан-мультиплексора 310 при высоком уровне управляющего сигнала Shift_or_sleep. Сигнал, подводимый ко входу d, электрически соединяется с выходом скан-мультиплексора 310 при низком уровне управляющего сигнала Shift_or_sleep. Можно считать, что скан-мультиплексор 310 может быть сконфигурирован таким образом, что инвертируется фаза управляющего сигнала. Кроме того, можно считать, что скан-мультиплексор 310 может содержать более двух входов и что для управления выбором входных сигналов может применяться цифровое контрольное слово.

Вход d скан-мультиплексора 310 электрически соединен с затвором первой n-канальной цепи 322 с низким пороговым напряжением (LVT) и с затвором первой р-канальной цепи 324 LVT. Исток первой n-канальной цепи 322 электрически соединен с линией общего напряжения, а исток первой р-канальной цепи 324 LVT электрически соединен с линией питания. Сток первой n-канальной цепи 322 LVT электрически соединен с истоком первой n-канальной цепи 326 с высоким пороговым напряжением (HVT). Таким же образом сток первой р-канальной цепи 324 LVT электрически соединен с истоком первой р-канальной цепи 328 HVT. Стоки первой n-канальной цепи 326 HVT и первой р-канальной цепи 328 HVT электрически соединены и подключены к выходу скан-мультиплексора 310.

Вход Sin скан-мультиплексора 310 подключен таким же образом, за исключением того, что не используются цепи LVT. Вход Sin скан-мультиплексора 310 буферизуется и инвертируется инвертором сигнала 311 до электрического соединения с затворами цепей 314 и 312 HVT, истоки которых подключены соответственно к общей линии напряжения и линии питания. Стоки цепей 314 и 312 вторых n-канала и р-канала HVT электрически соединены соответственно с истоками цепей 318 И 316 третьих n-канала и р-канала HVT. Стоки цепей 318 И 316 третьих n-канала и р-канала HVT электрически соединены между собой и подключены к выходу скан-мультиплексора 310.

Выбор входа d или входа Sin производится на основании сигналов, подаваемых на затворы первых цепей 326 и 328 HVT и третьих цепей 318 и 316 HVT. Управляющий вход скан-мультиплексора 310 электрически соединен с затвором цепи 328 первого р-канала HVT и с затвором цепи 318 третьего n-канала HVT. Управляющий вход электрически соединен также с управляющим инвертором 321, логически инвертирующим сигнал управляющего входа. Выход управляющего инвертора 321 электрически соединен с затворами цепи 326 первого n-канала HVT и цепи 316 третьего р-канала HVT.

Таким образом, если сигнал управляющего входа имеет низкий уровень, цепи 326 и 328 первых n-канала и р-канала HVT приобретают смещение. Сигнал со входа d передается через цепи 322 И 324 первых n-канала и р-канала LVT и через смещенные цепи 326 И 328 первых n-канала и р-канала HVT на выход скан-мультиплексора 310. Сигнал управляющего входа низкого уровня отключает цепи 318 И 316 третьих n-канала и р-канала HVT, и таким образом вход Sin изолируется от выхода скан-мультиплексора 310.

В обратном случае, если сигнал управляющего входа имеет высокий уровень, приобретают смещение цепи 318 И 316 третьих n-канала и р-канала HVT. Сигнал со входа Sin проходит через цепи 314 И 312 вторых n-канала и р-канала HVT и через смещенные цепи 318 И 316 третьих n-канала и р-канала HVT на выход скан-мультиплексора 310. Сигнал управляющего входа высокого уровня отключает цепи 326 И 328 первых n-канала и р-канала HVT, и таким образом вход d изолируется от выхода скан-мультиплексора 310.

Выход скан-мультиплексора 310 электрически соединен с первым передаточным вентилем 330. Первый передаточный вентиль 330 содержит цепи 332 И 334 n-канала и p-канала. В конфигурации, показанной на Фиг. 3, первый передаточный вентиль 330 собран на цепях HVT. Первый передаточный вентиль 330 является проводящим, когда к затвору цепи 332 n-канала подводится высокий уровень напряжения, а к затвору цепи 334 р-канала подводится высокий уровень напряжения.

Выход первого передаточного вентиля 330 электрически соединен со входом ведущего регистра 340 (MR). Вход ведущего регистра 340 электрически соединен с инвертором 341 ведущего регистра (MR). Вход MR 340 электрически соединен также со стоками цепей n-канала и p-канала MR 342 и 344. Выход инвертора MR 341 электрически соединен с выходом ведущего регистра 340. Выход инвертора MR 341 электрически соединен с затворами вторых цепей 346 И 348 n-канала и p-канала MR. Исток цепи 348 второго р-канала MR электрически соединен с линией питания, тогда как исток цепи 346 второго n-канала MR электрически соединен с линией общего напряжения. Сток цепи 348 второго р-канала MR электрически соединен с истоком цепи 344 первого р-канала MR. Таким же образом сток цепи 346 второго n-канала MR электрически соединен с истоком цепи 342 первого n-канала MR. Таким образом, можно считать, что цепи 342 И 346 первого и второго n-каналов MR сконфигурированы последовательно, и цепи 344 И 348 первого и второго р-каналов MR сконфигурированы последовательно.

Выход ведущего регистра 340 электрически соединен со вторым передаточным вентилем 350, содержащим цепи 352 и 354 n-канала и р-канала. В варианте осуществления, показанном на Фиг. 3, во втором передаточном вентиле 350 использованы цепи LVT. Выход второго передаточного вентиля 350 электрически соединен со входом ведомого регистра 360 (SR).

Вход ведомого регистра 360 электрически соединен напрямую с первым выходом ведомого регистра 360. Вход ведомого регистра 360 (SR) подключен также к стокам цепей 362 и 364 первых n-канала и р-канала SR и ко входу 361 инвертора SR. Выход 361 инвертора SR электрически соединен с затворами цепей 368 и 366 вторых р-канала и n-канала SR. Выход 361 инвертора SR также электрически соединен со вторым выходом SR 360.

Исток цепи 368 второго р-канала SR электрически соединен с линией питания, а сток цепи 368 второго р-канала SR электрически соединен с истоком цепи 364 первого р-канала SR. Таким образом, можно считать, что цепи 364 и 368 первого и второго р-каналов SR сконфигурированы последовательно. Таким же образом исток цепи 366 второго n-канала SR электрически соединен с линией общего напряжения, а сток цепи 366 второго n-канала SR электрически соединен с истоком цепи первого n-канала SR 362. Цепи 362 и 366 первого и второго n-каналов SR сконфигурированы последовательно.

Первый выход SR 360 электрически соединен со входом выходного буфера 363. Выходной буфер 363 содержит первый инвертор 372 со входом, электрически соединенным со входом буфера, и с выходом, электрически соединенным со входом второго инвертора 374. Выход второго инвертора 374 является выходом буфера 363, а также выходом триггера 300. Первый и второй инверторы 372 и 374 представляют собой цепи LVT и используют n-канальный переключатель 376 для электрического соединения виртуальной линии общего напряжения первого и второго инверторов 372 и 374 с реальной линией общего напряжения. Затвор переключателя 376 электрически соединен с инвертированным управляющим входом скан-мультиплексора 310, обозначенным как "ssb". Альтернативно может быть использован p-канальный переключатель для электрического соединения виртуальной линии питания первого и второго инверторов 372 и 374 с реальной линией питания. Однако ввиду разницы скоростных показателей и размеров цепей n-каналов и p-каналов n-канальный переключатель может оказаться предпочтительным. Если желательна дополнительная изоляция, могут быть использованы оба вида переключателей для подключения виртуальных линий питания компонентов буфера к реальным линиям питания.

Общая синхронизация используется для управления передаточными вентилями 330 и 350, а также ведущим и ведомым регистрами 340 и 360. Входной сигнал синхронизации (CLK) подводится ко входу первого инвертора 382 синхронизации. Первый инвертор 382 синхронизации может быть использован для буферизации входного сигнала синхронизации в добавление к инвертированию сигнала. Выход первого инвертора 382 синхронизации электрически соединен с цепью 332 n-канала первого передаточного вентиля 330, с цепью 354 p-канала второго передаточного вентиля 350, с цепью 344 первого р-канала MR, с цепью 362 первого n-канала SR, а также со входом второго инвертора 384 синхронизации. Выход первого инвертора 384 синхронизации электрически соединен с цепью 334 p-канала первого передаточного вентиля 330, с цепью 352 n-канала второго передаточного вентиля 350, с цепью первого n-канала MR 342, а также с цепью 364 первого р-канала SR. Таким образом, можно считать, что первый и второй передаточные вентили 330 и 350 проводят в противоположных фазах сигнала синхронизации. Кроме того, первые цепи MR 344 и 342 проводят в фазах сигнала синхронизации, противоположных фазам, управляющим проводимостью первых цепей SR 364 и 362.

В альтернативном случае однофазный триггер 300, показанный на Фиг. 3, может быть модифицирован для функционирования в режиме двухфазного триггера. Для переконфигурирования однофазного триггера 300 в двухфазный триггер должны быть изменены конфигурации линии CLK и первого, и второго инверторов 382 и 384 синхронизации. Эти изменения не показаны на Фиг. 3, но описаны следующим образом. Сигнал CLK и подключения к инверторам 382 и 384 синхронизации удаляются с Фиг. 3. Вместо этого сигнал первой фазы, phi1 (не показан), электрически соединяется с цепью 332 n-канала первого передаточного вентиля 330. Инвертированная версия сигнала первой фазы, phi1, может быть получена логическим инвертированием сигнала первой фазы с использованием первого инвертора 382 синхронизации. Инвертированный сигнал первой фазы электрически соединяется с цепью 334 p-канала первого передаточного вентиля 330. Сигнал второй фазы, phi2 (не показан), электрически соединяется с цепью 352 n-канала второго передаточного вентиля 350. Инвертированная версия сигнала второй фазы может быть получена с использованием второго инвертора 384 синхронизации. Ивертированный сигнал второй фазы электрически соединяется с цепью 354 p-канала второго передаточного вентиля 350. Сигналы первой и второй фазы могут быть, но не в обязательном порядке, активны в течение взаимоисключающих периодов времени. Таким образом, можно считать, что однофазный триггер 300 может быть модифицирован для работы в качестве двухфазного триггера.

Возвращаясь к описанию однофазного триггера 300, показанного на Фиг. 3, функционирование триггера 300 может быть описано следующим образом. В течение активного состояния управляющий сигнал Shift_or_sleep находится на низком уровне. Низкий уровень управляющего сигнала приводит к активности переключателя 376, что включает в работу буфер. Низкий уровень управляющего сигнала приводит также к выбору входа d скан-мультиплексора 310. В течение первой фазы синхронизации, когда сигнал CLK находится на низком уровне, на выходе первого инвертора 382 синхронизации уровень высокий, что активизирует первый передаточный вентиль 330 и деактивирует второй передаточный вентиль 350. Когда уровень сигнала CLK переходит от низкого к высокому, значение данных запирается в ведущем регистре 340 посредством отключения первого передаточного вентиля 330 и активации первых цепей MR 344 и 342. Использование цепей LVT в тракте d-сигнала скан-мультиплексора 310 снижает время установки триггера 300.

Можно считать, что первый и второй передаточные вентили 330 и 350 могут быть сконфигурированы для работы на других фазах сигнала CLK посредством добавления других инверторов сигнала CLK. Реальная фаза сигнала CLK, используемого триггером, не ограничивает изобретение. Описана только одна фазовая конфигурация для простоты изложения.

Второй передаточный вентиль 350 становится активным при переходе уровня сигнала CLK от низкого к высокому. Значение данных, запертое в регистре 340, передается через второй передаточный вентиль 350, ведомый регистр 360 и буфер 363 на выход триггера 300. Цепи LVT 352 и 354 используются во втором передаточном вентиле 350, а также в буфере 363, для снижения времени прохождения сигнала (clock-to-Q) в триггере 300. Таким образом, в течение активного режима время установки триггера 300 снижается посредством использования цепей LVT в тракте d-сигнала скан-мультиплексора 310. Время прохождения сигнала (clock-to-Q) в триггере 300 снижается посредством использования цепей LVT во втором передаточном вентиле 350, а также в выходном буфере.

Функционирование однофазн