Устройство считывания сигналов с многоэлементных фотоприемников (варианты)

Иллюстрации

Показать всеИзобретение относится к системам регистрации оптической информации и ее обработки. Изобретение позволяет повысить чувствительность устройства считывания сигналов с многоэлементных фотоприемников. Сущность изобретения: устройство считывания сигналов с многоэлементных фотоприемников состоит из ячеек, каждая из которых содержит емкость интегрирования, емкость компенсации, буферный транзистор, транзистор выбора ячейки, транзистор сброса, ключевой транзистор, компаратор напряжений. Кроме того, в каждую ячейку устройства введены дополнительный ключ, соединяющий вторую обкладку емкости интегрирования с истоком, подложкой буферного транзистора и входом компаратора, выход которого соединен с затвором ключевого транзистора, а вход разрешения срабатывания соединен с шиной разрешения вывода аналоговых данных, дополнительный буферный транзистор, затвор которого соединен с затвором буферного транзистора, исток соединен со стоком буферного транзистора, подложка соединена с подложкой буферного транзистора, сток соединен с общей шиной, сток транзистора сброса соединен с входом ячейки, причем фазы открытия и закрытия дополнительного ключа противоположны фазам открытия и закрытия ключевого транзистора. 2 н.п. ф-лы, 3 ил.

Реферат

Изобретение относится к системам регистрации оптической информации при помощи гибридных и монолитных фотоприемных устройств (ФПУ) и ее обработки в фокальной плоскости средствами КМОП микроэлектроники с элементами дельта-сигма АЦП.

Известно устройство считывания сигналов с многоэлементных фотоприемников, построенное на принципах дельта-сигма АЦП (US 5886659, 23.03.1999), состоящее из массива ячеек и ряда АЦП, количество которых равно или меньше количества столбцов массива ячеек. Данное устройство позволяет проводить аналого-цифровое преобразоваие одновременно в ячейках одного ряда массива, что позволяет улучшить помехозащищенность изделия, упростить связь с внешними устройствами, уменьшить суммарную рассеиваемую мощность, улучшить однородность устройства в целом. Однако эффективная зарядовая емкость ячейки определяется ее физической зарядовой емкостью (фактически величиной емкости интегрирования в ячейке). Чувствительность и динамический диапазон устройства считывания не увеличивается.

Известно устройство считывания сигналов с многоэлементных фотоприемников, построенное на принципах дельта-сигма АЦП (US 7023369 В2, 04.04.2006), состоящее из ячеек, каждая из которых содержит полностью или частично устройство формирования компенсирующего заряда, компаратор, интегратор. Устройство не позволяет выводить информацию об остаточном, нескомпенсированном заряде, содержащем, в случае детекторов инфракрасного диапазона, значительную часть информационного сигнала. Кроме того, величина компенсирующего заряда определяется величиной внешнего регулируемого напряжения, шум которого не коррелирован с шумом фотоприемника, а, значит, их мощности складываются, а чувствительность ФПУ уменьшается.

Известно устройство считывания сигналов с многоэлементных фотоприемников, построенное на принципах дельта-сигма АЦП (Proc. SPIE, vol.5074, р.208-221, Fig.7), состоящее из ячеек, каждая из которых содержит емкость интегрирования, первая обкладка которой соединена с общей шиной, вторая обкладка соединена с входом ячейки, затвором буферного транзистора и истоком ключевого транзистора, сток которого соединен со второй обкладкой емкости компенсации, первая обкладка которого соединена с общей шиной, транзистор выбора ячейки, исток которого соединен с шиной аналоговых данных, затвор соединен с шиной выбора ячейки, сток соединен с истоком буферного транзистора, транзистор сброса, исток которого соединен с шиной напряжения сброса, а затвор с шиной сброса, компаратор напряжений, выход которого соединен с цифровым устройством обработки и хранения, выход которого соединен с шиной цифровых данных.

Данное устройство является ближайшим к предлагаемому техническому решению.

Устройство работает следующим образом. После сброса емкости интегрирования в исходное состояние начинается ее разрядка током подключенного к входу ячейки фотодетектора. Изменяющееся на емкости интегрирования напряжение, через буферный транзистор, транзистор выбора ячейки и шину аналоговых данных поступает на вход компаратора, выход которого управляет устройством формирования компенсационного заряда, содержащего емкость компенсации, ключевой транзистор, так, что на вторую обкладку емкости интегрирования инжектируется определенная порция заряда.

Недостаток такого устройства заключается в том, что время, необходимое для единичного акта компенсации заряда определяется постоянной времени Tk=R×Ck, где Ck - величина емкости компенсации, R - сопротивление транзистора, через который протекает компенсационный заряд, причем сопротивление этого транзистора значительно увеличивается в процессе протекания компенсационного заряда, поскольку уменьшается разность между постоянным напряжением, приложенным к его затвору, и напряжением на его истоке, увеличивающемся по мере заряда емкости компенсации. Кроме того, величина компенсирующего заряда определяется величиной внешнего регулируемого напряжения, шум которого не коррелирован с шумом фотоприемника, а, значит, их мощности складываются, а чувствительность ФПУ уменьшается. К истоку буферного транзистора оказываются подключенными входная емкость компаратора, емкость шины аналоговых данных, емкости истоков транзисторов выбора ячеек в других, подключенных к данной шине аналоговых данных, ячейках, что ограничивает быстродействие устройства. Поскольку отношение сигнала к шуму определяется количеством актов компенсации заряда, ограничение быстродействия приводит к ограничению чувствительности устройства в целом.

Техническим результатом изобретения является повышение чувствительности устройства считывания сигналов с многоэлементных фотоприемников.

Технический результат достигается тем, что устройство считывания сигналов с многоэлементных фотоприемников, состоящее из ячеек, каждая из которых содержит емкость интегрирования, первая обкладка которой соединена с общей шиной, вторая обкладка соединена с входом ячейки, затвором буферного транзистора и истоком ключевого транзистора, сток которого соединен со второй обкладкой емкости компенсации, первая обкладка которого соединена с общей шиной, транзистор выбора ячейки, исток которого соединен с шиной аналоговых данных, затвор соединен с шиной разрешения вывода аналоговых данных, сток соединен с истоком буферного транзистора, транзистор сброса, исток которого соединен с шиной напряжения сброса, а затвор с шиной сброса, компаратор напряжений, выход которого соединен с цифровым устройством обработки и хранения, выход которого соединен с шиной цифровых данных, при этом устройство содержит дополнительный ключ, соединяющий вторую обкладку емкости интегрирования с истоком, подложкой буферного транзистора и входом компаратора, выход которого соединен с затвором ключевого транзистора, а вход разрешения срабатывания соединен с шиной разрешения вывода аналоговых данных, дополнительный буферный транзистор, затвор которого соединен с затвором буферного транзистора, исток соединен со стоком буферного транзистора, подложка соединена с подложкой буферного транзистора, сток соединен с общей шиной, сток транзистора сброса соединен с входом ячейки, причем фазы открытия и закрытия дополнительного ключа противоположны фазам открытия и закрытия ключевого транзистора.

Технический результат по варианту 2 достигается тем, что устройство считывания сигналов с многоэлементных фотоприемников, состоящее из ячеек, каждая из которых содержит емкость интегрирования, первая обкладка которой соединена с общей шиной, вторая обкладка соединена с входом ячейки, затвором буферного транзистора и истоком ключевого транзистора, сток которого соединен со второй обкладкой емкости компенсации, первая обкладка которого соединена с общей шиной, транзистор выбора ячейки, исток которого соединен с шиной аналоговых данных, затвор соединен с шиной разрешения вывода аналоговых данных, сток соединен с истоком буферного транзистора, транзистор сброса, исток которого соединен с шиной напряжения сброса, а затвор с шиной сброса, компаратор напряжений, выход которого соединен с цифровым устройством обработки и хранения, выход которого соединен с шиной цифровых данных, при этом устройство содержит дополнительный ключ, соединяющий вторую обкладку емкости интегрирования с истоком, подложкой буферного транзистора и выходом дополнительного источника тока, вход включения тока которого соединен с выходом компаратора и затвором ключевого транзистора, вход разрешения срабатывания компаратора соединен с шиной выбора ячейки, вход компаратора соединен с входом ячейки и стоком транзистора сброса, дополнительный буферный транзистор, затвор которого соединен с затвором буферного транзистора, исток соединен со стоком буферного транзистора, подложка соединена с подложкой буферного транзистора, сток соединен с общей шиной, причем фазы открытия и закрытия дополнительного ключа противоположны фазам открытия и закрытия ключевого транзистора.

Технических решений, содержащих признаки, сходные с отличительными, не выявлено, что позволяет сделать вывод о соответствии заявляемого технического решения критерию «новизна».

В ранее известных схемах величина компенсационного заряда определялась выражением dQ=Ck×(Uk-Uп), где Uk - внешнее напряжение на затворе транзистора, передающего компенсационный заряд, Uп - его пороговое напряжение. В заявляемом техническом решении компенсационный заряд равен dQ=Ck×Uпб, где Uпб - пороговое напряжение буферного транзистора. Тем самым вклад в шум устройства от внешнего напряжения Uk устраняется, а чувствительность устройства увеличивается.

Время, необходимое для перетекания компенсационного заряда, определяется R×Ck цепи. В заявляемом техническом решении R равно сопротивлению открытого дополнительного ключа, в то время как в ранее известных решениях это сопротивление значительно увеличивалось в процессе протекания компенсационного заряда. Это происходило из-за уменьшения разности между постоянным напряжением, приложенным к затвору, и напряжением на истоке, увеличивающемся по мере заряда емкости компенсации. Тем самым, в заявляемом техническом решении за отведенное время порция компенсационного заряда может быть передана более точно, или за отведенное время измерений может быть проведено большее количество актов компенсации, что увеличит эффективную зарядовую емкость ячейки и чувствительность устройства в целом.

Тем самым, новая совокупность признаков позволяет сделать заключение о соответствии заявляемого технического решения критерию «изобретательский уровень».

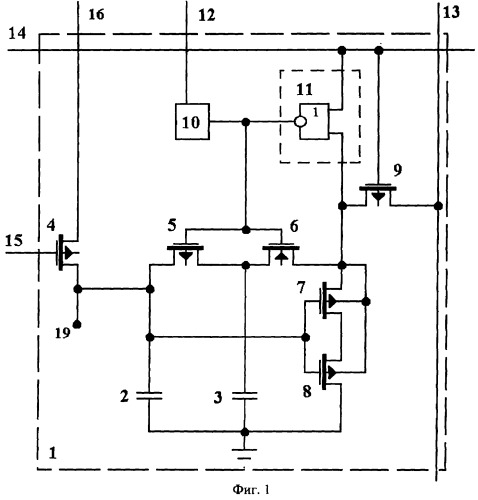

На Фиг.1 приведена принципиальная схема ячейки предлагаемого устройства в случае, когда дополнительный ключ выполнен в виде nМОП транзистора, противоположного ключевому транзистору рМОП типа проводимости, а их затворы соединены. В качестве компаратора используется двухвходовая логическая схема ИЛИ-НЕ с порогом срабатывания, определяемым технологией изготовления.

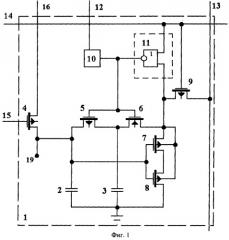

На Фиг.2 приведена принципиальная схема другого варианта ячейки предлагаемого устройства.

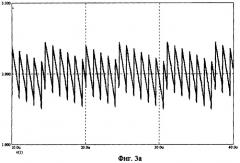

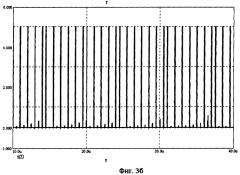

На Фиг.3а и 3б приведены соответственно диаграмма напряжения на второй обкладке емкости интегрирования, демонстрирующая процесс интегрирования фототока детектора и компенсации накопленного заряда и диаграмма импульсного напряжения на выходе компаратора, показывающая количество проведенных актов компенсации.

На Фиг.1 и 2 изображено: 1 - ячейка, 2 - емкость интегрирования, 3 - емкость компенсации, 4 - транзистор сброса, 5 - ключевой транзистор, 6 - дополнительный ключевой транзистор, 7 - буферный транзистор, 8 - дополнительный буферный транзистор, 9 - транзистор выбора ячейки, 10 - цифровое устройство обработки и/или хранения, 11 - компаратор, 12 - шина цифровых данных, 13 - шина аналоговых данных, 14 - шина разрешения вывода аналоговых данных, 15 - шина сброса, 16 - шина напряжения сброса, 17 - шина выбора ячеек, 18 - дополнительный источник тока, 19 - вход ячейки.

Как показано на Фиг.1 и 2, вход ячейки 19 соединен со второй обкладкой емкости интегрирования 2, истоком ключевого транзистора 5, затворами буферного транзистора 7 и дополнительного буферного транзистора 8, стоком транзистора сброса 4, затвор которого соединен с шиной сброса 15, а исток с шиной напряжения сброса 16, первая обкладка емкости интегрирования 2 соединена с общей шиной, первой обкладкой емкости компенсации 3 и стоком дополнительного буферного транзистора 8, исток которого соединен со стоком буферного транзистора 7, подложка соединена с подложкой и истоком буферного транзистора 7, стоком транзистора выбора ячейки 9 и стоком дополнительного ключевого транзистора 6, исток которого соединен со второй обкладкой емкости компенсации и со стоком ключевого транзистора 5, затвор с затвором ключевого транзистора 5, выходом компаратора 11 и входом цифрового устройства обработки и/или хранения 10, выход которого соединен с шиной цифровых данных 12, затвором транзистора выбора ячеек 9 соединен с шиной разрешения вывода аналоговых данных 14, исток транзистора выбора ячеек 9 соединен с шиной аналоговых данных 13.

В варианте устройства, ячейка которого показана на Фиг.1, вход компаратора 11 соединен со стоком транзистора выбора ячейки 9, а вход разрешения срабатывания компаратора 11 соединен с шиной разрешения вывода аналоговых данных 14.

Устройство работает следующим образом.

Первоначально схема приводится в исходное состояние путем подачи кратковременного импульса на шину сброса 15, открывающего транзистор сброса 4. В исходном состоянии вывод аналоговых данных не разрешен, то есть единичный логический уровень на шине 14 обеспечивает закрытое состояние транзистора выбора ячейки 9 и запрещение срабатывания компаратора 11. При этом логический уровень на выходе компаратора 11 (логический ноль) обеспечивает замкнутое состояние ключевого транзистора 5 и разомкнутое состояние дополнительного ключевого транзистора 6. Емкости интегрирования 2 и компенсации 3 оказываются подключенными параллельно и разряжаются током подключенного к входу ячейки 19 фотодетектором, как видно на Фиг.3а.

При разрешении вывода аналоговых данных, транзистор выбора ячейки 9 замыкается и на входе компаратора 11 формируется напряжение, отличающееся от напряжения на емкости интегрирования на величину, равную пороговому напряжению буферного транзистора 7. При этом на компаратор 11 от шины 14 поступает разрешение на срабатывание. Если напряжение на входе компаратора 11 превышает порог его срабатывания, то компаратор изменяет логическое состояние выхода. Полученный импульс (Фиг.3б) поступает на цифровое устройство обработки и/или хранения 10 для последующей передачи по шине цифровых данных 12 во внешние устройства. Кроме того, происходит изменение состояния ключевого транзистора 5 и дополнительного ключевого транзистора 6 на противоположные. Заряд на емкости компенсации изменяется от величины Ck×Ug до величины Ck×(Ug+Uпб), то есть увеличивается на величину dQ=Ck×Uпб, где Ug - текущее значение напряжения на затворе буферного транзистора 7, Uпб - его пороговое напряжение. После окончания импульса выбора ячейки, ключевые транзисторы 5 и 6 возвращаются в исходное состояние, а суммарный заряд на емкости интегрирования и подключенной к ней параллельно емкости компенсации увеличится на величину dQ=Ck×Uпб. Напряжение на второй обкладке емкости интегрирования увеличивается (Фиг.3а). Дополнительный буферный транзистор 8 уменьшает относительные изменения напряжений на стоке, затворе и истоке буферного транзистора 7, улучшая тем самым стабильность величины dQ=Ck×Uпб.

В варианте устройства, ячейка которого показана на Фиг.2, вход компаратора 11 соединен, с входом ячейки 19, вход разрешения срабатывания компаратора 11 соединен с шиной выбора ячеек 17, выход компаратора 11 соединен с входом включения тока дополнительного источника тока 18, выход которого соединен со стоком транзистора выбора ячеек 9.

В этом варианте устройства вход компаратора подключен к входу ячейки и дополнительно увеличивает физическую зарядовую емкость ячейки. Исходно схема находится в аналогичном вырианту по Фиг.1 состоянии, на шинах 14 и 17 поддерживается состояние логической единицы, и подключенные параллельно емкости 2 и 3 разряжаются током фото детектора, как видно на Фиг.3а.

При выборе ячейки (логический ноль на шине 17), на компаратор 11 поступает разрешение на срабатывание. Если напряжение на входе компаратора 11 превышает порог его срабатывания, то компаратор изменяет логическое состояние выхода, а полученный импульс (Фиг.3б) поступает на цифровое устройство обработки и/или хранения 10. Кроме того, включается дополнительный источик тока 18 и на емкости компенсации 3, через открытый дополнительный ключевой транзистор 6, формируется напряжение, отличающееся от напряжения на емкости интегрирования на величину порогового напряжения Uпб буферного транзистора 7.

После окончания импульса выбора ячейки, ключевые транзисторы 5 и 6 возвращаются в исходное состояние, а суммарный заряд на емкости интегрирования и подключенной к ней параллельно емкости компенсации увеличится на величину dQ=Ck×Uпб.

После подачи определенного количества импульсов на шину выбора ячейки 17, подается импульс разрешения вывода аналоговых данных на шину 14 и по шине аналоговых данных 13 происходит вывод остаточной аналоговой информации.

В варианте схемы, изображенной на Фиг.2, уменьшается емкость, подключенная к истоку буферного транзистора, что увеличивает быстродействие и требует меньшие токи буферного транзистора. Кроме того, дополнительный источник тока включается компаратором только в то время, когда требуется проведение компенсации, уменьшая потребляемый схемой ток. Шина аналоговых данных требуется лишь для вывода остаточных аналоговых данных в конце кадра, а акты компенсации возможно проводить без ее участия одновременно в нескольких строках фотоматрицы, что в целом увеличивает чувствительность устройства считывания сигналов.

Преимущество предлагаемого технического решения заключаются в том, что оно позволяет увеличить чувствительность устройства считывания за счет увеличения эффективной зарядовой емкости, достигаемого путем увеличения количества актов компенсации заряда за отведенное время измерения, обусловленного увеличением быстродействия схемы.

1. Устройство считывания сигналов с многоэлементных фотоприемников, состоящее из ячеек, каждая из которых содержит емкость интегрирования, первая обкладка которой соединена с общей шиной, вторая обкладка соединена с входом ячейки, затвором буферного транзистора и истоком ключевого транзистора, сток которого соединен со второй обкладкой емкости компенсации, первая обкладка которого соединена с общей шиной, транзистор выбора ячейки, исток которого соединен с шиной аналоговых данных, затвор соединен с шиной разрешения вывода аналоговых данных, сток соединен с истоком буферного транзистора, транзистор сброса, исток которого соединен с шиной напряжения сброса, а затвор с шиной сброса, компаратор напряжений, выход которого соединен с цифровым устройством обработки и хранения, выход которого соединен с шиной цифровых данных, отличающееся тем, что устройство содержит дополнительный ключ, соединяющий вторую обкладку емкости интегрирования с истоком, подложкой буферного транзистора и входом компаратора, выход которого соединен с затвором ключевого транзистора, а вход разрешения срабатывания соединен с шиной разрешения вывода аналоговых данных, дополнительный буферный транзистор, затвор которого соединен с затвором буферного транзистора, исток соединен со стоком буферного транзистора, подложка соединена с подложкой буферного транзистора, сток соединен с общей шиной, сток транзистора сброса соединен с входом ячейки, причем фазы открытия и закрытия дополнительного ключа противоположны фазам открытия и закрытия ключевого транзистора.

2. Устройство считывания сигналов с многоэлементных фотоприемников, состоящее из ячеек, каждая из которых содержит емкость интегрирования, первая обкладка которой соединена с общей шиной, вторая обкладка соединена с входом ячейки, затвором буферного транзистора и истоком ключевого транзистора, сток которого соединен со второй обкладкой емкости компенсации, первая обкладка которого соединена с общей шиной, транзистор выбора ячейки, исток которого соединен с шиной аналоговых данных, затвор соединен с шиной разрешения вывода аналоговых данных, сток соединен с истоком буферного транзистора, транзистор сброса, исток которого соединен с шиной напряжения сброса, а затвор с шиной сброса, компаратор напряжений, выход которого соединен с цифровым устройством обработки и хранения, выход которого соединен с шиной цифровых данных, отличающееся тем, что устройство содержит дополнительный ключ, соединяющий вторую обкладку емкости интегрирования с истоком, подложкой буферного транзистора и выходом дополнительного источника тока, вход включения тока которого соединен с выходом компаратора и затвором ключевого транзистора, вход разрешения срабатывания компаратора соединен с шиной выбора ячейки, вход компаратора соединен с входом ячейки и стоком транзистора сброса, дополнительный буферный транзистор, затвор которого соединен с затвором буферного транзистора, исток соединен со стоком буферного транзистора, подложка соединена с подложкой буферного транзистора, сток соединен с общей шиной, причем фазы открытия и закрытия дополнительного ключа противоположны фазам открытия и закрытия ключевого транзистора.