Способ параллельного логического суммирования аналоговых сигналов слагаемых, эквивалентных двоичной системе счисления, и устройство для его реализации

Иллюстрации

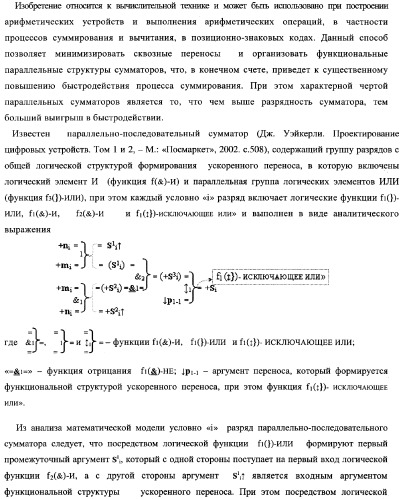

Показать всеИзобретение относится к вычислительной технике и может быть использовано при построении арифметических устройств и выполнения арифметических операций, в частности процессов суммирования и вычитания, в позиционно-знаковых кодах. Техническим результатом является повышение быстродействия. Каждый разряд сумматора содержит три элемента ИЛИ, три элемента И, два элемента НЕ и выполнен в виде двух каналов - канала формирования положительной суммы и канала формирования условно отрицательной суммы. 2 н.п. ф-лы, 5 ил.

Реферат

Текст описания приведен в факсимильном виде.

1. Способ параллельного логического суммирования последовательностей аналоговых сигналов слагаемых, эквивалентных двоичной системе счисления, включающий поразрядное выполнение преобразований аргументов аналоговых сигналов слагаемых [ni] и [mi], которые принимают либо условно высокий или активный уровень, либо условно низкий сигнал или неактивный уровень, при этом из входных аналоговых сигналов аргументов ni и mi в условно «i» разряде формируют аргумент аналогового сигнала первой промежуточной логической суммы S1i, посредством логических функций f1(})-ИЛИ и аргумент второй промежуточной суммы S2i, посредством логических функций f1(&)-И, отличающийся тем, что второй аргумент промежуточной суммы S2i формируют посредством логической функции f1(&)-И с учетом аргумента аналогового сигнала первой промежуточной логической суммы S1i-1 «i-1» разряда, который логически объединяют посредством логической функции f2(})-ИЛИ с аргументом аналогового сигнала, который является результатом преобразования логической функции f2(&)- И из системы аргументов аналоговых сигналов первой промежуточной суммы S1i-1 условно «i-1» разряда и одновременно измененных посредством логических функций f1(&)-HE и f2(&)-HE аргументов аналоговых сигналов слагаемых ni и mi условно «i» разряда, а результатом объединения является аргумент аналогового сигнала положительной суммы +Si, при этом аргумент аналогового сигнала условно отрицательной суммы -Si формируют посредством логической функции f3(&)-И из аргументов системы аналоговых сигналов, которая включает аргумент аналогового сигнала, который является результатом логического объединения посредством логической функции f3(})-ИЛИ одновременно измененных посредством логических функций f1(&)-HE и f2(&)-HE аргументов аналоговых сигналов слагаемых ni и mi условно «i» разряда, аргумента аналогового сигнала первой промежуточной суммы S1i и одновременно измененные посредством логических функций f3(&)-HE и f4(&)-HE аргументов аналоговых сигналов слагаемых ni-1 и mi-1 условно «i-1» разряда.

2. Устройство параллельного суммирования, условно «i» разряд которого включает логические функции f1(})-ИЛИ, f1(&)-HE и f1(&)-И, две функциональные входные связи которой являются входными связями приема аргументов слагаемых ni и mi, отличающееся тем, что условно «i» разряд параллельного сумматора выполнен в виде двух каналов формирования аргумента положительной суммы +Si и аргумента условно отрицательной суммы -Si, при этом в положительный канал, для формирования аргумента результирующей суммы +Si, введены логические функции f2(&)-HE и f2(})-ИЛИ, а в условно отрицательный канал, для формирования аргумента результирующей суммы -Si, введены логическая функция f3(})-ИЛИ и выходная логическая функция f3(&)-И с логическими функциями f3(&)-HE и f4(&)-HE, при этом функциональные связи логических функций в структуре сумматора выполнены в соответствии с математической моделью вида где - логическая функция f(&)-И; логическая функция f1(})-ИЛИ;«=&=» - логическая функция f(&)-HE изменения активности входного аргумента аналогового сигнала.