Цифровой преобразователь угла

Иллюстрации

Показать всеИзобретение относится к области автоматики и вычислительной техники и может найти применение для управления угловым положением подвижных частей объекта регулирования. Изобретением достигается результат, заключающийся в обеспечении точного следящего преобразования углового положения ротора 2-фазного датчика угла в выходной двоичный код N с диапазоном изменения 0…1, при использовании 2-фазных датчиков угла, в огибающих выходных напряжений которых могут присутствовать высшие нечетные пространственные гармоники (например, до девятой включительно - sin3α, sin5α, sin7α и sin9α) с различными соответствующими весовыми коэффициентами - h3, h5, h7 и h9. Технический результат достигается за счет использования 2-фазного датчика угла с дополнительной обмоткой опорного напряжения (вторичная обмотка, параллельная обмотке возбуждения); формирования из выходного напряжения указанной опорной обмотки первого и второго корректирующих напряжений вида UК1 = минус (h3+h5)·sin4·2πN и UK2 = минус (h7+h9)·sin8·2πN; введения первого и второго корректирующих напряжений в цепь сигнала рассогласования цифрового преобразователя угла для исключения составляющих погрешности преобразования вида sin4α и sin8α. 2 ил.

Реферат

Изобретение относится к области автоматики и вычислительной техники, а именно к элементам систем цифрового управления, представляющим в цифровом виде информацию о текущем угловом положении подвижной части объекта регулирования.

Известен цифровой преобразователь угла (ЦПУ) следящего типа, выбранный в качестве аналога, в котором используются: 2-фазный датчик угла (ДУ) с выходными напряжениями переменного тока US=к·UB·sinθ и UC=к·UB·cosθ, где UB - напряжение возбуждения ДУ, к - конструктивный параметр ДУ, θ - угловое положение ротора ДУ; генератор напряжения возбуждения 2-фазного ДУ; селектор квадранта; реверсивный счетчик с текущим значением кода Ф, представляющим собой выходной код ЦПУ; схемы выделения синуса и косинуса с коэффициентами передачи соответственно |sinΦ| и минус |cosΦ|; 2-входовый суммирующий усилитель; демодулятор с фильтром; интегратор; преобразователь напряжения в частоту; дешифратор и шина выходного цифрового сигнала Φ (Вульвет Дж. Датчики в цифровых системах. / Пер. с англ. под ред. А.С.Яроменка. М.: Энергоиздат, 1981. - 200 с., ил., стр. 153).

В таком ЦПУ нарушается условие точного преобразования угла в код (Φ=θ) при работе с реальными 2-фазными ДУ, в огибающих выходных напряжений которых (закономерность изменения амплитудных значений выходных напряжений переменного тока по углу), кроме первой пространственной гармоники sinθ, присутствуют существенные по величине высшие нечетные пространственные гармоники (sin3θ, sin5θ, sin7θ и sin9θ) с весовыми коэффициентами h3, h5, h7 и h9. Присутствие третьей и пятой гармоник вызывает появление составляющей погрешности преобразования вида (h3+h5)·sin4θ, а седьмой и девятой - (h7+h9)·sin8θ.

Известен ЦПУ следящего типа (В.М.Домрачев, Г.Ф.Мончак, А.П.Синицын. Преобразователь угла поворота вала в код. АС SU №1515365, Бюл. №38 от 15.10.89), выбранный в качестве прототипа, наиболее близкий к предлагаемому, который обеспечивает точное преобразование углового положения α ротора ДУ в двоичный код N при работе с 2-фазными ДУ, имеющими третью и пятую пространственные гармоники в огибающих.

В таком ЦПУ сигнал рассогласования UP получает дополнительную составляющую Uк = минус 4·(h3+h5)·U1·cos(2πN)·cos(2·2πN) и, тем самым, исключает составляющую погрешности преобразования вида (h3+h5)·sin4α. При этом негативное влияние седьмой и девятой гармоник на точность преобразования не устраняется, а корректировка по третьей и пятой гармоникам может осуществляться благодаря возможности подключения входа третьего ФЦАП к выходу первого ФЦАП с базовым сигналом вида U1·cos(2πN), что не всегда реализуется на практике. Такой возможности нет при применении серийных отечественных преобразователей выходных сигналов 2-фазных ДУ (микросборки типа 427ПВ2ТА или 2602ПВ1, НИИЭМП, г. Пенза) и аналогичного назначения зарубежных преобразователей (AD2S82A, ANALOG DEVICES, USA), которые реализуют алгоритм преобразования, соответствующий алгоритму аналога. Однако их применение позволяет многократно снизить массогабаритные характеристики ЦПУ в целом, повысить показатели надежности и уменьшить стоимостные показатели.

В отличие от прототипа предлагаемый ЦПУ решает задачу точного преобразования угла в код при наличии у ДУ не только третьей и пятой пространственных гармоник, но и седьмой, а также девятой, с весовыми коэффициентами h7, h9, даже при отсутствии базового сигнала U1·cos(2πN). В этом ЦПУ для корректировки в качестве базового сигнала используется выходное напряжение UОП дополнительной вторичной обмотки 2-фазного ДУ, параллельной его обмотке возбуждения.

Предлагаемый ЦПУ содержит: 2-фазный ДУ с дополнительной обмоткой опорного UОП напряжения, с угловым положением ротора α и с выходными напряжениями U1 и U2; генератор напряжения возбуждения 2-фазного ДУ; селектор квадранта; первый дешифратор; реверсивный n-разрядный двоичный счетчик с текущим значением кода N, представляющим собой выходной код ЦПУ; первый и второй ФЦАП с входящими в их состав дешифраторами и с коэффициентами передачи КФЦАП1=|cos2πN| и КФЦАП2 = минус |sin2πN| соответственно; третий ФЦАП со вторым дешифратором и с коэффициентом передачи КФЦАП3 = минус (h3+h5)·sin(4·2πN); первый аналоговый сумматор; демодулятор с фильтром; интегратор; преобразователь напряжения в частоту и шину выходного кода N, в котором выход генератора напряжения возбуждения подключен к обмотке возбуждения 2-фазного ДУ, фазные выходы с напряжениями U1 и U2 последнего подключены к аналоговым входам селектора квадранта, первый и второй выходы которого подключены соответственно к аналоговым входам первого и второго ФЦАП, их выходы подключены к первому и второму входам первого аналогового сумматора соответственно, выход демодулятора с фильтром через интегратор и преобразователь напряжения в частоту подключен к управляющим входам реверсивного n-разрядного двоичного счетчика, выходы двух старших разрядов которого через первый дешифратор подключены к цифровым входами селектора квадранта, выходы (n-2) младших разрядов подключены к цифровым входам первого, второго ФЦАП и через второй дешифратор - к цифровым входам третьего ФЦАП, выходы реверсивного n-разрядного двоичного счетчика подключены к шине выходного кода ЦПУ. В состав ЦПУ дополнительно введены: второй аналоговый сумматор, третий дешифратор и четвертый ФЦАП с коэффициентом передачи КФЦАП4 = минус (h7+h9)·sin8·(2πN). При этом аналоговый выход первого аналогового сумматора подключен к первому входу второго аналогового сумматора, выход которого подключен к входу выпрямляемого напряжения демодулятора, вход опорного напряжения демодулятора объединен с аналоговыми входами третьего и четвертого ФЦАП и с выходом дополнительной обмотки опорного напряжения 2-фазного ДУ, выходы третьего и четвертого ФЦАП подключены ко второму и третьему входам второго аналогового сумматора, а цифровой вход четвертого ФЦАП подключен через третий дешифратор к (n-3) младшим разрядам реверсивного n-разрядного двоичного счетчика.

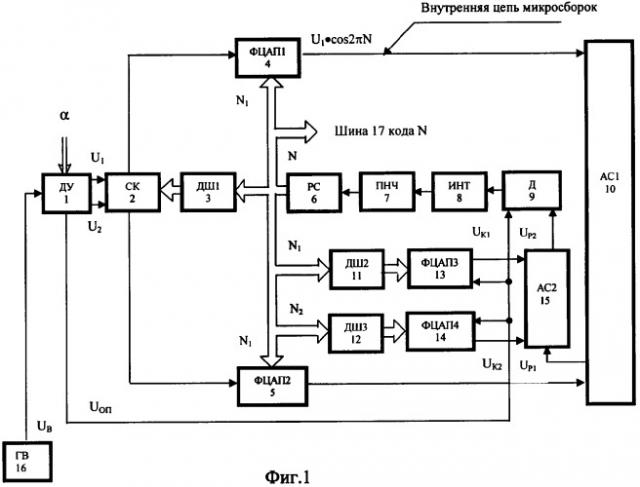

На фиг.1 приведена функциональная схема предлагаемого ЦПУ следящего типа, которая содержит: 2-фазный датчик угла (ДУ) 1 с дополнительной обмоткой опорного UОП напряжения, селектор квадранта (СК) 2, первый дешифратор (ДШ1) 3, первый и второй функциональные цифроаналоговые преобразователи (ФЦАП1 и ФЦАП2) 4 и 5 с входящими в их состав дешифраторами, реверсивный n-разрядный двоичный счетчик (PC) 6, преобразователь напряжения в частоту (ПНЧ) 7, интегратор (ИНТ) 8, демодулятор с фильтром (Д) 9, первый и второй аналоговые сумматоры (АС1 и АС2) 10 и 15, второй и третий дешифраторы (ДШ2 и ДШ3) 11 и 12, третий и четвертый функциональные цифроаналоговые преобразователи (ФЦАП3 и ФЦАП4) 13 и 14, генератор напряжения возбуждения (ГВ) 16 2-фазного ДУ и шину 17 выходного кода N.

На схеме приняты следующие обозначения: α - угловое положение ротора 2-фазного ДУ 1; UB - выходное напряжение генератора возбуждения 16 (напряжение возбуждения 2-фазного ДУ 1); UОП - напряжение переменного тока дополнительной опорной обмотки 2-фазного ДУ; U1 и U2 - выходные напряжения переменного тока 2-фазного ДУ; N - текущее значение кода реверсивного счетчика 6; N1 - текущее значение (n-2) младших разрядов кода реверсивного счетчика 6; N2 - текущее значение (n-3) младших разрядов кода реверсивного счетчика 6; UP1 - напряжение рассогласования ЦПУ без коррекции; UP2 - напряжение рассогласования ЦПУ с коррекцией; UK1 = минус UОП·(h3+h5)·sin(4·2πN) - выходное напряжение переменного тока третьего ФЦАП 13 (первое корректирующее напряжение) и UK2 = минус

UОП·(h7+h9)·sin(8·2πN) - выходное напряжение переменного тока четвертого ФЦАП 14 (второе корректирующее напряжение).

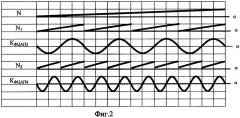

Характер изменения кодов и коэффициентов передач КФЦАП3 и КФЦАП4 по аргументу α≡2πN показан на фиг.2.

Точное преобразование достигается следующим образом. При возбуждении 2-фазного ДУ 1 напряжением UB от генератора напряжения возбуждения 16 его выходные напряжения U1 и U2 поступают через селектор квадранта 2 на аналоговые входы первого и второго ФЦАП 4 и 5. Выходной сигнал U1·cos2πN первого ФЦАП1 4 поступает (внутренняя цепь ЦПУ) на первый вход первого аналогового сумматора АС1 10, а на его второй вход поступает выходной сигнал минус U2·sin2πN второго ФЦАП2 5. Выходной сигнал аналогового сумматора UP1=U1·cos2πN-U2·sin2πN поступает на первый вход второго аналогового сумматора АС2 15. На объединенные аналоговые входы третьего, четвертого ФЦАП 13, 14 и вход опорного напряжения демодулятора Д 9 поступает сигнал UОП с выхода дополнительной обмотки опорного напряжения 2-фазного ДУ 1. Третий ФЦАП3 13 с дешифратором ДШ2 11 и четвертый ФЦАП4 14 с дешифратором ДШ2 12 с учетом текущих значений кодов N1, N2 и свойственных им коэффициентов передач КФЦАП3 и КФЦАП4 формируют первое UK1 и второе UK2 корректирующие напряжения соответственно, которые поступают на второй и третий входы второго аналогового сумматора 15. Таким образом, на выходе второго аналогового сумматора формируется напряжение рассогласования вида UP2=UP1-UK1-UK2, которое поступает на вход выпрямляемого напряжения демодулятора 9 и обеспечивает значение кода реверсивного n-разрядного двоичного счетчика, точно соответствующее текущему значению угла α, несмотря на наличие указанных ранее нечетных гармоник у 2-фазного ДУ. Для этого сигнал с выхода демодулятора 9 с фильтром (уже в виде напряжения постоянного тока) через интегратор 8 и преобразователь напряжения в частоту 7 управляет текущим значением кода реверсивного n-разрядного двоичного счетчика 6. Управление осуществляется таким образом, чтобы при текущем угловом положении ротора 2-фазного ДУ сигнал на выходе второго аналогового сумматора стремился к нулевому значению.

Описанный алгоритм точного преобразования реализуется при условии введения второго аналогового сумматора в цепь «выход первого аналогового сумматора - вход выпрямляемого напряжения демодулятора». Такое построение возможно и при использовании указанных ранее серийных преобразователей выходных сигналов 2-фазных ДУ.

Требуемые масштабные коэффициенты передачи (h3+h5) и (h7+h9) соответственно третьего и четвертого ФЦАП 13 и 14 устанавливаются в процессе проведения простейших регулировочных операций, что обеспечивает повышенную точность преобразования угла в код.

Таким образом, предлагаемый ЦПУ при использовании 2-фазных ДУ с широким спектром нечетных пространственных гармоник и имеющих дополнительную обмотку опорного напряжения и при применении выпускаемых промышленностью малогабаритных высоконадежных гибридных аналого-цифровых микросборок, не имеющих внешнего вывода с базовым сигналом вида U1·cos2πN, обеспечивает точное преобразование угла в код.

Цифровой преобразователь угла следящего типа, содержащий 2-фазный датчик угла с угловым положением ротора α; генератор напряжения возбуждения 2-фазного датчика угла; селектор квадранта; первый дешифратор; реверсивный n-разрядный двоичный счетчик текущего значения кода N-выходного кода цифрового преобразователя угла; первый и второй функциональные цифроаналоговые преобразователи с коэффициентами передачи соответственно |cos2πN| и минус |sin2πN|; третий функциональный цифроаналоговый преобразователь со вторым дешифратором и с коэффициентом передачи минус (h3+h5)·sin(4·2πN), где h3 и h5 - весовые коэффициенты высших нечетных пространственных гармоник; первый аналоговый сумматор; демодулятор с фильтром; интегратор; преобразователь напряжения в частоту; шину кода N, в котором выход генератора напряжения возбуждения подключен к обмотке возбуждения 2-фазного датчика угла, выходы 2-фазного датчика угла подключены к аналоговым входам селектора квадранта, первый и второй выходы последнего подключены соответственно к аналоговым входам первого и второго функциональных цифроаналоговых преобразователей, их выходы подключены к первому и второму входам первого аналогового сумматора, выход демодулятора с фильтром через интегратор и преобразователь напряжения в частоту подключен к входам реверсивного n-разрядного двоичного счетчика, выходы 2-х старших разрядов которого через первый дешифратор подключены к цифровым входами селектора квадранта, выходы (n-2)-х младших разрядов подключены к цифровым входам первого, второго функциональных цифроаналоговых преобразователей и через второй дешифратор - к цифровым входам третьего функционального цифроаналогового преобразователя, выходы реверсивного n-разрядного двоичного счетчика подключены к шине выходного кода цифрового преобразователя угла, отличающийся тем, что в него введены дополнительно третий дешифратор, четвертый функциональный цифроаналоговый преобразователь с коэффициентом передачи минус (h7+h9)·sin8·(2πN), где h7 и h9 - весовые коэффициенты высших нечетных пространственных гармоник; и второй аналоговый сумматор, а 2-фазный датчик угла выполнен с дополнительной вторичной обмоткой опорного напряжения, при этом аналоговые входы третьего, четвертого функциональных цифроаналоговых преобразователей и вход опорного напряжения демодулятора объединены между собой и подключены к выходу дополнительной обмотки опорного напряжения 2-фазного датчика угла, цифровой вход четвертого функционального цифроаналогового преобразователя через третий дешифратор подключен к (n-3) младшим разрядам кода реверсивного n-разрядного двоичного счетчика, выход первого аналогового сумматора подключен к первому входу второго аналогового сумматора, выход третьего функционального цифроаналогового преобразователя подключен к второму входу второго аналогового сумматора, выход четвертого функционального цифроаналогового преобразователя подключен к третьему входу второго аналогового сумматора, а его выход - к входу выпрямляемого напряжения демодулятора.