Интерполирующий преобразователь время-код

Иллюстрации

Показать всеИзобретение относится к технике прецизионного измерения интервалов времени и направлено на повышение стабильности за счет постоянной оценки точности и калибровки преобразования. Этот результат обеспечивается за счет того, что в интерполирующий преобразователь время-код введены блок калибровки, четвертый и пятый регистры, инвертор и измеритель частоты импульсов. Причем соответствующие входы решающего блока подключены к выходам измерителя частоты импульсов, четвертого и пятого регистров, информационные входы четвертого и пятого регистров соединены с соответствующими выходами первого и второго шифраторов. Тактовые входы первого и второго регистров, триггера, а также входы измерителя частоты импульсов и блока калибровки соединены с выходом генератора, управляемого напряжением, вход управления которого соединен с выходом блока калибровки, входной зажим соединен с входом сброса счетчика импульсов, тактовым входом третьего регистра, входом первой цифровой линии задержки, входом разрешения первого регистра и через инвертор - с входом сброса триггера и входом разрешения второго регистра, прямой и инверсный выходы триггера соединены с входами тактирования четвертого и пятого регистров соответственно. 1 з.п. ф-лы, 2 ил.

Реферат

Область техники, к которой относится изобретение

Настоящее изобретение относится к технике прецизионного измерения интервалов времени, в частности к устройствам для измерения длительности однократного импульса.

Уровень техники

Для измерения интервалов времени широко применяются преобразователи время-код, действие которых основано на подсчете числа импульсов эталонного периода, укладывающихся в измеряемый интервал времени. Для повышения точности преобразования за счет уменьшения шага квантования времени используются различные способы интерполяции эталонного периода.

Известен цифровой измеритель интервалов времени [1], который содержит эталонный генератор импульсов, выход которого присоединен через первый элемент И к входу счетчика импульсов, при этом оставшийся вход первого элемента И подключен к выходу триггера, входы которого служат входами сигналов пуска и останова устройства. Кроме того, имеется подключенная к выходу эталонного генератора последовательная цепь множества элементов задержки, выход каждого из которых соединен с входом сброса соответствующего дополнительного триггера, число которых равно числу элементов задержки. Выходы всех дополнительных триггеров присоединены к входам шифратора. Процесс измерения начинается после сброса счетчика импульсов и триггеров импульсом пуска, а завершается импульсом останова. Старшие разряды результата измерения образуются на выходах счетчика импульсов и отображают целое число эталонных периодов, укладывающихся в измеряемый интервал, а младшие разряды результата образуются на выходах шифратора и отображают дробную часть эталонного периода - остаток от деления интервала на эталонный период в единицах времени задержки элемента задержки. Недостаток данного аналога - низкая точность измерения, погрешность которого не может быть меньше времени задержки одного элемента задержки.

Аналогами настоящего изобретения являются также схемы цифровых преобразователей время-код, в которых использован нониусный метод оценки дробной части измеряемого с помощью эталонного генератора интервала времени, например схема, описанная в [2]. Данное устройство включает основной и дополнительный генераторы импульсов, периоды которых различаются на малую величину, которая и составляет значение разрешения по времени. В известное устройство входят также два триггера и два элемента И, управляющие процессом нониусной развертки, а также два счетчика импульсов, отображающих результат измерения. При высокой точности измерения данного устройства оно имеет низкую производительность, так как процесс нониусной развертки занимает множество опорных периодов, тем большее, чем выше точность измерения.

Другим аналогом настоящего изобретения является временной интерполятор [3], содержащий счетчик импульсов и секционированную линию задержки, входы которых соединены с общим зажимом опорных сигналов. Устройство включает регистр в виде множества триггеров с общими информационными и сбросовыми входами, причем синхронизирующие входы триггеров соединены с соответствующими промежуточными отводами линии задержки. Кроме того, в схему входит постоянное запоминающее устройство (ПЗУ), которое служит преобразователем термометрического кода регистра в двоичный код. Общее время задержки секционированной линии задержки равно одному опорному периоду. Запуск устройства осуществляется синхронизированным с опорным сигналом стартовым импульсом, который разрешает работу счетчика импульсов. Одновременно опорные сигналы распространяются по линии задержки. В момент поступления стопового импульса счетчик импульсов фиксирует число полных опорных периодов, уложившихся в измеряемый интервал, а регистр - номер отвода секционированной линии задержки, до которого успел распространиться опорный сигнал. В итоге счетчик отражает старшие биты результата измерения, а ПЗУ - младшие биты. Погрешность измерения определяется в аналоге временем задержки одной секции линии задержки, что существенно меньше опорного периода. Кроме того, имеется дополнительный источник погрешности преобразования из-за возможной неравномерности задержки отдельных секций линии задержки.

Наиболее близким по технической сущности к настоящему изобретению является устройство для преобразования интервала времени с двойной интерполяцией [4]. Данный аналог, принятый за прототип, построен на основе мультифазного генератора (МФГ). Один регистр с выходным шифратором фиксирует двоичный код позиции сигнала Старт внутри опорного периода МФГ, а второй регистр со своим шифратором - код позиции сигнала Стоп. На протяжении интервала между входными сигналами разрешается работа счетчика импульсов, который отображает в двоичном коде число полных опорных периодов, укладывающихся в преобразуемый интервал. Состояние счетчика импульсов также записывается в третий регистр сигналом Стоп.

МФГ, построенный на основе цепи элементов задержки, на каждом выходе вырабатывает импульсы типа «меандр». В моменты поступления входных сигналов Старт и Стоп в первый и второй регистры соответственно записываются термометрические коды их фаз, отсчитанные по интерполирующей субшкале МФГ. Поскольку признаком типа зафиксированной регистром волны МФГ служит состояние первого выхода регистра, то оно может рассматриваться как состояние старшего разряда двоичного кода фазы. Шифраторы преобразуют термометрические коды регистров в двоичные числа, отражающие порядковые номера выходов регистров, на которых происходит инверсия логического состояния, то есть двоичные коды моментов поступления сигналов Старт и Стоп.

К достоинству данного устройства можно отнести простоту и чисто цифровое исполнение устройства.

Недостатком прототипа является недостаточная точность и низкая стабильность при изменениях температуры и питающего напряжения, поскольку не предусмотрен режим калибровки.

Сущность изобретения

Целью настоящего изобретения является повышение точности и стабильности преобразователя время-код. Указанная цель достигается введением процедуры калибровки и фиксации моментов спада и фронта измеряемого интервала относительно фронтов генератора, управляемого напряжением (ГУН), выступающего в роли опорного генератора.

Интерполирующий преобразователь время-код содержит первую цифровую линию задержки (ЦЛЗ), множество выходов которой присоединено к соответствующим информационным входам первого и второго регистров, выходы которых соединены с соответствующими входами первого и второго шифраторов соответственно, а также ГУН, выходом подключенный к входу тактирования счетчика импульсов, триггер, вход установки которого соединен с входным зажимом устройства, третий регистр, информационными входами подключенный к соответствующим выходам счетчика импульсов, а выходами - к соответствующим входам решающего блока. Для достижения поставленной цели дополнительно введены блок калибровки, четвертый и пятый регистры, инвертор и измеритель частоты импульсов, причем соответствующие входы решающего блока подключены к выходам измерителя частоты импульсов, четвертого и пятого регистров, при этом информационные входы четвертого и пятого регистров соединены с соответствующими выходами первого и второго шифраторов, тактовые входы первого и второго регистров, триггера, а также входы измерителя частоты импульсов и блока калибровки соединены с выходом ГУН, вход управления которого соединен с выходом блока калибровки, входной зажим соединен с входом сброса счетчика импульсов, тактовым входом третьего регистра, входом первой ЦЛЗ, входом разрешения первого регистра и через инвертор - с входом сброса триггера и входом разрешения второго регистра, прямой и инверсный выходы триггера соединены с входами тактирования четвертого и пятого регистров соответственно.

Блок калибровки содержит вторую ЦЛЗ, шестой регистр, информационные входы которого соединены с соответствующими выходами второй цифровой линии задержки, а выходы - с соответствующими входами третьего шифратора, выходами связанного с цифровым входом компаратора, выходы которого присоединены к соответствующим входам реверсивного счетчика импульсов, причем реверсивный счетчик своими выходами соединен с входами цифроаналогового преобразователя (ЦАП), выход ЦАП является выходом блока калибровки, а вход второй ЦЛЗ и тактовый вход шестого регистра являются входом блока калибровки.

Первая и вторая ЦЛЗ могут быть выполнены в виде последовательной цепи элементов задержки.

Принцип действия предлагаемого устройства основан на стробировании состояний первой ЦЛЗ во время распространения по ней измеряемого интервала времени, относительно периода импульсов ГУН. Указанные состояния, соответствующие цифровому отсчету фронта и спада интервала времени, запоминаются первым и вторым регистрами, которые тактируются импульсами, вырабатываемыми ГУН Т0. Число полных периодов ГУН, укладывающихся в интервале, фиксируется счетчиком импульсов и запоминается в третьем регистре. Блок калибровки подстраивает частоту ГУН так, чтобы его импульсы, распространяясь по второй ЦЛЗ, проходили определенное количество звеньев второй ЦЛЗ, равное Q, причем значение Q постоянно стремится быть равным константе А, подаваемой на вход компаратора. Данные с выходов измерителя частоты, третьего, четвертого и пятого регистров накапливаются и обрабатываются в решающем блоке.

Код, отражающий длительность интервала, равен:

где N0 - двоичное состояние третьего регистра, N1, N2 - двоичные состояния четвертого и пятого регистров шифраторов, А - константа, подаваемая на вход компаратора в блоке калибровки.

Таким образом, в предлагаемом интерполирующем преобразователе время-код постоянно идет калибровка результата. Оценка измерения выполняется в каждом периоде ГУН, полученное на выходе третьего шифратора число Q, стремящееся быть равным константе А, позволяет оценить текущее в данных условиях значение времени задержки звена второй ЦЛЗ как tD=Т0/А и учесть его при расчете длительности измеряемого интервала.

Перечень чертежей

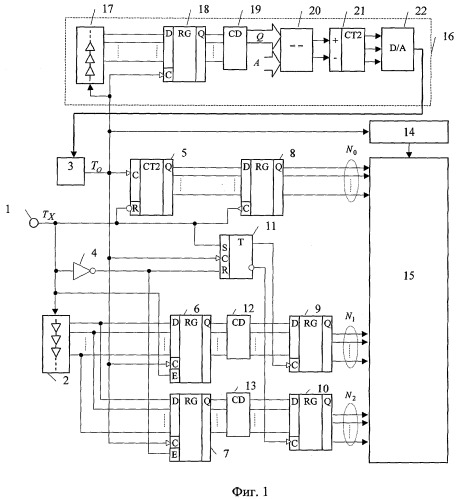

На фиг.1 представлена функциональная схема интерполирующего преобразователя время-код в соответствии с настоящим изобретением.

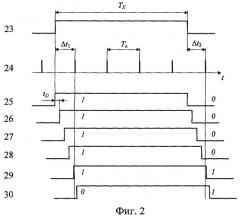

На фиг.2 изображены временные диаграммы сигналов, поясняющие принцип действия интерполирующего преобразователя время-код.

Сведения, подтверждающие возможность осуществления изобретения

Представленная на фиг.1 схема интерполирующего преобразователя время-код содержит входной зажим 1, первую ЦЛЗ 2, генератор, управляемый напряжением 3, инвертор 4, счетчик импульсов 5, первый - пятый регистры 6-10, триггер 11, первый 12 и второй 13 шифраторы, измеритель частоты 14 импульсов, решающий блок 15 и блок калибровки 16, причем соответствующие входы решающего блока 15 подключены к выходам третьего регистра 8, измерителя частоты 14 импульсов, четвертого 9 и пятого 10 регистров, при этом информационные входы четвертого 9 и пятого 10 регистров соединены с соответствующими выходами первого 12 и второго 13 шифраторов, входы которых соединены с выходами первого 6 и второго 7 регистров соответственно, информационные входы которых соединены с соответствующими выходами первой ЦЛЗ 2, а информационные входы третьего регистра 8 соединены с соответствующими выходами счетчика импульсов 5, тактовые входы первого 6 и второго 7 регистров, счетчика импульсов 5, триггера 11, а также входы измерителя частоты 14 импульсов и блока калибровки 16 соединены с выходом генератора, управляемого напряжением 3, вход управления которого соединен с выходом блока калибровки 16, входной зажим 1 соединен с инверсным входом сброса счетчика импульсов 5, тактовым входом третьего регистра 8, тактируемого по спаду, входом установки триггера 11, входом первой ЦЛЗ 2, входом разрешения работы первого регистра 6 и входом инвертора 4, выход которого соединен с входом сброса триггера 11 и входом разрешения работы второго регистра 7, прямой и инверсный выходы триггера соединены с входами тактирования четвертого 9 и пятого 10 регистров соответственно.

Блок калибровки содержит вторую ЦЛЗ 17, шестой регистр 18, информационные входы которого соединены с соответствующими выходами второй ЦЛЗ 17, а выходы - с соответствующими входами третьего шифратора 19. Третий шифратор 19, компаратор 20, реверсивный счетчик 21 и ЦАП 22 подключены последовательно друг за другом, причем выход ЦАП 22 является выходом блока калибровки 16, а вход второй ЦЛЗ 17 и тактовый вход шестого регистра 18 являются входом блока калибровки 16 соединенного с выходом генератора, управляемого напряжением 3.

ЦЛЗ 2 и 17 в предпочтительном варианте осуществления представляют собой последовательную цепь элементов задержки. Элементом задержки может служить любой неинвертирующий логический элемент. В качестве решающего блока может использоваться ЭВМ.

Порядок функционирования устройства (фиг.1) иллюстрируется временными диаграммами, показанными на фиг.2. ГУН 3 непрерывно снабжает вторую ЦЛЗ 17 опорными импульсами 24. На вход компаратора подается константа A, определяющая какое количество звеньев второй ЦЛЗ 17 пройдут импульсы, вырабатываемые ГУН 3. В каждом периоде ГУН 3 комбинация чисел с выхода второй ЦЛЗ 17, в виде термометрического кода, через шестой регистр 18 подается на третий шифратор 19, преобразующий ее в двоичную форму Q. Компаратор 20, сравнивая два числа на своих входах: Q и константу А, вырабатывает признак, на основании которого реверсивный счетчик 21 импульсов складывает или вычитает единицу из своего предыдущего состояния. Состояние реверсивного счетчика 21 импульсов подается на ЦАП 22, который подстраивает частоту ГУН 3 так, чтобы его импульсы, распространяясь по второй ЦЛЗ 17, проходили определенное количество звеньев, равное константе А. Таким образом, число на выходе третьего шифратора 19 Q будет всегда стремиться быть равным константе А. Измерив с помощью измерителя частоты 14 импульсов частоту ГУН 3 и зная, что значение Q постоянно стремится быть равным константе А, находится значение времени задержки звена второй ЦЛЗ 17 как tD=Т0/А, справедливое для двух идентичных ЦЛЗ 2 и 17.

Процесс преобразования инициируется импульсом измеряемой длительности 23 Тx, который начинает распространяться по ЦЛЗ 2 и одновременно разрешает работу счетчика импульсов 5. В моменты появления первых после фронта и спада импульса 23 Тx опорных импульсов 24 от ГУН 3 цифровые состояния отводов 25-30 ЦЛЗ 2 записываются в первый 6 и второй 7 регистры. Записанные в регистры 6 и 7 коды являются термометрическими кодами вида 000…111, либо 111…000. Эти состояния после преобразования в первом 12 и втором 13 шифраторах в прямые двоичные коды отражают погрешности квантования Δt1 и Δt2 24 в начале и конце импульса как двоичные числа N1 и N2, которые запоминаются четвертым 9 и пятым 10 регистрами. Счетчик импульсов 5 к окончанию импульса 23 ТХ достигает состояния N0, запоминаемое третьим регистром 8. Значение на выходе измерителя частоты 14 импульсов и числа N0 с выходов третьего регистра 8, N1 и N2 с выходов четвертого 9 и пятого 10 регистров соответственно, работой которых управляет триггер 11, передаются на соответствующие входы решающего блока 15 для вычисления значения интервала:

Погрешность преобразования складывается из погрешности оценки времени задержки звена второй ЦЛЗ 17 и погрешности оценивания Δt1 и Δt2 24 и составляет:

Таким образом, предлагаемое устройство осуществляет преобразование время-код и одновременно оценивает точность преобразования, компенсируя низкую стабильность при использовании ЦЛЗ.

По сравнению с прототипом предлагаемое устройство обеспечивает более высокую стабильность за счет постоянной оценки точности и калибровки преобразования.

Литература

1. Шляндин В.М. Цифровые измерительные устройства: Учебник для вузов. - М.: Высшая школа, 1981, с.166, рис.3.27.

2. Там же, с.163, рис.3.25.

3. Патент США 4439046, МПК G04 8/00, 27.03.1984 г.

4. Устройство для измерения интервала времени. - Патент РФ №2260830 / Чулков В.А.

1. Интерполирующий преобразователь время-код, содержащий первую цифровую линию задержки, множество выходов которой присоединено к соответствующим информационным входам первого и второго регистров, выходы которых соединены с соответствующими входами первого и второго шифраторов соответственно, а также генератор, управляемый напряжением, выходом подключенный к входу тактирования счетчика импульсов, триггер, вход установки которого соединен с входным зажимом устройства, третий регистр, информационными входами подключенный к соответствующим выходам счетчика импульсов, а выходами - к соответствующим входам решающего блока, отличающийся тем, что в него введены блок калибровки, четвертый и пятый регистры, инвертор и измеритель частоты импульсов, причем соответствующие входы решающего блока подключены к выходам измерителя частоты импульсов, четвертого и пятого регистров, при этом информационные входы четвертого и пятого регистров соединены с соответствующими выходами первого и второго шифраторов, тактовые входы первого и второго регистров, триггера, а также входы измерителя частоты импульсов и блока калибровки соединены с выходом генератора, управляемого напряжением, вход управления которого соединен с выходом блока калибровки, входной зажим соединен с входом сброса счетчика импульсов, тактовым входом третьего регистра, входом первой цифровой линии задержки, входом разрешения первого регистра и через инвертор - с входом сброса триггера и входом разрешения второго регистра, прямой и инверсный выходы триггера соединены с входами тактирования четвертого и пятого регистров соответственно.

2. Интерполирующий преобразователь время-код по п.1, отличающийся тем, что блок калибровки содержит вторую цифровую линию задержки, шестой регистр, информационные входы которого соединены с соответствующими выходами второй цифровой линии задержки, а выходы - с соответствующими входами третьего шифратора, выходами связанного с цифровым входом компаратора, выходы которого присоединены к соответствующим входам реверсивного счетчика импульсов, причем реверсивный счетчик своими выходами соединен с входами цифроаналогового преобразователя, выход цифроаналогового преобразователя является выходом блока калибровки, а вход второй цифровой линии задержки и тактовый вход шестого регистра являются входом блока калибровки.