Способ формирования интегрального сигнала управления для систем автоматического регулирования и устройство для его осуществления

Иллюстрации

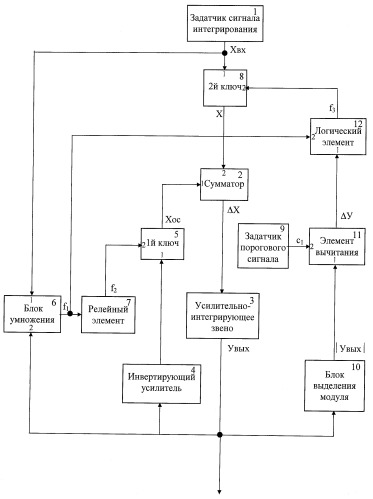

Показать всеИзобретение относится к системам автоматического управления или регулирования линейных или угловых скоростей и может быть использовано в системах автоматического регулирования различных объектов. Достигаемый технический результат - повышение динамической точности и быстродействия устройства. Устройство для осуществления способа формирования интегрального сигнала управления для систем автоматического регулирования содержит задатчик сигнала интегрирования, сумматор, усилительно-интегрирующее звено, инвертирующий усилитель, два ключа, блок умножения, релейный элемент, блок выделения модуля выходного сигнала, задатчик порогового сигнала и логический элемент. 2 н.п. ф-лы, 1 ил.

Реферат

Изобретение относится к системам автоматического управления или регулирования линейных или угловых скоростей и может быть использовано в системах автоматического регулирования различных объектов.

Известны технические решения, в которых применяется процесс интегрирования для достижения требуемого астатизма в системах автоматического управления летательными аппаратами (САУ ЛА).

Основу таких решений составляет введение в контур управления интегрирующего звена, например, по рассогласованию между заданным и текущим значением регулируемой величины (для ЛА этой величиной может быть рассогласование по тангажу, курсу, крену, высоте). В замкнутом контуре регулирования обеспечивается при этом сведение к нулю сигнала на входе интегрирующего звена. Таким образом, при регулировании с интегральным законом по рассогласованию достигается астатизм I-го порядка, установившееся значение регулируемой координаты равно задающему воздействию, рассогласование системы сводится к нулю.

Наиболее близким известным техническим решением (прототипом) является способ интегрирования сигнала управления для астатических систем управления летательными аппаратами и устройство для его осуществления [1]. Этот способ состоит в том, что задают сигнал управления для интегрирования, интегрируют текущий сигнал управления, инвертируют интегрированный сигнал, задают пороговый сигнал ε≥0, перемножают задающий сигнал управления и интегрированный сигнал, формируют сигнал обратной связи, равный инвертированному сигналу при непревышении сигнала перемножения над пороговым сигналом и равный нулю при превышении его и формируют текущий сигнал интегрирования, равный сумме задающего сигнала и сигнала обратной связи.

Устройство по этому способу содержит последовательно соединенные задатчик сигнала интегрирования, сумматор, интегрирующее звено, масштабный усилитель, выход которого соединен с выходом устройства, последовательно соединенные инвертирующий усилитель и управляемый ключ, выход которого соединен со вторым входом сумматора, последовательно соединенные блок умножения, первый и второй входы которого соединены соответственно с входом и выходом устройства, и релейный элемент, выход которого соединен со вторым входом управляемого ключа, а также задатчик порогового сигнала.

Существенными признаками прототипа-способа, совпадающими с существенными признаками предлагаемого технического решения, являются следующие признаки: способ формирования интегрального сигнала управления для систем автоматического регулирования включает задание сигнала управления для интегрирования, суммирование входного сигнала интегрирования и сигнала обратной связи, усиление суммарного сигнала, формирование выходного сигнала посредством интегрирования усиленного суммарного сигнала, усиление и инвертирование выходного сигнала, перемножение задающего сигнала управления и выходного сигнала и формирование сигнала обратной связи, равного усиленному инвертированному выходному сигналу при отрицательной полярности сигнала перемножения, и задание порогового сигнала.

Существенными признаками прототипа-устройства, совпадающими с существенными признаками предлагаемого технического решения являются следующие признаки: устройство формирования интегрального сигнала управления для систем автоматического регулирования также содержит задатчик сигнала интегрирования и последовательно соединенные сумматор, усилительно-интегрирующее звено, выход которого соединен с выходом устройства, инвертирующий усилитель и первый ключ, выход которого соединен с первым входом сумматора, последовательно соединенные блок умножения, первый и второй входы которого соединены соответственно с выходом задатчика сигнала интегрирования и выходом устройства, и релейный элемент, выход которого соединен со вторым входом первого ключа, и задатчик порогового сигнала.

Недостатками известных решений являются невысокая динамическая точность при отработке сигналов с изменяющейся полярностью, обусловленная затянутостью процесса списывания интегрального сигнала предшествующей полярности, так как при смене знака сигнала на входе устройства сигнал на его выходе не изменит знак, пока наинтегрированный ранее сигнал не спишется до нуля.

Технической задачей, решаемой в предлагаемом изобретении, является повышение динамической точности и расширение функциональных возможностей системы автоматического регулирования.

Указанный технический результат достигается тем, что в известном способе формирования интегрального сигнала управления для систем автоматического регулирования, включающем задание сигнала управления для интегрирования, суммирование входного сигнала интегрирования и сигнала обратной связи, усиление суммарного сигнала, формирование выходного сигнала посредством интегрирования усиленного суммарного сигнала, усиление и инвертирование выходного сигнала, перемножение задающего сигнала управления и выходного сигнала и формирование сигнала обратной связи, равного усиленному инвертированному выходному сигналу при отрицательной полярности сигнала перемножения, а также задание порогового сигнала, дополнительно выделяют сигнал модуля выходного сигнала, формируют разностный сигнал между сигналом модуля и пороговым и формируют входной сигнал суммирования, равный заданному сигналу управления при несовпадении полярностей сигнала перемножения и разностного, при этом коэффициент усиления инвертирующего усилителя в цепи обратной связи Ку составляет

где Kyи - коэффициент усиления суммарного сигнала в прямой цепи, Т0 - заданная постоянная времени процесса списывания выходного сигнала.

Указанный технический результат достигается также тем, что известное устройство формирования интегрального сигнала управления для систем автоматического регулирования, содержащее задатчик сигнала интегрирования и последовательно соединенные сумматор, усилительно-интегрирующее звено, выход которого соединен с выходом устройства, инвертирующий усилитель и первый ключ, выход которого соединен с первым входом сумматора, последовательно соединенные блок умножения, первый и второй входы которого соединены соответственно с выходом задатчика сигнала интегрирования и выходом устройства, и релейный элемент, выход которого соединен со вторым входом первого ключа, и задатчик порогового сигнала, дополнительно содержит второй ключ, первый вход которого соединен с выходом задатчика сигнала интегрирования, а выход - со вторым входом сумматора, последовательно соединенные блок выделения модуля, вход которого соединен с выходом устройства, элемент вычитания, второй вход которого соединен с выходом задатчика порогового сигнала, и логический элемент, второй вход которого соединен с выходом блока умножения, а выход - со вторым входом второго ключа, при этом коэффициент усиления инвертирующего усилителя в цепи обратной связи Ку составляет

где Kуи - коэффициент усиления суммарного сигнала в прямой цепи, Т0 - заданная постоянная времени процесса списывания выходного сигнала.

Отличительными признаками предлагаемого технического решения - Способа формирования интегрального сигнала управления для систем автоматического регулирования - является то, что способ включает выделение сигнала модуля выходного сигнала, формирование разностного сигнала между сигналом модуля и пороговым сигналом и формирование входного сигнала суммирования, равного заданному сигналу управления при несовпадении полярностей сигнала перемножения и разностного сигнала, при этом коэффициент усиления инвертирующего усилителя в цепи обратной связи Ку составляет

где Kуи - коэффициент усиления суммарного сигнала в прямой цепи, Т0 - заданная постоянная времени процесса списывания выходного сигнала.

Отличительными признаками предлагаемого технического решения - Устройства формирования интегрального сигнала управления для систем автоматического регулирования - является то, что устройство дополнительно содержит второй ключ, первый вход которого соединен с выходом задатчика сигнала интегрирования, а выход - со вторым входом сумматора, последовательно соединенные блок выделения модуля, вход которого соединен с выходом устройства, элемент вычитания, второй вход которого соединен с выходом задатчика порогового сигнала, и логический элемент, второй вход которого соединен с выходом блока умножения, а выход - со вторым входом второго ключа, при этом коэффициент усиления инвертирующего усилителя в цепи обратной связи Ку составляет

где Kуи - коэффициент усиления суммарного сигнала в прямой цепи, Т0 - заданная постоянная времени процесса списывания выходного сигнала.

Предложенные способ формирования сигнала управления для систем автоматического регулирования и устройство для его осуществления, как показывает проведенное математическое моделирование, позволяют расширить функциональные возможности управления (т.е. дают возможность отрабатывать интенсивные быстро меняющиеся сигналы управления) и повысить при этом точность управления. По существу, сформированы четыре взаимосвязанных канала, обеспечивающие в целом достаточно точное управление быстро меняющимися процессами.

Способ формирования сигнала управления для систем автоматического регулирования и устройство для его осуществления могут найти применение, например, в системах управления маневренными летательными аппаратами, к которым одновременно предъявляются достаточно высокие требования по точности управления и по быстродействию.

На чертеже представлена блок-схема устройства формирования интегрального сигнала управления для систем автоматического регулирования с реализацией предложенного способа.

Устройство формирования интегрального сигнала управления содержит задатчик сигнала интегрирования 1, последовательно соединенные сумматор 2, усилительно-интегрирующее звено 3, выход которого соединен с выходом устройства, инвертирующий усилитель 4 и первый ключ 5, выход которого соединен с первым входом сумматора, последовательно соединенные блок умножения 6, первый и второй входы которого соединены соответственно с выходом задатчика сигнала интегрирования и выходом устройства, и релейный элемент 7, выход которого соединен со вторым входом первого ключа, второй ключ 8, первый вход которого соединен с выходом задатчика сигнала интегрирования, а выход - со вторым входом сумматора, задатчик порогового сигнала 9 и последовательно соединенные блок выделения модуля 10, вход которого соединен с выходом устройства, элемент вычитания 11, второй вход которого соединен с выходом задатчика порогового сигнала, и логический элемент 12, второй вход которого соединен с выходом блока умножения, а выход - со вторым входом второго ключа.

Устройство формирования интегрального сигнала управления для систем автоматического регулирования работает следующим образом.

В устройстве сформированы четыре канала:

- прямой интегральный канал управления, включающий задатчик сигнала интегрирования 1, сумматор 2 и усилительно-интегрирующее звено 3;

- канал обратной связи, состоящий из инвертирующего усилителя 4, вход которого соединен с выходом усилительно-интегрирующего звена 3, и первого ключа 5, выход которого соединен с первым входом сумматора 2. Канал обеспечивает введение обратной связи к прямому каналу для ускоренного списывания наинтегрированного сигнала при смене полярности входного сигнала;

- логический канал, управляющий работой устройства по подключению и отключению обратной связи через ключ 5. Он включает в себя блок умножения 6 и релейный элемент 7;

- канал, обеспечивающий ограничение выходного интегрированного сигнала и управляющий корректным выходом на ограничение и "сходом" с ограничения этого сигнала. Этот канал включает в себя второй ключ 8, первый вход которого соединен с выходом задатчика сигнала интегрирования 1, а выход - со вторым входом сумматора 2, задатчик порогового сигнала 9 и последовательно соединенные блок выделения модуля 10, вход которого соединен с выходом устройства, элемент вычитания 11, второй вход которого соединен с выходом задатчика порогового сигнала, и логический элемент 12, второй вход которого соединен с выходом блока умножения 6, а выход - со вторым входом второго ключа.

При включении устройства и начале его работы с нуля, т.е. при выходном сигнале блока 1 (входном сигнале устройства) xвx=0, сигналы на выходах сумматора 2, усилительно-интегрирующего звена 3 и инвертирующего усилителя 4 равны 0. Ключи 5 и 8 нормально замкнуты.

Рассмотрим работу системы при задании сигнала блоком 1 xвx>0. Второй ключ 8 замкнут, так как:

- на выходе усилительно-интегрирующего звена 3 имеем сигнал увых=0;

- на выходе блока 10 сигнал ;

- на выходе элемента 11 сигнал равен

и Δу<0, т.к. выходной сигнал задатчика порогового сигнала c1=const>0.

На входах логического элемента 12 один входной сигнал Δу<0, второй входной сигнал f1 с выхода блока умножения 6

Следовательно, выходной сигнал этого элемента f3=0, т.к. логика функционирования этого звена имеет вид

Таким образом, на рассматриваемой фазе процесса сигнал на входе сумматора х=xвх. Сигнал х, проходя через сумматор и усилительно-интегрирующее звено, определяет появление выходного сигнала увых>0. Сигнал f1=xвx·yвых>0 с выхода блока умножения 6 поступает на вход релейного элемента 7, статическая характеристика которого определена в виде:

где f2 - сигнал на выходе релейного элемента 7; поскольку в данном случае имеем f2=1, ключ 5 размыкается и сигнал обратной связи хoс=0. Устройство в целом начинает работать в режиме прямого интегрирования входного сигнала. Выходной сигнал увых формируется в виде:

где Куи - коэффициент усиления блока 3,

Δx - сигнал на выходе сумматора 2:

Сигнал обратной связи xос, коммутируемый первым ключом 5, определяется:

где Ку - передаточный коэффициент инвертирующего усилителя 4, определяемый из соотношения

где Т0 - постоянная времени желаемого экспоненциального закона списывания наинтегрированного сигнала.

Процесс прямого интегрирования сигнала xвx>0 продолжается:

- либо до смены знака сигнала xвx,

- либо до достижения выходным сигналом yвых заданной величины c1,

определенной в задатчике порогового сигнала 9.

Рассмотрим эти варианты.

В первом случае выходной сигнал устройства yвых не достиг ограничения c1, а задающий сигнал сменил полярность, т.е. xвx<0. При этом подключится канал обратной связи, состоящий из блоков 4 и 5, так как на выходе блока умножения 6 сигнал f1 станет отрицательным, сигнал f2 в соответствии с (4) примет значение 0, и первый ключ 5 замкнет канал обратной связи. В соответствии с (6), (7) будет обеспечено ускоренное списывание положительного выходного сигнала yвых с постоянной времени не более Т0. Одновременно в соответствии с (5) усилительно -интегрирующее звено 3 интегрирует сигнал новой - отрицательной - полярности, и сигнал увых достигает отрицательных значений. С этого момента, поскольку xзад<0 и yвых<0, f1>0, f2=1, ключ 5 размыкается и начинается процесс прямого интегрирования отрицательного входного сигнала х=xзад<0.

Во втором случае при xзад>0 сигнал увых достигает величины c1. На выходе элемента вычитания 11 в соответствии с (1) получаем Δу≥0. Поскольку при xзад>0 и yвых>0 на выходе блока умножения 6 имеем сигнал f1>0, на выходе логического элемента 12 в соответствии с (3) имеем f3=1.

При этом ключ 8 размыкается, сигнал х становится равным нулю, а поскольку ключ 5 при xзад>0 и yвых>0 также разомкнут, на входе усилительно-интегрирующего звена 3 имеем Δх=0, и процесс интегрирования останавливается, причем выходной сигнал увых равен заданному ограничению c1.

Ключ 8 замкнется вновь, как только сменится знак xзад, так как сигнал на выходе блока умножения f1 станет отрицательным; при этом разомкнется ключ 5 и будет обеспечено ускоренное списывание положительного выходного сигнала увых с постоянной времени не более Т0.

Логика протекания процессов в устройстве при отрицательном значении заданного сигнала xзад аналогична описанной выше для xзад>0, что обеспечивается наличием блока выделения модуля 10.

Все составные звенья для реализации способа и устройства могут быть реализованы на современных элементах автоматики и вычислительной техники, например, по [2, стр.103], а также программно-алгоритмически.

Источники информации.

1. Способ формирования интегрального сигнала управления для астатических систем управления ЛА и устройство для его осуществления. Патент РФ №2275675, G06F 7/38, G05B 13/00, 2006 г.

2. А.У.Ялышев, О.И.Разоренов. Многофункциональные аналоговые регулирующие устройства автоматики. М.: Машиностроение, 1981.

1. Способ формирования интегрального сигнала управления для систем автоматического регулирования, включающий формирование заданного сигнала интегрирования, суммирование заданного сигнала интегрирования и сигнала обратной связи, полученного путем усиления и инвертирования выходного сигнала, формирование выходного сигнала посредством интегрирования усиленного суммарного сигнала, формирование сигнала умножения заданного сигнала интегрирования и выходного сигнала, подключение сигнала обратной связи при отрицательной полярности сигнала умножения, и задание порогового сигнала, отличающийся тем, что выделяют сигнал модуля выходного сигнала, формируют разностный сигнал между сигналом модуля выходного сигнала и пороговым сигналом подключают заданный сигнал интегрирования на вход сумматора при несовпадении полярностей сигнала умножения заданного сигнала интегрирования и выходного сигнала и разностного сигнала, при этом коэффициент усиления инвертирующего усилителя в цепи обратной связи Kу составляет ,где Kуи - коэффициент усиления при интегрировании суммарного сигнала в прямой цепи, Т0 - заданная постоянная времени процесса списывания выходного сигнала.

2. Устройство формирования интегрального сигнала управления для систем автоматического регулирования, содержащее задатчик сигнала интегрирования и последовательно соединенные сумматор, усилительно-интегрирующее звено, выход которого соединен с выходом устройства, инвертирующий усилитель и первый ключ, выход которого соединен с первым входом сумматора, последовательно соединенные блок умножения, первый и второй входы которого соединены соответственно с выходом задатчика сигнала интегрирования и выходом устройства, и релейный элемент, осуществляющий замыкание первого ключа при подаче на него сигнала с отрицательной полярностью, выход которого соединен со вторым входом первого ключа, и задатчик порогового сигнала, отличающееся тем, что оно содержит второй ключ, первый вход которого соединен с выходом задатчика сигнала интегрирования, а выход - со вторым входом сумматора, последовательно соединенные блок выделения модуля, вход которого соединен с выходом устройства, элемент вычитания, второй вход которого соединен с выходом задатчика порогового сигнала, и логический элемент, осуществляющий замыкание второго ключа, если полярность сигналов, поданных на его первый и второй входы, не совпадают, при этом второй вход логического элемента соединен с выходом блока умножения, а выход - со вторым входом второго ключа, при этом коэффициент усиления инвертирующего усилителя в цепи обратной связи Ky составляет где Kуи - коэффициент усиления при интегрировании суммарного сигнала в прямой цепи, Т0 - заданная постоянная времени процесса списывания выходного сигнала.