Устройство для преобразования из полиномиальной системы классов вычетов в позиционный код

Иллюстрации

Показать всеИзобретение относится к вычислительной технике, в частности к модулярным спецпроцессорам (СП), функционирующим в полиномиальной системе классов вычетов (ПСКВ) и способным сохранять работоспособное состояние при возникновении ошибки за счет реконфигурации структуры.

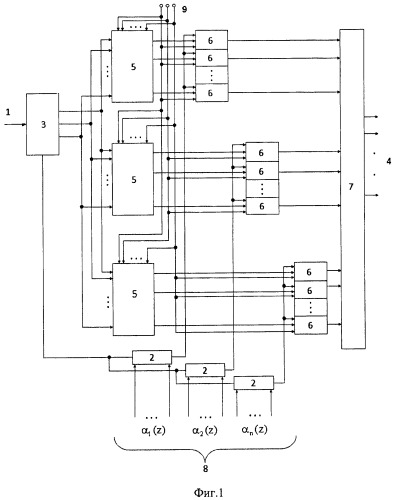

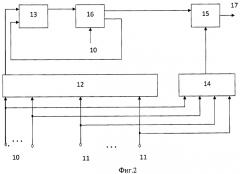

Техническим результатом является расширение функциональных возможностей, за счет возможности вычисления значений ортогональных базисов при возникновении отказов вычислительных трактов по модулю pi(z) и их исключении из процесса преобразования модульного кода ПСКВ в двоичный позиционный код. Устройство содержит вход (1) запуска устройства, группу сдвиговых регистров (2), блок (3) синхронизации, выход (4) устройства, группу блоков (5) расчета ортогональных базисов, блоки (6) трехвходовых элементов И, сумматор (7) по модулю два, группу информационных входов (8), группу управляющих входов (9) устройства, группу синхровходов (10), группу управляющих входов (11), при этом группа блоков расчета ортогональных базисов содержит первый блок памяти (12), умножитель (13), второй блок памяти (14), умножитель (15), регистр 16, выход регистра (17). 2 ил., 2 табл.

Реферат

Изобретение относится к вычислительной технике, в частности к модулярным спецпроцессорам (СП), функционирующим в полиномиальной системе классов вычетов (ПСКВ) и способным сохранять работоспособное состояние при возникновении ошибки за счет реконфигурации структуры.

Известно устройство для преобразования числа из системы остаточных классов в позиционный код (Авторское свидетельство №2298873, кл., Н03М 7/18, 10.05.2007. Бюл. №13), которое содержит вход запуска устройства, группу информационных входов, группу сдвиговых регистров, блок синхронизации, группу блоков памяти, блоки элементов И, накапливающий сумматор, выход устройства.

Техническим результатом изобретения является расширение функциональных возможностей, проявляющееся в возможности вычисления значений ортогональных базисов при возникновении отказов вычислительных трактов по модулю pi(z) и их исключении из процесса преобразования модулярного кода ПСКВ в двоичный позиционный код при меньших аппаратурных затратах по сравнению с прототипом.

Указанный технический результат достигается за счет ввода в конструкцию группы блока расчета ортогональных базисов, структура которого отличается от прототипа меньшими схемными затратами, и сумматора по модулю два.

Устойчивость структуры вычислительного устройства к дефектам аппаратуры обеспечивает возможность работы спецпроцессора в режиме постепенной деградации. Указанное свойство обеспечивает высокую живучесть СП и является одним из основных факторов, на которых базируются разработки способов построения систем, способных деградировать постепенно. Применение полиномиальной системы классов вычетов позволяет реализовать построение живучих вычислительных систем с постепенной деградацией структуры.

Одним из основных достоинств модулярных кодов, к которым относится и ПСКВ, являются обменные операции. Алгоритмической основой обменных операций между точностью, производительностью и корректирующими способностями являются независимость обработки информации по каждому модулю и функциональная равноправность разрядов. Данные свойства обусловлены полной арифметичностью кодовых конструкций, базирующихся па модулярном представлении чисел, где информационная и контрольные части равноправны относительно любой модульной операции.

Согласно общей теории кодирования мощность модулярного кода определяется соответствием каждому действительному операнду A(z) множества М, A(z)∈M слова (α1(z), α2(z) … αn(z))∈=Рполн(z), где Рполн(z) - декартово произведение некоторых оснований множества, p1(z), р2(z), …, pn(z) αi(z)∈pi(z); i=1, 2, …, n. Если на диапазон возможного изменения кодируемого множества M(z) наложить ограничения, считая, что для однозначного представления достаточно k первых остатков (k<n), то соответствующие им основания упорядоченной системы классов вычетов p1(z), p2(z), …, pk(z); i=1, 2, …, k принадлежат множеству информационных модулей. В этом случае диапазон однозначного представления по данным основаниям соответственно равен

Оставшиеся r=n-k «лишних остатка» можно считать избыточными, так как их исключение из модульной кодовой конструкции (α1(z), α2(z), … αn(z)) не влечет за собой ущерба однозначности представления числа А(z), то есть при отказе r каналов их можно просто удалить из процессора, не оказывая влияния на точность выполнения задания. Но с другой стороны, данные r избыточных каналов предопределяют корректирующие способности вычислительной системы, другими словами, гарантию защиты от недостоверного результата.

Таким образом, изменяя количество информационных k и избыточных r оснований в заданной структуре непозиционного СП, можно варьировать его основными показателями - точностью, информационной надежностью и производительностью вычислительной системы.

Для перевода числа из полиномиальной системы классов в вычетов позиционный код используется китайская теорема об остатках (КТО), согласно которой

где Bi(z) - ортогональный базис i-го основания.

Ортогональный базис определяется как

где mi(z) - вес ортогонального базиса i-го основания.

Применение mi(z) позволяет обеспечить выполнение условия

Bi(z)≡1 mod pi(z).

Преобразуем выражение (2) к виду

Подставив равенство (3) в выражение (1), получаем

Разделив обе части последнего равенства на величину Р,

получаем

Принимая во внимание попарную простоту модулей pi(r), i=1, 2, …, k+r, введем обозначение

Тогда

Таким образом, очевидно, что величина веса ортогонального базиса определяется произведением величин, обратных основаниям ПСКВ pj(z) по модулю pi(z).

Значит для пересчета ортогональных базисов при построении СП ПСКВ с реконфигурируемой структурой необходимо использовать значения , т.е. обратных величин оснований pj(z) по модулю pi(z) для поля GF(24). В таблице 1 представлены величины для поля GF(24).

| Таблица 1 | |||||

| Величины для поля GF(24). | |||||

| Значение pi(z) основания ПСКВ | |||||

| p1(z) | p2(z) | p3(z) | p4(z) | p5(z) | |

| - | 1 | 1 | 1 | 1 | |

| z | - | z | z+1 | 1 | |

| z3+z | z3+1 | - | z2+7 | z3+z2+1 | |

| z3 | z3+z2+z | z2 | - | z3+z+1 | |

| z3+z2+z | z2+z | z3+z | z3+z2 | - |

Устройство содержит вход 1 запуска устройства, группу сдвиговых регистров 2, блок 3 синхронизации, выход 4 устройства, группу блоков 5 расчета ортогональных базисов, блоки 6 трехвходовых элементов И, сумматор 7 по модулю два, группу информационных входов 8, группу управляющих входов 9 устройства. Структура устройства показана на фиг.1.

Вход 1 запуска устройства соединен с входом запуска блока 3 синхронизации, выход которого соединен с входами разрешения сдвига сдвиговых регистров группы 2, информационные входы которых являются соответствующими информационными входами 8 группы устройства, выход i-го сдвигового регистра группы 2 соединен с первым входом элемента И i-ой группы (i=1, 2, …, n) блоков 6 трехвходовых элементов И. Выходы блока 3 синхронизации также подключены к первому входу блоков 5 расчета ортогональных базисов, второй вход которых подключен к управляющим входам устройства 9, выход i-го блока расчета ортогональных базисов 5 подключены ко второму входу элементов И 1-го блока 6, третьи входы которых соединены с соответствующим управляющим входом группы 9, выходы элементов И блока 6 соединены со входами сумматора 7 по модулю два, выход которого является выходом устройства 4.

С целью сокращения аппаратных затрат в блоках 5 расчета ортогональных базисов вместо (n-2) умножителей по модулю pi(z), где i=1, 2, …, n, используемых в прототипе, устанавливаем один умножитель по модулю и один регистр.

Блок расчета ортогональных базисов содержит синхровходы 10, n управляющих входов 11, первый блок памяти 12, умножитель 13 по модулю pi(z), где i=1, 2, …, n, второй блок памяти 14, умножитель 15, регистр 16, выход 17 блока. Структура блока показана на фиг.2.

Синхровходы 10 подключены к синхровходам первого 12 блока памяти, второго 14 блока памяти и регистра 16, а управляющие входы 11 подключены к адресным входам первого 12 блока памяти и второго 14 блока памяти. Первый вход умножителя 13 по модулю pi(z) подключен к выходу первого 12 блока памяти, а второй вход умножителя по модулю pi(z) подсоединен ко второму выходу регистра 16, вход которого соединен с выходом умножителя 13 по модулю pi(z). Первый вход умножителя 15 соединен с первым выходом регистра 16, а второй вход умножителя 15 подключен к выходу второго 14 блока памяти. Выход умножителя 15 является выходом 17 блока расчета ортогональных базисов.

Число, представляемое в коде ПСКВ, A(z)=(α1(z), α2(z), …, αn(z)), через группу информационных входов 8 заносится на сдвиговые регистры 2 группы, причем вычеты по каждому из оснований ПСКВ заносятся в свой регистр 2. Работа устройства происходит по тактам. В каждом такте содержимое регистров 2 сдвигается вправо (в сторону младших разрядов) на один разряд. Алгоритм работы устройства может быть представлен в виде

где n - количество оснований ПСКВ;

ni=ord pi(z) - степень i-го основания ПСКВ;

αi g={0, 1} - значение g-го разряда, i-го основания ПСКВ;

Bi *(z) - пересчитанное значение i-го ортогонального базиса.

Из выражения (6) видно, что устройство реализует операцию последовательного суммирования произведений пересчитанных ортогональных базисов Bi *(z) назначения остатка αi(z), представленного в двоичном коде.

Группа блоков 5 осуществляет расчет ортогональных базисов zg·Bi *(z) в соответствии со значениями, поданными на п управляющих входов 9 устройства.

В первом такте по сигналу из блока 3 синхронизации производится выдача величины из блоков 5 параллельно и в случае открытых блоков трехвходовых элементов И группы 6 - прибавление их к содержимому сумматора 7, работающего по модулю два. В следующем такте содержимое каждого из регистров 2 сдвигается на один разряд вправо, и блок 3 синхронизации разрешает выдачу очередного пересчитанного значения из блоков 5.

Работа устройства осуществляется в течении s тактов, где s=v, для расширенного поля Галуа GF(2v),

Если i-ый канал модулярного вычислительного устройства является работоспособным, то по соответствующему входу группы управляющих входов 9 поступает значение 1, в противном случае - значение 0.

Блок 5 расчета ортогональных базисов групп работает следующим образом. При поступлении первого синхросигнала от блока 3 синхронизации на вход 10 из первого блока памяти 12 на первый вход умножителя 13 по модулю pi(z) подаются первое значение , которое умножается на единицу и подается на вход регистра 16. При приходе второго синхросигнала на вход 10 данный результат поступает на второй вход умножителя 13, на первый вход которого подается значение второе значение .

Спустя n-1 тактов на выходе регистра 16 появляется значение веса ортогонального базиса mi(z). Таким образом определяется значение

Причем величины определяются значением сигнала, поступающего с j-го управляющего входа 11, согласно условия

Значения , поступающие с первого блока 12 памяти, определяются значениями сигналов, подающихся на адресные входы блока 12 с управляющих входов 11 и синхровходов 10. Причем

где yj - сигнал на j-ом входе управляющих входов 11.

Вычисленное значение mi *(z) веса ортогонального базиса по i-ому основанию согласно выражения (7) поступает на первый вход умножителя 15, на второй вход которого с выходов второго блока 14 памяти подается значение

где l∈Uoтк; Uoтк - множество отказавших оснований в процессе функционирования вычислительной системы ПСКВ; g=0, 1, …, ord pi(z)-1.

Полученное значение Р*(z) определится значением сигнала, поступающего на адресные входы второго блока 14 памяти с управляющих входов 11 и синхровходов 10. Во втором блоке 14 памяти хранятся константы произведения zg·P*(z).

Умножитель 15 осуществляет вычисление величины ортогонального базиса

Полученное значение ортогонального базиса согласно (11) подается на выход 17, который является выходом блока 5 расчета ортогональных базисов.

Если в процессе функционирования вычислительной системы ПСКВ откажет b основание, то на управляющих вxодах 9 появится сигнал

(y1, …, yb-1, yb, yb+1, …, yn)=(1, …, 1, 0, 1, …, 1).

Данный сигнал поступает на управляющие входы 11 блоков 5 расчета ортогональных базисов. Под управлением данного сигнала из первого блока 12 памяти значения , (j=1, …, n, j≠i), a (n-2) умножителей 13 по модулю два вычисляет

где .

Под управлением сигналов, поступивших с управляющих входов 11 и синхровходов 10, из второго блока 14 памяти поступают значения, определенные выражением (10). Умножитель 15 реализует выражение (11), где

Одновременно с этим значения (y1, …, yb-1, yb, yb+1, …, yn)=(1, …, 1, 0, 1, …, 1) подаются на третьи входы 6 элементов И блоков 6. Нулевой сигнал yb=0 производит закрытие элементов И b-го блока 6. Таким образом, значения αb(z)·Вb(z) в получении конечного результата согласно (6) не участвуют, так как на сумматор 7 они не подаются.

Рассмотрим пример.

Необходимо вычислить значения ортогональных базисов полиномиальной системы классов вычетов, задаваемой в поле GF(24). Для этого поля определены следующие основания p1(z)=z+1, p2(z)=z2+z+1, p3(z)=z4+z3+z2+z+1, p4(z)=z4+z3+1, p5(z)=z4+z+1.

Согласно (2) определяем значения Pi(z)

P1(z)=p2(z)p3(z)p4(z)p5(z)=z14+z13+z12+z11+z10+z9+z8+z7+z6+z5+z4+z3+z2+z+1;

P2(z)=p1(z)p3(z)p4(z)p5(z)=z13+z12+z10+z9+z7+z6+z4+z3+z+1;

P3(z)=p1(z)p2(z)p4(z)p5(z)=z11+z10+z6+z5+z+1;

P4(z)=p1(z)p2(z)p3(z)p5(z)=z11+z10+z9+z8+z6+z4+z3+1;

P5(z)=p1(z)p2(z)p3(z)p4(z)=z1l+z8+z7+z5+z3+z2+z+1.

Для выполнения условия Bi(z)=1modpi(z) вычислим значения весов ортогональных базисов. Получаем m1(z)=1; m2(z)=z; m3(z)=z3+z; m4(z)=z3; m5(z)=z.

Определим значения m1(z), воспользовавшись равенством (5). Тогда

m1(z)=1; m2(z)=z2(z+1)mod(z2+z+1)=z;

m3(z)=[(z3+z)(z3+1)(z2+1)(z3+z2+1)]mod(z4+z3+z2+z+1)=z3+z;

m4(z)=[z5(z3+z+1)(z3+z2+z+1)]mod(z4+z3+1)=z3;

m5(z)=[(z3+z2+z)(z3+z)(z2+z)(z3+z2)]mod(z4+z+1)=z.

Рассмотрим работу группы блока 5 расчета ортогональных базисов на примере блока 5, функционирующего по модулю р3(z)=z4+z3+z2+z+l. При поступлении первого сигнала по входу 10 с выхода первого блока памяти 12 на первый вход умножителя 13 по модулю р3(z)=z4+z3+z2+z+1 подается значение , которое умножается на 1 и записывается в регистр 16. Так как все вычислительные каналы, определяемые основаниями ПСКВ, находятся в работоспособном состоянии, то в процессе функционирования вычислительной системы ПСКВ на управляющих входах 9 появится сигнал

(y1, y2, y2, y4, y5)=(1, 1, 1, 1, 1),

который поступает на группу управляющих входов 11 блока 5 расчета ортогональных базисов.

При поступлении второго сигнала по входу 10 с выхода первого блока памяти 12 на первый вход умножителя 13 по модулю p3(z)=z4+z3+z2+z+1 подается значение , которое умножается на значение , поступившее на второй вход умножителя 13 по модулю p3(z)=z4+z3+z2+z+1. Данное значение было записано в регистре 16 и поступило на второй вход умножителя 13 по модулю p3(z)=z4+z3+z2+z+1 при поступлении второго синхросигнала 10. В результате на выходе умножителя 13 по модулю p3(z)=z4+z3+z2+z+1 получается результат который записывается в регистр 16.

При поступлении третьего сигнала по входу 10 с выхода первого блока памяти 12 на первый вход умножителя 13 по модулю p3(z)=z4+z3+z2+z+1 подается значение которое умножается на значение поступившее на второй вход умножителя 13 по модулю p3(z)=z4+z3+z2+z+1. Данное значение было записано в регистре 16 и поступило на второй вход умножителя 13 по модулю p3(z)=z4+z3+z+z+1 при поступлении третьего синхросигнала 10. В результате на выходе умножителя 13 по модулю p3(z)=z4+z3+z2+z+1 получается результат который записывается в регистр 16.

При поступлении четвертого сигнала по входу 10 с выхода первого блока памяти 12 на первый вход умножителя 13 по модулю p3(z)=z4+z3+z2+z+1 подается значение которое умножается на значение поступившее на второй вход умножителя 13 по модулю p3(z)=z4+z3+z2+z+1. Данное значение было записано в регистре 16 и поступило на второй вход умножителя 13 по модулю p3(z)=z4+z3+z2+z+1 при поступлении четвертого синхросигнала 10. В результате на выходе умножителя 13 по модулю p3(z)=z4+z3+z2+z+1 получается результат

Полученное значение с первого выхода регистра 16 подается на вход умножителя 15, на второй вход которого подается значение Р3(z)=p1(z)p2(z)p4(z)p5(z)=z11+z10+z6+z5+z+1 с выхода второго блока памяти 14. Данное значение будет определяться управляющим сигналом

(y1, y2, y2, y4, y5)=(1, 1, 1, 1, 1),

который поступает на входы второго блока памяти 14 с группы управляющих входов 11 блока 5 расчета ортогональных базисов. В результате значение ортогонального базиса будет равно B3(z)=z14+z13+z12+z1l+z9+z8+z7+z6+z4+z3+z2+z.

Остальные блоки 5 расчета ортогональных базисов работают аналогичным образом.

В таблице 2 представлены ортогональные базисы исходной системы ПСКВ, в которой все основания являются работоспособными.

| Таблица 2 | |

| Ортогональные базисы | |

| Ортогональные базисы | Веса |

| B1(z)=z14+zl3+z12+z11+z10+z9+z8+z7+z6+z5+z4+z3+z2+z+1 | mi(z)=l |

| B2(z)=z14+z13+z11+zl0+z8+z7+z5+z4+z2+z | m^(z)=z |

| В3(z)=z14+z13+z12+z11+z9+z8+z7+z6+z4+z3+z2+z | ms(z)=z+z |

| В4(z)=z14+z13+z12+z11+z9+z7+z6+z3 | m4(z)=z3 |

| B5(z)=z12+z9+z8+z6+z4+z3+z2+z | ms(z)=z |

Полученные данные совпадают с контрольным просчетом.

Рассмотрим процедуру постепенной деградации структуры не позиционного процессора ПСКВ. Допустим, что в процессе функционирования отказало последнее основание p5(z)=z4+z+1. Тогда диапазон представления входные данных составит P1234(z)=zl1+z8+z7+z5+z3+z2+z+1.

При этом ортогональные базисы и соответствующие им веса составят

B1 1234(z)=z10+z9+z8+z6+z5+z2+1; m1 1234(z)=1.

B2 1234(z)=z10+z9+z6+z5+z4+z; m2 1234(z)=z.

B3 l234(z)=z9+z8+z6+z2; m3 1234(z)=z2.

B4 1234(z)=z9+z6+z4+z; m4 1234(z)=z2+z.

Для перерасчета ортогональных базисов определим значения

P1 1234(z)=z10+z9+z8+z6+z5+z2+1; m1 1234(z)=1;

P2 1234(z)=z9+z8+z5+z4+z3+1; m2 1234(z)=[z2(z+1)]mod z2+z+1=z.

P3 1234(z)=z7+z6+z4+1;

m3 1234(z)=[(z3+z)(z3+1)(z2+1)]mod(z4+z3+z2+z+1)=z2;

P4 1234(z)=z7+z6+z5+z2+z+1;

m1 1234(z)=[z5(z3+z+1)]mod(z4+z3+1)=z2+z.

Так как произошел отказ пятого вычислительного канала, определяемого основанием ПСКВ p5(z)=z4+z+1, а все остальные находятся в работоспособном состоянии то в процессе функционирования вычислительной системы ПСКВ на управляющих входах 9 появится сигнал

(y1, y2, y3, y4, y5)=(1, 1, 1, 1, 0),

который поступает на группу управляющих входов 11 блока 5 расчета ортогональных базисов.

Рассмотрим работу группы блока 5 расчета ортогональных базисов на примере блока 5, функционирующего по модулю p3(z)=z4+z3+z2+z+1. При поступлении первого сигнала по входу 10 с выхода первого блока памяти 12 на первый вход умножителя 13 по модулю p3(z)=z4+z3+z2+z+1 подается значение которое умножается на 1 и записывается в регистр 16.

При поступлении второго сигнала по входу 10 с выхода первого блока памяти 12 на первый вход умножителя 13 по модулю p3(z)=z4+z3+z2+z+1 подается значение которое умножается на значение поступившее на второй вход умножителя 13 по модулю р3(z)=z4+z3+z2+z+1.

Данное значение было записано в регистре 16 и поступило на второй вход умножителя 13 по модулю p3(z)=z4+z3+z2+z+1 при поступлении второго синхросигнала 10. В результате на выходе умножителя 13 по модулю p3(z)=z4+z3+z2+z+1 получается результат который записывается в регистр 16.

При поступлении третьего сигнала по входу 10 с выхода первого блока памяти 12 на первый вход умножителя 13 по модулю p3(z)=z4+z3+z2+z+1 подается значение которое умножается на значение поступившее на второй вход умножителя 13 по модулю p3(z)=z4+z3+z2+z+1. Данное значение было записано в регистре 16 и поступило на второй вход умножителя 13 по модулю p3(z)=z4+z3+z2+z+1 при поступлении третьего синхросигнала 10. В результате на выходе умножителя 13 по модулю p3(z)=z4+z3+z2+z+1 получается результат который записывается в регистр 16.

При поступлении четвертого сигнала по входу 10 с выхода первого блока памяти 12 на первый вход умножителя 13 по модулю p3(z)=z4+z3+z2+z+1 подается значение которое умножается на значение поступившее на второй вход умножителя 13 по модулю p3(z)=z4+z3+z2+z+1. Данное значение было записано в регистре 16 и поступило на второй вход умножителя 13 по модулю p3(z)=z4+z3+z2+z+1 при поступлении четвертого синхросигнала 10. Значение будет соответствовать ситуации, когда произошел отказ основания p5(z)=z4+z+1. В результате на выходе умножителя 13 по модулю p3(z)=z4+z3+z2+z+1 получается результат

Полученное значение с первого выхода регистра 16 подается на вход умножителя 15, на второй вход которого подается значение P3 l234(z)=p1(z)p2(z)p4(z)=z7+z6+z4+1 выхода второго блока памяти 14. Данное значение будет определяться управляющим сигналом

(y1, y2, y3, y4, y5)=(1, 1, 1, 1, 0),

который поступает на входы второго блока памяти 14 с группы управляющих входов 11 блока 5 расчета ортогональных базисов. В результате значение ортогонального базиса будет равно B3 l234(z)=z9+z8+z6+z2.

Осуществив произведение на получаем пересчет ортогональных базисов в новой системе оснований, которые совпадают с представленными ранее.

Проведем дальнейшую деградацию структуры непозиционного процессора ПСКВ. Допустим, что в процессе дальнейшего функционирования отказало четвертое основание p4(z)=z4+z3+1. Тогда диапазон представления входных данных составит P123(z)=z7+z6+z5+z2+z+1.

При этом ортогональные базисы и соответствующие им веса составят

B1 123(z)=z6+z4+z3+z2+1, m1 123(z)=1.

B2 123(z)=z6+z5+z+1; m2 123(z)=z+1.

B3 123(z)=z5+z4+z3+z2+z+1; m3 l23(z)=z2+z+1.

Для перерасчета ортогональных базисов определим значения

P1 123(z)=z6+z4+z3+z2+1; m1 123(z)=1.

P2 123(z)=z5+1; m2 123(z)=z2modz2+z+1=z+1.

P3 123(z)=z3+1;

m3 l23(z}=[(z3+z)(z3+1)]mod(z4+z3+z2+z+1)=z2+z+1.

Осуществив произведение на соответствующее значение получаем пересчет ортогональных базисов в новой системе оснований, которые совпадают с представленными ранее.

Так как произошел отказ четвертого вычислительного канала, определяемого основанием ПСКВ p4(z)=z4+z3+1, а все остальные находятся в работоспособном состоянии то в процессе функционирования вычислительной системы ПСКВ на управляющих входах 9 появится сигнал

(y1, y2, y3, y4, y5)=(1, 1, 1, 0, 0),

который поступает на группу управляющих входов 11 блока 5 расчета ортогональных базисов.

Рассмотрим работу группы блока 5 расчета ортогональных базисов на примере блока 5, функционирующего по модулю p3(z)=z4+z3+z2+z+1. При поступлении первого сигнала по входу 10 с выхода первого блока памяти 12 на первый вход умножителя 13 по модулю p3(z)=z4+z3+z2+z+1 подается значение которое умножается на 1 и записывается в регистр 16.

При поступлении второго сигнала по входу 10 с выхода первого блока памяти 12 на первый вход умножителя 13 по модулю p3(z)=z4+z3+z2+z+1 подается значение которое умножается на значение поступившее на второй вход умножителя 13 по модулю p3(z)=z4+z3+z2+z+1. Данное значение было записано в регистре 16 и поступило на второй вход умножителя 13 по модулю p3(z)=z4+z3+z2+z+1 при поступлении второго синхросигнала 10. В результате на выходе умножителя 13 по модулю p3(z)=z4+z3+z2+z+1 получается результат

который записывается в регистр 16.

При поступлении третьего сигнала по входу 10 с выхода первого блока памяти 12 на первый вход умножителя 13 по модулю p3(z)=z4+z3+z2+z+1 подается значение которое умножается на значение поступившее на второй вход умножителя 13 по модулю p3(z)=z4+z3+z2+z+1. Данное значение было записано в регистре 16 и поступило на второй вход умножителя 13 по модулю p3(z)=z4+z3+z2+z+1 при поступлении третьего синхросигнала 10. В результате на выходе умножителя 13 по модулю p3(z)=z4+z3+z2+z+1 получается результат

который записывается в регистр 16.

При поступлении четвертого сигнала по входу 10 с выхода первого блока памяти 12 на первый вход умножителя 13 по модулю p3(z)=z4+z3+z2+z+1 подается значение , которое умножается на значение поступившее на второй вход умножителя 13 по модулю p3(z)=z+z+z+z+1. Данное значение было записано в регистре 16 и поступило на второй вход умножителя 13 по модулю p3(z)=z4+z3+z2+z+1 при поступлении четвертого синхросигнала 10. Значения и будут соответствовать ситуации, когда произошел отказ оснований p4(z)=z4+z3+1 и p5(z)=z4+z+1. В результате на выходе умножителя 13 по модулю р3(z)=z4+z3+z2+z+1 получается результат

Полученное значение с первого выхода регистра 16 подается на вход умножителя 15, на второй вход которого подается значение P3 l234(z)==p1(z)p2(z)==z+1 с выхода второго блока памяти 14. Данное значение будет определяться управляющим сигналом

(y1, y2, y3, y4, y5)=(1, 1, 1, 0, 0),

который поступает на входы второго блока памяти 14 с группы управляющих входов 11 блока 5 расчета ортогональных базисов. Осуществив произведение на получаем пересчет ортогональных базисов в новой системе оснований. В результате значение ортогонального базиса будет равно B3 123(z)=z5+z4+z3+z2+z+1, которые совпадают с представленными ранее.

Устройство для преобразования из полиномиальной системы классов вычетов в позиционный код, содержащее вход запуска устройства, группу сдвиговых регистров, блок синхронизации, выход устройства, блоки элементов И, группу информационных входов, причем вход запуска устройства соединен с входом запуска блока синхронизации, выход которого соединен с входами разрешения сдвига сдвиговых регистров группы, информационные входы которых являются соответствующими информационными входами группы устройства, выход i-го сдвигового регистра группы соединен с первым входом элемента И i-й группы (i=1, 2, …, n), причем устройство содержит группу блоков расчета ортогональных базисов, сумматор по модулю два, управляющие входы устройства, причем выходы блока синхронизации подключены к первому входу блоков расчета ортогональных базисов, второй вход которых подключен к управляющим входам устройства, выход i-го блока расчета ортогональных базисов подключены ко второму входу элементов И i-го блока, третьи входы которых соединены с соответствующим управляющим входом группы, выходы элементов И соединены со входами сумматора по модулю два, выход которого является выходом устройства, отличающееся тем, что блок расчета ортогональных базисов содержит синхровходы, n управляющих входов, первый и второй блоки памяти, умножитель, умножитель по модулю pi(z), где i=1, 2, …, n, и регистр, причем синхровходы подключены к первому и второму блокам памяти и регистру, n управляющих входов подключены к первому и второму блокам памяти, выход первого блока памяти подключен к первому входу умножителя по модулю pi(z), где i=1, 2, …, n, выход второго блока памяти подключен к умножителю, выход умножителя по модулю pi(z), где i=1, 2, …, n подключен к входу регистра, первый выход регистра подключен к входу умножителя, второй выход регистра подключен к второму входу умножителя по модулю pi(z), где i=1, 2, …, n, выход умножителя является выходом блока.