Способ передачи и приема сигнала и устройство для передачи и приема сигнала

Иллюстрации

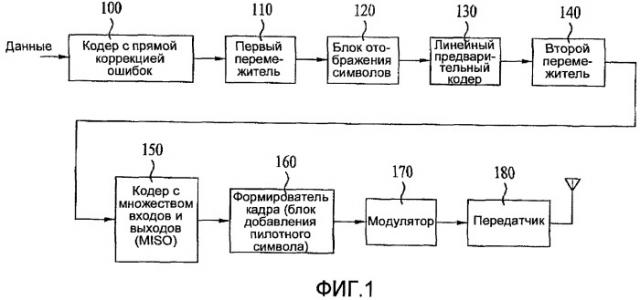

Показать всеИзобретение относится к системам приема/передачи сигнала. Техническим результатом является улучшение эффективности использования полосы пропускания канала, увеличение скорости передачи данных и расстояния передачи сигнала. Указанный технический результат достигается тем, что предложено устройство передачи сигнала, содержащее: кодер с прямой коррекцией ошибок (FEC), который выполняет кодирование FEC входных данных согласно схеме кодирования Боуза-Чоудхури-Хоквенгема (ВСН) и схеме кодирования с малой плотностью проверок на четность (LDPC); первый перемежитель, который перемежает FEC-кодированные данные; блок отображения символов, который преобразовывает перемежаемые данные в символы данных; второй перемежитель, который выполняет перемежение символов данных; кодер, который кодирует символы данных, перемежаемые вторым перемежителем согласно способу кодирования множество входов один выход (MISО); блок вставки пилотного символа, который вставляет по меньшей мере один пилотный символ в кадр данных, включающий в себя кодированные символы данных, причем по меньшей мере пилотный символ включает в себя информацию для типа передачи согласно способу кодирования MISO; и передатчик для передачи кадра данных, включающий в себя пилотный символ и символы данных. 4 н. и 11 з.п. ф-лы, 35 ил.

Реферат

ОБЛАСТЬ ТЕХНИКИ

Настоящее изобретение относится к способу передачи/приема сигнала и к устройству для передачи/приема сигнала, а более конкретно - к способу передачи/приема сигнала и к устройству для передачи/приема сигнала, которые могут увеличивать скорость переноса данных.

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

Когда была разработана технология цифрового широковещания, стало возможно передавать/принимать широковещательный сигнал, включающий в себя видеоизображения высокой четкости (HD) и высококачественный цифровой звук. При непрерывном развитии алгоритмов сжатия и высокой эффективности аппаратных средств система цифрового широковещания быстро развивается. Система цифрового телевидения (DTV) может принимать цифровой широковещательный сигнал и обеспечивать пользователям множество дополнительных услуг, а также видеосигнал и звуковой сигнал.

Когда цифровое вещание стало широко использоваться, увеличился спрос на такие услуги, как более высококачественный видео- и звуковой сигнал, и объем данных или количество каналов телевизионного вещания, которые необходимы пользователями, постепенно увеличивается.

РАСКРЫТИЕ ИЗОБРЕТЕНИЯ

Техническая проблема

Однако при существующем способе передачи/приема сигнала нельзя увеличивать объем передаваемых/принимаемых данных или количество широковещательных каналов. Соответственно существует потребность в новом способе передачи/приема сигнала, который может улучшить эффективность использования полосы пропускания канала и уменьшать стоимость создания сети для передачи/приема сигнала, по сравнению с существующим способом передачи/приема сигнала.

Задачей настоящего изобретения является обеспечение способа передачи/приема сигнала и устройства для передачи/приема сигнала, которые могут увеличить скорость передачи данных и использовать существующую сеть для передачи/приема сигнала.

Дополнительные преимущества, задачи и особенности изобретения будут сформулированы частично в последующем описании, а частично станут очевидными для специалистов после изучения последующего описания, или их можно узнать из практического применения изобретения. Задачи и другие преимущества изобретения можно реализовать и обеспечить с помощью структуры, которая, в частности, указана в данном описании и в формуле изобретения, а также на прилагаемых чертежах.

Техническое решение

Для достижения этих задач и других преимуществ и в соответствии с целью изобретения, которое воплощено и подробно описано в данной работе, обеспечивают устройство для передачи сигнала и устройство для приема сигнала. Устройство для передачи сигнала включает в себя кодер с прямой коррекцией ошибок (FEC), первый перемежитель, блок отображения символов, второй перемежитель, кодер, блок вставки пилотного символа и передатчик.

Кодер с прямой коррекцией ошибок (FEC) выполняет кодирование с прямой коррекцией ошибок (FEC) входных данных согласно схеме кодирования Боуза-Чоудхури-Хоквенгема (BCH) и схеме кодирования с малой плотностью проверок на четность (LDPC). Первый перемежитель перемежает FEC-кодированные данные, блок отображения символов преобразовывает перемежаемые данные в символы данных, и второй перемежитель перемежает символы данных. Кодер кодирует символы данных, перемежаемые вторым перемежителем. Блок вставки пилотного символа вставляет по меньшей мере один пилотный символ в кадр данных, включающий в себя кодированные символы данных, и передатчик передает кадр данных, включающий в себя пилотные символы и символы данных.

Блок вставки пилотного символа вставляет по меньшей мере один пилотный символ в начальную часть кадра данных. Второй перемежитель хранит в памяти преобразованные символы данных по строкам, а считывает хранимые символы данных по столбцам.

Кодер принимает последовательные первый и второй символы и кодирует символы таким образом, что Y_tx1 (t)=S0, Y_tx1 (t+T)=S1, Y_tx2 (t)=-S1* и Y_tx2 (t+T)=S0*, где S0 представляет первый символ, S1 представляет второй символ, * представляет комплексное сопряжение, Y_tx1 представляет кодированные символы для передачи через первую антенну, Y_tx2 представляет кодированные символы для передачи через вторую антенну, t представляет время, когда передают символы, и T представляет период времени между передачей первого символа и второго символа соответственно.

Устройство для приема сигнала включает в себя приемник, анализатор (1330) кадра, декодер, первый деперемежитель, блок обратного отображения символов, второй деперемежитель и декодер с прямой коррекцией ошибок (FEC).

Анализатор кадра анализирует символы данных в принимаемом кадре данных, декодер декодирует проанализированные символы данных. Первый деперемежитель деперемежает декодированные символы данных, блок обратного отображения символов преобразовывает деперемежаемые символы данных в битовые данные и второй деперемежитель деперемежает преобразованные битовые данные. Декодер с прямой коррекцией ошибок (FEC) выполняет декодирование с прямой коррекцией ошибок (FEC) относительно деперемежаемых битовых данных согласно схеме декодирования Боуза-Чоудхури-Хоквенгема (BCH) и схеме декодирования с малой плотностью проверок на четность (LDPC).

По меньшей мере один пилотный символ может быть включен в начальную часть кадра данных. Декодер декодирует проанализированные символы данных согласно алгоритму Аламоути. Первый деперемежитель хранит в памяти декодированные символы данных по строкам, а считывает хранимые символы данных по столбцам.

В другом аспекте обеспечивают способ передачи и приема сигнала. Способ включает в себя выполнение кодирования с прямой коррекцией ошибок (FEC) входных данных согласно схеме кодирования Боуза-Чоудхури-Хоквенгема (BCH) и схеме кодирования с малой плотностью проверок на четность (LDPC), перемежение FEC-кодированных данных, преобразование перемежаемых данных в символы данных, перемежение символов данных, кодирование перемежаемых символов данных, вставку по меньшей мере одного пилотного символа в кадр данных, включающий в себя кодированные символы данных, и передачу кадра данных, включающего в себя пилотные символы и символы данных.

Преобразованные символы данных перемежают таким образом, что преобразованные символы данных хранят в памяти по строкам, а считывают хранимые символы данных по столбцам.

При кодировании перемежаемых символов данных первый и второй символы в перемежаемых символах данных кодируют таким образом, чтобы Y_tx1(t)=S0, Y_tx1 (t+T)=S1, Y_tx2 (t)=-S1*, Y_tx2 (t+T)=S0*, где S0 представляет первый символ, S1 представляет второй символ, * представляет комплексное сопряжение, Y_tx1 представляет кодированные символы для передачи через первую антенну, Y_tx2 представляет кодированные символы для передачи через вторую антенну, t представляет время, когда передают символы, и T представляет период времени между передачей первого символа и второго символа соответственно.

Способ включает в себя прием кадра данных, включающего в себя символы данных и по меньшей мере один пилотный символ, поиск символов данных в принятом кадре данных, декодирование проанализированных символов данных, деперемежение декодированных символов данных, преобразование деперемежаемых символов данных в битовые данные, деперемежение преобразованных битовых данных и выполнение декодирования с прямой коррекцией ошибок (FEC) деперемежаемых битовых данных согласно схеме декодирования Боуза-Чоудхури-Хоквенгема (BCH) и схеме декодирования с малой плотностью проверок на четность (LDPC).

Проанализированные символы данных декодируют согласно алгоритму Аламоути. Декодированные символы данных перемежают таким образом, что декодированные символы данных хранят в памяти по строкам, а считывают хранимые символы данных по столбцам.

Дополнительные преимущества, задачи и особенности изобретения будут сформулированы частично в последующем описании, а частично станут очевидны специалистам после изучения последующего описания, или их можно изучать из практического применения изобретения. Задачи и другие преимущества изобретения можно реализовывать и обеспечивать с помощью структуры, которая, в частности, указана в данном описании и в формуле изобретения, а также на прилагаемых чертежах.

Полезные результаты

Согласно способу передачи/приема сигнала и устройству для передачи/приема сигнала настоящего изобретения можно упростить переключение системы передачи/приема сигнала, используя существующую сеть передачи/приема сигнала, и уменьшать стоимость.

Кроме того, можно улучшить скорость переноса данных, так как можно получить выигрыш в ОСШ (отношение сигнал-шум), и оценивать канал по отношению к каналу передачи, имеющему свойство большого разброса задержки, для увеличения расстояния передачи сигнала. Соответственно можно улучшать эффективность передачи/приема сигнала в системе передачи/приема.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Фиг. 1 является схематической структурной схемой, на которой показано устройство для передачи сигнала согласно варианту осуществления настоящего изобретения;

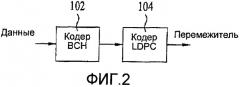

фиг. 2 является схематической структурной схемой, на которой показан кодер с прямой коррекцией ошибок согласно варианту осуществления настоящего изобретения;

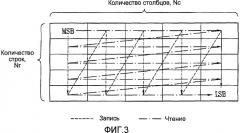

фиг. 3 является представлением, на котором показан перемежитель для перемежения входных данных согласно варианту осуществления настоящего изобретения;

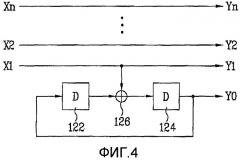

фиг. 4 является схематической структурной схемой, на которой показан модулятор решетчатого кодирования согласно варианту осуществления настоящего изобретения;

фиг. 5 является схематической структурной схемой, на которой показан линейный предварительный кодер согласно варианту осуществления настоящего изобретения;

фиг. 6-8 являются представлениями, на которых показана кодовая матрица для распределения входных данных согласно варианту осуществления настоящего изобретения;

фиг. 9 является представлением, на котором показана структура переносимого кадра согласно варианту осуществления настоящего изобретения;

фиг. 10 является структурной схемой, на которой показано устройство передачи сигнала, имеющее множество передающих трактов, согласно другому варианту осуществления настоящего изобретения;

фиг. 11-15 являются представлениями, на которых показаны примеры кодовых матриц 2x2 для распределения входных символов согласно варианту осуществления настоящего изобретения;

фиг. 16 является представлением, на котором показан пример способа перемежения согласно варианту осуществления настоящего изобретения;

фиг. 17 является представлением, на котором подробно показан пример способа перемежения, показанный на фиг. 16, согласно варианту осуществления настоящего изобретения;

фиг. 18 является представлением, на котором показан пример способа кодирования с множеством входов и выходов согласно варианту осуществления настоящего изобретения;

фиг. 19 является представлением, на котором показана структура интервала пилотного символа согласно варианту осуществления настоящего изобретения;

фиг. 20 является представлением, на котором показана другая структура интервала пилотного символа согласно варианту осуществления настоящего изобретения;

фиг. 21 является схематической структурной схемой, на которой показано устройство для приема сигнала согласно варианту осуществления настоящего изобретения;

фиг. 22 является схематической структурной схемой, на которой показан пример декодера линейного предварительного кодирования согласно варианту осуществления настоящего изобретения;

фиг. 23 является схематической структурной схемой, на которой показан другой пример декодера линейного предварительного кодирования согласно варианту осуществления настоящего изобретения;

фиг. 24-26 являются представлениями, на которых показаны примеры кодовых матриц 2х2 для восстановления распределенных символов согласно варианту осуществления настоящего изобретения;

фиг. 27 является схематической структурной схемой, на которой показан декодер решетчатого кодирования согласно варианту осуществления настоящего изобретения;

фиг. 28 является схематической структурной схемой, на которой показан декодер с прямой коррекцией ошибок согласно варианту осуществления настоящего изобретения;

фиг. 29 является структурной схемой, на которой показан пример устройства приема сигнала, имеющего множество приемных трактов согласно варианту осуществления настоящего изобретения;

фиг. 30 является представлением, на котором показан пример способа декодирования с множеством входов и выходов согласно варианту осуществления настоящего изобретения;

фиг. 31 является представлением, на котором подробно показан пример на фиг. 30 согласно варианту осуществления настоящего изобретения;

фиг. 32 является схематической структурной схемой, на которой показан другой пример устройства для передачи сигнала согласно варианту осуществления настоящего изобретения;

фиг. 33 является схематической структурной схемой, на которой показан другой пример устройства для приема сигнала согласно варианту осуществления настоящего изобретения;

фиг. 34 является последовательностью операций, показывающей способ передачи сигнала согласно варианту осуществления настоящего изобретения; и

фиг. 35 является последовательностью операций, показывающей способ приема сигнала согласно варианту осуществления настоящего изобретения.

ПРЕДПОЧТИТЕЛЬНЫЙ ВАРИАНТ ОСУЩЕСТВЛЕНИЯ ИЗОБРЕТЕНИЯ

Способ передачи/приема сигнала и устройство для передачи/приема сигнала согласно настоящему изобретению будут подробно описаны в отношении сопроводительных чертежей.

Фиг. 1 - схематическая структурная схема, на которой показано устройство для передачи сигнала согласно варианту осуществления настоящего изобретения.

Устройство для передачи сигнала на фиг. 1 может быть системой передачи широковещательного сигнала, предназначенной для передачи широковещательного сигнала, включающего в себя видеоданные и т.д. На фиг. 1, например, теперь будет описана система передачи сигнала согласно системе передачи цифрового видеосигнала (DVB). В варианте осуществления на фиг. 1 будет описана система передачи сигнала, концентрируясь на операции обработки сигнала.

Вариант осуществления на фиг. 1 включает в себя кодер 100 с прямой коррекцией ошибок (FEC), первый перемежитель 110, блок 120 отображения символов, линейный предварительный кодер 130, второй перемежитель 140, кодер 150 с множеством входов и выходов, формирователь 160 кадра, модулятор 170 и передатчик 180.

Кодер 100 FEC кодирует входной сигнал и выводит кодированный сигнал. Кодер 100 FEC предоставляет возможность системе приема сигнала обнаружить ошибку, которая возникает в передаваемых данных, и корректировать эту ошибку. Данные, кодированные кодером 100 FEC, вводят в первый перемежитель 110. Подробный пример кодера 100 FEC показан на фиг. 2.

Первый перемежитель 110 перемешивает данные, выводимые из кодера 100 FEC, по случайным позициям, так, чтобы они стали устойчивы к пачке ошибок, которые возникают в данных при передаче данных. Первый перемежитель 110 может использовать сверточный перемежитель или блочный перемежитель, который можно изменить в соответствии с передающей системой. Вариант осуществления первого перемежителя 110 подробно показан на фиг. 3.

Данные, перемежаемые первым перемежителем 110, вводят в блок 120 отображения символов. Блок 120 отображения символов может быть модулятором решетчатого кодирования, в дальнейшем, когда блок 120 отображения символов отображает данные в символ в соответствии с решетчатым кодированием. Модулятор 120 решетчатого кодирования преобразовывает входные данные в кодированные данные символа. Модулятор 120 решетчатого кодирования может кодировать передаваемый сигнал, и он может быть блоком отображения символов, отображающим кодированный сигнал в символ в соответствии со схемой, такой как схема QAM (квадратурной амплитудной модуляции) или схема QPSK (квадратурной фазовой манипуляции). Подробный пример модулятора 120 решетчатого кодирования показан на фиг. 4.

Линейный предварительный кодер 130 распределяет входные данные символа по нескольким частям выходных данных символа для уменьшения вероятности того, что вся информация будет потеряна из-за замираний, когда она подвергается частотно-избирательным замираниям в канале. Подробный пример линейного предварительного кодера 130 показан на фиг. 5-8.

Второй перемежитель 140 перемежает данные символа, выводимые из линейного предварительного кодера 130. Таким образом, если перемежение выполняют с помощью второго перемежителя 140, то можно исправить ошибку, которая возникает, когда данные символа подвергают одинаковому частотно-избирательному замиранию в определенной позиции. Второй перемежитель 140 может использовать сверточный перемежитель или блочный перемежитель. Вариант осуществления второго перемежителя 110 также подробно показан на фиг. 3.

Линейный предварительный кодер 130 и второй перемежитель 140 обрабатывает данные для передачи так, чтобы они стали устойчивы к частотно-избирательным замираниям в канале, и их можно называть кодером для частотно-избирательных замираний.

Кодер 150 с множеством входов и выходов кодирует данные, перемежаемые вторым перемежителем 140, так что данные обрабатывают через множество передающих трактов. Устройство для передачи/приема сигнала может обрабатывать сигнал согласно способу с множеством входов и выходов. В дальнейшем способ с множеством входов и выходов включает в себя способ с множеством входов и множеством выходов (MIMO), способ с одним входом и множеством выходов (SIMO) и способ с множеством входов и одним выходом (MISO).

В качестве способа кодирования с множеством входов и выходов можно использовать способ пространственного мультиплексирования и способ пространственного разнесения. При способе пространственного мультиплексирования данные, содержащие отличающуюся информацию, передают одновременно, используя множество передающих и приемных антенн. Соответственно данные можно более быстро передавать без дополнительного увеличения полосы пропускания системы. При способе пространственного разнесения данные, имеющие ту же самую информацию, передают через множество передающих антенн, так что может быть получен эффект разнесения.

В это время в качестве кодера 150 с множеством входов и выходов, который использует способ пространственного разнесения, может использоваться пространственно-временной блочный кодер (STBC), пространственно-частотный блочный кодер (SFBC) или пространственно-временной решетчатый кодер (STTC). В качестве кодера 150 с множеством входов и выходов, который использует способ пространственного мультиплексирования, способ деления потока данных на множество передающих антенн и передачи потоков данных, можно использовать полноскоростной кодер с полным разнесением (FDFR), линейный дисперсный кодер (LDC), вертикальный многоуровневый пространственно-временной кодер лаборатории Бэлла (VBLAST) или диагональный BLAST (D-BLAST).

Формирователь 160 кадра вставляет предварительно кодированный сигнал в пилот-сигнал в предопределенную позицию кадра и формирует кадр, определенный в системе передачи/приема. Формирователь 160 кадра может размещать интервал символа данных и интервал пилотного символа, который является преамбулой интервала символа данных, в кадре. Соответственно в дальнейшем формирователь 160 кадра можно называть блоком вставки пилотного символа.

Например, формирователь 160 кадра может размещать пилотные несущие, позиции которых во времени сдвинуты и распределены, в интервале данных несущей. Формирователь кадра может размещать повторные пилотные несущие, позиции которых во времени зафиксированы, в интервале данных.

Модулятор 170 модулирует данные с помощью способа мультиплексирования с ортогональным частотным разделением (OFDM), так что генерируют символы OFDM. И модулятор 170 вставляет защитный интервал в модулируемые данные.

Передатчик 180 преобразовывает цифровой сигнал, имеющий защитный интервал и интервал данных, который выводят из модулятора 170, в аналоговый сигнал, и передает аналоговый сигнал.

Фиг. 2 является схематической структурной схемой, на которой показан кодер FEC, показанный на фиг. 1. Кодер FEC включает в себя кодер 102 Боуза-Чоудхури-Хоквенгема (BCH) и кодер 104 с малой плотностью проверок на четность (LDPC) в качестве внешнего кодера и внутреннего кодера соответственно.

Код LDPC является кодом коррекции ошибок, который может уменьшать вероятность того, что информация будет потеряна. Кодер 104 LDPC кодирует сигнал в состоянии, в котором длина блока кодирования является такой большой, что передаваемые данные устойчивы к ошибкам передачи. Чтобы препятствовать увеличению аппаратной сложности из-за увеличения размера блока, плотность битов четности уменьшают для уменьшения сложности кодера.

Чтобы препятствовать возникновению области насыщения вероятности ошибки в выходных данных приемника, кодер 102 BCH присоединяют перед кодером 104 LDPC в качестве дополнительного внешнего кодера. Если пренебрежимо малая область насыщения вероятности ошибки возникает, даже когда используется только кодер 104 LDPC, то кодер 102 BCH можно не использовать. Альтернативно в качестве внешнего кодера вместо кодера BCH можно использовать другие кодеры.

В случае, когда используют два кодера с коррекцией ошибок, контрольные разряды четности (контрольные разряды четности BCH) для кодирования BCH добавляют к входному кадру данных, и контрольные разряды четности (контрольные разряды четности LDPC) для кодирования LDPC добавляют к контрольным битам четности BCH. Длина контрольных битов четности BCH, добавляемых к кодируемому кадру данных, может изменяться от длины ключевого слова LDPC и скорости кодирования LDPC.

Данные, которые FEC-кодируют с помощью кодера 102 BCH и кодера 104 LDPC, выводят к первому перемежителю 110.

Фиг. 3 является представлением, на котором показан первый (второй) перемежитель, показанный на фиг. 1. В качестве первого (второго) перемежителя на фиг. 3, например, можно использовать блочный перемежитель.

Перемежитель на фиг. 3 хранит входные данные в области памяти, имеющей форму матрицы, в предопределенной структуре, и считывает, и выводит данные в структуре, отличающейся от структуры, используемой для хранения данных. Например, перемежитель на фиг. 3 имеет объем памяти NrxNc, состоящий из Nr строк и Nc столбцов, и данные, вводимые в перемежитель, заполняют от позиции, соответствующей первой строке и первому столбцу объема памяти. Данные хранят с первой строки и первого столбца до Nr-ой строки и первому столбцу, а если первый столбец заполнен, тогда хранят от первой строки до Nr-й строки следующего столбца (второго столбца). Данные можно хранить до Nr-й строки Nc-го столбца в этой последовательности (т.е. данные хранят по столбцам).

В случае, когда данные, которые хранят, как показано на фиг. 3, считывают, данные считывают и выводят от первой строки и первого столбца к первой строке и Nc-му столбцу. Если все данные первой строки считаны, то данные считывают и выводят с первого столбца следующей строки (второй строки) в направлении Nc-го столбца. Данные можно считывать и выводить до Nc-го столбца Nr-й строки в этой последовательности (т.е. данные считывают построчно). В это время позиция старшего значащего бита (MSB) блока данных является левым самым верхним краем, а позиция младшего значащего бита (LSB) блока данных является правым самым нижним краем.

Размер блока памяти, шаблон хранения и шаблон считывания перемежителя являются только примерами, и их можно изменять согласно реализуемым вариантам осуществления. Например, размер блока памяти первого перемежителя может изменяться в соответствии с размером блока FEC-кодирования. В примере на фиг. 2 количество строк Nr и столбцов Nc блока, которые определяют размер блока, перемежаемого первым перемежителем, могут изменяться согласно длине блока кода LDPC. Если длина блока кода LDPC увеличивается, то длину блока (т.е. длину строки блока) можно увеличить.

Фиг. 4 является схематической структурной схемой, на которой показан модулятор решетчатого кодирования. Решетчатое кодирование является способом отображения символов, в котором можно максимизировать минимальное Евклидово расстояние между символами. Модулятор 120 решетчатого кодирования включает в себя элемент задержки и блок поразрядной операции. На фиг. 4, для удобства описания, например, используют два элемента задержки (первый элемент задержки 122 и второй элемент задержки 124) и поразрядный сумматор 126. Таким образом, количество элементов задержки и блоков выполнения поразрядной операции может изменяться согласно количеству состояний или количеству входных битов, которые будут кодировать с помощью решетчатого кодирования. Модулятор 120 решетчатого кодирования принимает входные биты X1-Xn и выводит n (Y1-Yn) MSB (старших значащих битов) через маршрут обычного кодирования. Модулятор решетчатого кодирования принимает входной LSB (младший значащий бит) X1 и выводит выходной бит Y1 и дополнительный бит Y0, которые кодированы с помощью решетчатого кодирования.

Поразрядный сумматор 126 поразрядно складывает входное значение X1 и выходное значение от первого элемента задержки 122 и выводит суммированное значение. Второй элемент задержки 124 задерживает значение, выводимое от поразрядного сумматора 126, и выводит Y0. Значение, выводимое от второго элемента задержки 124, возвращают к первому элементу задержки 122.

Среди выходных битов Y0-Yn, Y1 и Y0 используются для выбора сомножества, которое является подмножеством решетчатой кодированной модуляции кодирующей совокупности, а остальные биты Y2-Yn используют для определения совокупности в сомножестве.

Модулятор 120 решетчатого кодирования может уменьшать битовые ошибки из-за выбора сомножества, когда увеличивают количество состояний или увеличивают количество входных битов, которые будут кодировать с помощью решетчатого кодирования.

Линейный предварительный кодер 130 распределяет входные данные символа по нескольким частям выходных данных символа для уменьшения вероятности того, что вся информация будет потеряна из-за замираний, когда она подвергается частотно-избирательным замираниям в канале.

Фиг. 5 является схематической структурной схемой, на которой показан линейный предварительный кодер, показанный на фиг. 1. Линейный предварительный кодер 130 может включать в себя последовательно-параллельный преобразователь 132, кодер 134 и параллельно-последовательный преобразователь 136.

Последовательно-параллельный преобразователь 132 преобразовывает входные данные в параллельные данные. Кодер 134 распределяет значения преобразованных параллельных данных по нескольким частям данных через оперирование кодирующей матрицы.

Кодирующую матрицу разрабатывают с помощью сравнения передаваемого символа с принимаемым символом так, чтобы минимизировать попарную ошибочную вероятность (PEP), что эти два символа отличаются друг от друга. Если кодирующую матрицу разрабатывают таким образом, чтобы минимизировать PEP, то выигрыш разнесения и выигрыш кодирования, полученные через линейное предварительное кодирование, становятся максимальными.

Если минимальное Евклидово расстояние линейно предварительно кодированного символа делают максимальным через кодирующую матрицу, то вероятность ошибки можно минимизировать, когда приемник использует декодер по методу максимального правдоподобия (ML).

Фиг. 6 является представлением, на котором показан пример кодирующей матрицы, используемой кодером 134, т.е. кодовой матрицы для распределения входных данных. Фиг. 6 показывает пример кодирующей матрицы для распределения входных данных по нескольким частям выходных данных, которую также называют матрицей Вандермонда.

Входные данные можно упорядочивать параллельно по длине числа (L) выходных данных.

матрицы можно выражать следующим уравнением и можно определять другими способами. Если матрица Вандермонда используется в качестве кодирующей матрицы, то элемент матрицы определяют в соответствии с математической формулой 1.

Кодирующая матрица математической формулы 1 вращает фазу входных данных с помощью математической формулы на фиг. 1 в соответствии с входными данными, и генерирует выходные данные.

Математическая формула 1

В математической формуле 1 L обозначает количество выходных данных. Если группой входных данных, которые вводят на кодер на фиг. 5, является x, а группой данных, которую кодируют и выводят с помощью кодера 134 с использованием матрицы по математической формуле 1, являются y, то y выражают в соответствии с математической формулой 2.

Математическая формула 2

Фиг. 7 показывает другой пример кодирующей матрицы. Фиг. 7 показывает другой пример кодирующей матрицы для распределения входных данных по нескольким частям выходных данных, которую также называют матрицей Адамара. Матрица на фиг. 7 является матрицей, имеющей обычную форму, в которой L расширяют на 2k. В данном случае L обозначает количество выходных символов, по которым будут распределять входные символы.

Выходные символы матрицы на фиг. 7 можно получать с помощью суммирования и вычитания L выходных символов. Другими словами, входные символы можно распределять по L выходным символам соответственно.

Даже в матрице на фиг. 7, если входной группой данных, вводимой на кодер 134 на фиг. 5, является x, а группой данных, которую кодируют и выводят с помощью кодера 134 с использованием описанной выше матрицы, является y, то y является произведением описанной выше матрицы и x.

Фиг. 8 показывает другой пример кодирующей матрицы для распределения входных данных. Фиг. 8 показывает другой пример кодирующей матрицы для распределения входных данных по нескольким частям выходных данных, которую также называют матрицей Золотого кода. Матрица Золотого кода является матрицей 4x4, имеющей специальную форму. Альтернативно можно использовать две различные матрицы 2x2.

C на фиг. 8 обозначает кодовую матрицу Золотого кода, и x1, x2, x3 и x4 в кодовой матрице обозначают данные символа, которые можно параллельно вводить на кодер 134 на фиг. 5. Константы в кодовой матрице могут определять характеристики кодовой матрицы, а значения строк и столбцов, вычисленные с помощью данных констант кодовой матрицы и входных данных символа, могут быть выражены с помощью выходных данных символа. Последовательность выходных данных символа может изменяться согласно вариантам осуществления реализации. Соответственно в этом случае параллельно-последовательный преобразователь 136 на фиг. 5 может преобразовывать параллельные данные в последовательные данные согласно последовательности позиций данных в параллельном наборе данных, выводимом из кодера 134, и выводить последовательные данные.

Фиг. 9 является представлением, на котором показана структура переносимого кадра, кодированного с помощью канала передачи данных описанного выше варианта осуществления. Переносимый кадр, сформированный согласно настоящему варианту осуществления, может включать в себя пилотный символ, включающий в себя информацию пилотной несущей, и символ данных, включающий в себя информацию данных.

В примере на фиг. 9 кадр включает в себя М (М является натуральным числом) интервалов, и разделен на M-1 интервалов символа данных и интервал пилотного символа, который используют в качестве преамбулы. Кадры, имеющие описанную выше структуру, повторяют.

Каждый интервал символа включает в себя информацию несущей через некоторое число поднесущих OFDM. Информация пилотной несущей интервала пилотного символа состоит из случайных данных для уменьшения отношения пиковой к средней мощности (PAPR). Значение автокорреляции информации пилотной несущей имеет форму импульса в частотной области. Значение корреляции между символами несущих файла может быть близко к 0.

Соответственно интервал пилотного символа, используемый в качестве преамбулы, предоставляет возможность приемнику быстро распознавать кадр сигнала на фиг. 9, и он может использоваться для корректировки и синхронизации при уходе частоты. Так как интервал пилотного символа представляет начало кадра сигнала, можно устанавливать параметр системы передачи для предоставления возможности быстро синхронизировать принимаемый сигнал. Формирователь кадра формирует интервалы символа данных и вставляет интервал пилотного символа перед интервалами символов данных, таким образом формируя передаваемый кадр.

Если отдельный интервал, включающий в себя информацию пилотной несущей, присутствует в переносимом кадре, как показано на фиг. 9, то интервалы символа данных могут не включать в себя информацию пилотной несущей. Соответственно можно увеличивать информационную емкость. В DVB, например, так как процент пилотной несущей во всех допустимых несущих составляет приблизительно 10%, величину увеличения информационной емкости выражают в соответствии с математической формулой 3.

Математическая формула 3

В математической формуле 3 Δ обозначает величину увеличения, а М обозначает количество интервалов, которые включает в себя кадр.

Фиг. 10 является структурной схемой, на которой показано устройство передачи сигнала, которое обрабатывает сигналы, используя множество передающих трактов, согласно другому варианту осуществления настоящего изобретения. В дальнейшем, для удобства описания предполагают, что количество передающих трактов равно двум.

Вариант осуществления на фиг. 10 включает в себя кодер 800 с прямой коррекцией ошибок (FEC), первый перемежитель 810, блок 820 отображения символов (модулятор решетчатого кодирования), линейный предварительный кодер 830, второй перемежитель 840, кодер 850 с множеством входов и выходов, первый формирователь 860 кадра, второй формирователь 865 кадра, первый модулятор 870, второй модулятор 875, первый передатчик 880 и второй передатчик 885.

Кодер 800 FEC, первый перемежитель 810, линейный предварительный кодер 830, второй перемежитель 840 и кодер 850 с множеством входов и выходов выполняют те же самые функции, как блоки на фиг. 1.

Кодер 800 FEC включает в себя кодер BCH и кодер LDPC. Кодер 800 FEC выполняет FEC-кодирование входных данных и выводит кодированные данные. Выходные данные перемежают первым перемежителем 810 таким образом, что последовательность потока данных изменяется. В качестве первого перемежителя 810 можно использовать сверточный перемежитель или блочный перемежитель.

Модулятор 820 решетчатого кодирования может преобразовывать входные данные в кодированные данные символа. Таким образом, модулятор 820 решетчатого кодирования может кодировать передаваемый сигнал и отображать кодированный сигнал на символ согласно схеме QAM или QPSK. Например, если сигнал отображают на символ для генерации 128QAM, то символ может включать в себя 7-битовые данные, а если сигнал отображают на символ для генерации 256QAM, то символ может включать в себя 8-битовые данные.

Линейный предварительный кодер 830 включает в себя последовательно-параллельный преобразователь, кодер и параллельно-последовательный преобразователь. Кодовая матрица, с кодированным линейным предварительным кодером 830, показана на фиг. 11-15.

Второй перемежитель 840 перемежает данные символа, выводимые из линейного предварительного кодера 830. В качестве второго перемежителя 840 можно использовать сверточный перемежитель или блочный перемежитель. Второй перемежитель 840 перемежает данные символа таким образом, что данные символа, которые распределяют по данным, выводимым из линейного предварительного кодера 830, не подвергаются тому же самому частотно-избирательному замиранию. Способ перемежения можно менять согласно вариантам осуществления реализации. Пример способа перемежения показан на фиг. 16-17.

Перемежаемые данные выводят на кодер 850 с множеством входов и выходов, и кодер 850 с множеством входов и выходов кодирует входные дан