Устройство диверсифицированного безопасного управления, в частности, для железнодорожной системы

Иллюстрации

Показать всеИзобретение относится к устройствам управления железнодорожной системой. Устройство содержит комплект установленных параллельно процессоров формирования команд управления железнодорожной системой, каждый из которых выполнен с возможностью приема разных наборов команд, блок выбора команды, выбираемой среди выходных данных, поступающих из процессоров. Модульные прикладные автоматические системы идентичны для всех наборов команд, и каждый набор команд, связанный с процессором, выполнен с возможностью формирования отдельного планировщика последовательной активации модульных прикладных автоматических систем согласно отдельной последовательности. Способ содержит следующие этапы: в два процессора загружают два разных набора команд из соответствующих программных баз данных, на соответствующие входы параллельных процессоров передают идентичные входные данные. При помощи каждого процессора исполняют соответствующий ему разный набор команд, позволяющий вычислять и выдавать на соответствующие выходы идентичные выходные данные в зависимости от идентичных входных данных. При этом исполнение набора команд процессором содержит следующие этапы: исполняют, по меньшей мере, две модульные прикладные автоматические системы, извлекают выходные данные, полученные в конце исполнения последовательности, выходные данные направляют в блок выбора команды и командный сигнал выбирают из выходных данных, поступивших из процессоров, в зависимости от определенного критерия. Достигается повышение безопасности железнодорожной системы. 2 н. и 10 з.п. ф-лы, 6 ил.

Реферат

Объектом настоящего изобретения является устройство диверсифицированного безопасного управления, в частности, для железнодорожной системы, содержащее

- комплект из, по меньшей мере, двух процессоров формирования команд, предназначенных для железнодорожной системы, установленных параллельно с возможностью приема на соответствующем входе идентичных входных данных Е,

при этом каждый процессор выполнен с возможностью приема разных наборов команд, позволяющих производить вычисления и выдавать на соответствующие выходы идентичные выходные данные S(P1), S(P2), S(P3) в соответствии с идентичными входными данными Е,

- блок выбора команды, содержащий, по меньшей мере, два входа, при этом каждый вход соединен с выходом процессора, и командный выход, выполненный с возможностью выдачи командного сигнала, выбранного среди выходных данных, полученных от процессора, в зависимости от заранее определенного критерия.

Железнодорожная система содержит систему стрелочного перевода, соединенную с системой одноуровневого железнодорожного переезда, и устройство оповещения о перекрывании шлагбаума на переезде.

Для повышения безопасности известные технические решения предусматривают диверсификацию цепи управления железнодорожной системы в виде ветвей обработки, имеющих разную конфигурацию вычислительных схем. На основании одних и тех же входных данных каждая ветвь исполняет одни и те же прикладные программы или прикладные алгоритмы, но в разных режимах вычисления.

В случае если каждая ветвь работает правильно, на выходе каждой ветви получают одинаковые команды.

В случае сбоя в схемах одной из ветвей формируются разные команды.

В случае одновременного сбоя в нескольких ветвях подаются также разные команды по причине отсутствия корреляции неисправностей между ветвями, имеющими разную конфигурацию вычислительных схем. Такое классическое устройство является предпочтительным, когда применяются сложные алгоритмы.

Простое в плане конструкции и хорошо известное использование этого устройства безопасного управления предполагает наличие процессора идентичной архитектуры для каждой ветви.

В этом хорошо известном варианте использования каждый процессор исполняет отдельный набор команд или целевую программу на основании отдельной исходной программы в зависимости от соответствующего отдельного входного языка компилятора, при этом каждая отдельная исходная программа эмулирует одну и ту же прикладную программу, определенную теми же входами, теми же выходами и теми же прикладными алгоритмами.

Вместе с тем, это использование, являющееся простым в плане оборудования, остается сложным в плане программного обеспечения, которое требует многочисленных расширений программных компонентов в соответствии с числом разных используемых языков или компиляторов.

Объективной проблемой такого классического устройства диверсифицированного безопасного управления является сложность развертывания программных компонентов, использующих несколько компиляционных языков.

Таким образом, задачей настоящего изобретения является создание устройства диверсифицированного безопасного управления, для которого развертывание программных компонентов требует меньших усилий.

В этой связи, объектом настоящего изобретения является устройство диверсифицированного безопасного управления, в частности, для железнодорожной системы, содержащее

- комплект из, по меньшей мере, двух процессоров формирования команд, предназначенных для управления железнодорожной системой, установленных параллельно с возможностью приема на соответствующем входе идентичных входных данных Е,

при этом каждый процессор выполнен с возможностью приема разных наборов команд, позволяющих производить вычисления и выдавать на соответствующие выходы идентичные выходные данные S(P1), S(P2), S(P3) в соответствии с идентичными входными данными Е,

- блок выбора команды, содержащий, по меньшей мере, два входа, при этом каждый вход соединен с выходом процессора, и командный выход, выполненный с возможностью выдачи командного сигнала, выбранного среди выходных данных, полученных от процессора, в зависимости от заранее определенного критерия,

отличающееся тем, что

- каждый набор команд, связанный с процессором, обеспечивает исполнение, по меньшей мере, двух модульных прикладных автоматических систем, при этом модульные прикладные автоматические системы являются идентичными для всех наборов команд,

- каждый набор команд, связанный с процессором, может формировать планировщик последовательной активации, по меньшей мере, двух модульных прикладных автоматических систем согласно соответствующей последовательности,

- и тем, что каждый планировщик отличается от других планировщиков присущей ему соответствующей последовательностью.

Согласно частным вариантам выполнения, устройство диверсифицированного безопасного управления характеризуется одним или несколькими следующими отличительными признаками:

- каждый планировщик может активировать и упорядочивать модульные прикладные автоматические системы согласно отдельной циклической последовательности исполнения модульных прикладных автоматических систем, имеющей идентичный цикл и разные начало цикла или направление прохождения;

- каждый планировщик может активировать и упорядочивать модульные прикладные автоматические системы согласно отдельной циклической последовательности исполнения модульных прикладных автоматических систем, имеющей идентичный цикл с одинаковым направлением прохождения;

- каждый планировщик может активировать и упорядочивать модульные прикладные автоматические системы согласно отдельной последовательности, образованной рядом частичных последовательностей модульных прикладных автоматических систем, сгруппированных в подгруппы, входящие в совокупность модульных прикладных автоматических систем устройства управления;

- подгруппы автоматических систем одинаковы для всех процессоров;

- каждая модульная прикладная автоматическая система содержит входы автоматической системы и выходы автоматической системы,

при этом вход автоматической системы является внешним, если он может принимать входную переменную данную устройства управления,

при этом выход автоматической системы является внешним, если он может выдавать выходную переменную данную устройства управления,

при этом вход и выход одной и той же автоматической системы или двух разных автоматических систем являются внутренними, если они могут быть соединены друг с другом и производить между собой обмен одной и той же переменной данной,

при этом совокупность входных и выходных переменных данных автоматических систем образует вектор состояния устройства управления,

и устройство управления для каждого процессора содержит оперативное запоминающее устройство, содержащее

- регистр состояния начала исполнения последовательности автоматических систем, содержащий значения совокупности переменных состояния перед исполнением последовательности автоматических систем,

- регистр состояния конца исполнения последовательности автоматических систем, содержащий значения совокупности переменных состояния вектора состояния, полученного после исполнения последовательности автоматических систем;

- для каждого процессора и в течение исполнения последовательности процессор может считывать только в регистре состояния начала и записывать только в регистре состояния конца;

- для каждого процессора регистр состояния начала последовательности может быть записан и обновлен только в конце исполнения последовательности при помощи значений переменных состояния, содержащихся в регистре конца последовательности,

и каждый процессор может повторять исполнение последовательности автоматических систем до момента, когда значения состояния, по меньшей мере, двух соответствующих регистров состояния станут одинаковыми;

- каждый процессор содержит

программную базу данных, содержащую набор процессорных команд, выполненный с возможностью загрузки в процессор и исполнения последовательности прикладных автоматических систем согласно последовательности, заданной процессору соответствующим планировщиком;

- каждая программная база данных содержит набор команд, сформированных одним и тем же компилятором;

- блок выбора команды является блоком решения мажоритарной выборки среди выходных данных, поступающих от всех процессоров, при этом блок выполнен с возможностью сравнения выходных данных, поступающих от соответствующих выходов каждого процессора, и передачи выходных данных, мажоритарно общих относительно всех процессоров согласно заранее определенному критерию большинства; и

- блок выбора команды является блоком решения единогласной выборки.

Объектом настоящего изобретения является также способ диверсифицированного безопасного управления, содержащий следующие этапы:

- по меньшей мере, в два процессора загружают два разных набора команд из соответствующих программных баз данных,

- на соответствующие входы параллельных процессоров передают идентичные входные данные,

- при помощи каждого процессора исполняют соответствующий ему разный набор команд, позволяющий вычислять и выдавать на соответствующие выходы идентичные выходные данные в зависимости от идентичных входных данных Е, при этом исполнение набора команд процессором содержит следующие этапы:

- исполняют, по меньшей мере, две модульные прикладные автоматические системы, при этом модульные прикладные автоматические системы являются идентичными для каждого набора команд, согласно соответствующей последовательности, отличной от последовательностей других наборов команд,

- извлекают выходные данные, полученные в конце исполнения последовательности,

- выходные данные направляют в блок выбора команды и

- командный сигнал выбирают из выходных данных, поступивших из процессоров, в зависимости от определенного критерия.

Согласно частным вариантам осуществления способ безопасного управления характеризуется одним или несколькими следующими отличительными признаками:

- в зависимости от критерия выбора подтверждают или соответственно запрещают передачу команды, полученную из множества полученных выходных данных, и

- в случае запрещения сигнализируют наличие сбоя в работе, по меньшей мере, одного процессора.

Настоящее изобретение будет более очевидно из нижеследующего описания, представленного исключительно в качестве примера, со ссылками на прилагаемые чертежи.

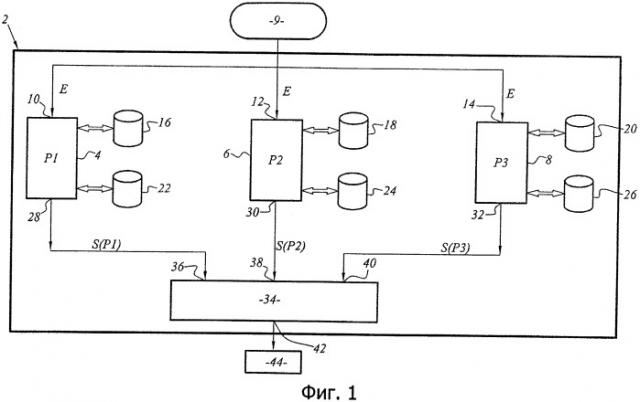

Фиг.1 - блок-схема устройства диверсифицированного безопасного управления.

Фиг.2А, 2В, 2С - блок-схема первого варианта выполнения программных баз данных, показанных на фиг.1.

Фиг.3А, 3В, 3С - последовательности, соответствующие каждой из программных баз данных, показанных соответственно на фиг.2А, 2В, 2С.

Фиг.4А - схема выходов и входов, соответствующих каждой из автоматических систем, показанных на фиг.2А, 2В, 2С.

Фиг.4В и 4С - схематичный вид структуры данных векторов состояния, соответствующих регистру состояния начала последовательности и регистру состояния конца последовательности любого оперативного ЗУ.

Фиг.5 - блок-схема способа управления, осуществляемого устройством диверсифицированного безопасного управления согласно первому варианту выполнения программных баз данных.

Фиг.6А, 6В, 6С, 6D, 6Е - последовательность второго варианта выполнения программных баз данных.

Устройство 2 диверсифицированного безопасного управления, показанное на фиг.1, содержит три цепи вычисления или обработки, при этом каждая представляет собой соответственно первый процессор 4 или Р1, второй процессор 6 или Р2 и третий процессор 8 или Р3.

Каждый процессор 4, 6, 8 через соответствующий вход 10, 12, 14 получает одни и те же входные данные, поступающие от заранее определенной железнодорожной системы 9.

Каждый процессор 4, 6, 8 соответственно выполнен с возможностью исполнения вычислительной программы или набора команд, загруженных из соответствующей программной базы данных 16, 18, 20, с которой он связан.

Каждый процессор 4, 6, 8 выполнен с возможностью обмена оперативными данными с соответствующей базой оперативных данных 22, 24, 26.

Каждый процессор 4, 6, 8 содержит соответствующий выход 28, 30, 32, выполненный с возможностью передачи выходных данных S(P1), S(P2), S(P3) после обработки.

Устройство 2 диверсифицированного безопасного управления содержит также блок 34 выбора команды, содержащий в данном случае три входа 36, 38, 40. Каждый вход 36, 38, 40 выполнен с возможностью получения выходного сигнала S(P1), S(P2), S(P3), поступающего от каждого процессора 4, 6, 8 или (P1, P2, Р3).

Блок 34 выбора команды содержит выход 42, соединенный с терминалом 44 приема команды.

Структура первого варианта выполнения каждой программной базы данных 16, 18, 20, связанной с каждым процессором 4, 6, 8, схематично показана соответственно на фиг.2А, 2В, 2С.

Первая программная база данных 16, связанная с первым процессором Р1, содержит последовательность автоматических систем 46, 48, 50, 52 или А, В, С, D, упорядоченных согласно первой последовательности в порядке А, В, С, D, и первый планировщик 54 или Seq1, управляющий последовательной работой автоматических систем в этом порядке.

Вторая программная база данных 18, связанная со вторым процессором P2, содержит такие же автоматические системы, упорядоченные согласно второй отдельной последовательности 50, 52, 46, 48 или С, D, А, В, и второй планировщик 56 или Seq2, управляющий последовательной работой автоматических систем в этом порядке.

Третья программная база данных 20, связанная со вторым процессором Р3, содержит автоматические системы, упорядоченные согласно третьей, тоже отдельной последовательности D, С, В, А, и второй планировщик 58 или Seq3, управляющий последовательной работой автоматических систем в этом порядке.

Автоматические системы, соответствующие одному и тому же варианту применения, являются идентичными в каждой программной базе данных в том смысле, что они генерируются на основании одного и того же исходного кода и одного и того же компилятора.

Все автоматические системы каждой базы данных генерируются на основании одного и того же компилятора.

Первая, вторая, третья последовательности, применяемые планировщиками Seq1, Seq2 и Seq3, показаны соответственно на фиг.3А, 3В, 3С. Каждая последовательность 60, 70, 78, сформированная на основании одного и того же цикла 62, содержит начало 64, 72, 80 последовательности, в данном случае А на фиг.3А, С на фиг.3В и D на фиг.3С. Направлением прохождения каждой последовательности 60, 70, 78 является соответственно направление 66, 74, 82, то есть направление по часовой стрелке 66 на фиг.3А, направление по часовой стрелке 74 на фиг.3В и направление против часовой стрелки 82 на фиг.3С. Каждой последовательности 60, 70, 78 соответствует конец 68, 76, 84 последовательности, получаемый в результате прохождения от начала 64, 72, 80 каждой последовательности 60, 70, 78.

На фиг.4А показана совокупность автоматических систем, предназначенных для модульных применений. В данном случае автоматическая система А служит для создания модели маршрута, автоматическая система В служит для создания модели одноуровневого железнодорожного переезда, автоматическая система С моделирует модель оповещения, и автоматическая система D воспроизводит модель стрелочного перевода.

На каждый из двух входов 86, 88 автоматической системы А поступают два входных сигнала E1, E2 от железнодорожной системы, и на выходе 90 он выдает первый внутренний сигнал I1.

Автоматическая система В содержит два входа 92, 94, на каждый из которых поступает первый внутренний сигнал I1 и первый входной сигнал Е1 железнодорожной системы. Автоматическая система В содержит также два выхода 96, 98, выполненные с возможностью выдавать второй внутренний сигнал I2 и первый внешний выходной сигнал S1.

На два входа 100, 102 автоматической системы С поступают соответственно второй внутренний сигнал I2 и первый внешний входной сигнал Е1. Автоматическая система С выдает второй внешний выходной сигнал S2 на выходе 104.

На два входа 106, 108 автоматической системы D поступают соответственно первый внешний входной сигнал Е1 и второй внешний входной сигнал Е2. На своем единственном выходе 110 автоматическая система D выдает третий внешний выходной сигнал S3.

В данном случае первым внешним входным сигналом Е1 является текущее время, тогда как второй внешний входной сигнал Е2 является индикатором прохождения путевого знака железнодорожного пути. В данном случае первая внутренняя переменная I1 представляет собой предусмотренное время прохождения железнодорожного переезда, а вторая внутренняя переменная I2 представляет собой расчетное время подачи команды на оповещение.

Первый внешний выходной сигнал S1 является командой на опускание шлагбаума железнодорожного переезда, второй внешний выходной сигнал S2 является командой на оповещение о перекрывании железнодорожного переезда, тогда как третий внешний выходной сигнал S3 является командой стрелочного перевода.

Каждое оперативное ЗУ 22, 24, 26, связанное с процессором (P1, P2, Р3), содержит регистр 112 состояния начала последовательности и регистр 113 состояния конца последовательности, являющиеся родовыми по отношению к процессорам (Р1, P2, Р3) и показанные соответственно на фиг.4В и 4С.

Каждый из регистров, показанных на фиг.4В и 4С, представлен соответствующим вектором состояния. Вектор состояния регистра 112 начала последовательности, показанный на фиг.4В, содержит семь ячеек памяти 114, 116, 118, 120, 122, 124, 126 и подразделен на три области памяти: первую область 114, 116, которая может запоминать два внешних входных сигнала E1, E2, вторую область I(Pi), 118, 120, запоминающую две внутренние переменные I1(Pi), I2(Pi), и третью область S(Pi), 122, 124, 126, запоминающую внешние выходные данные S1(Pi), S2(Pi) и S3(Pi).

Регистр 113 состояния конца последовательности содержит структуру 130, 132, 134, 136, 138, 140, 142, аналогичную вектору состояния 114, 116, 118, 120, 122, 124, 126 регистра 112 состояния начала последовательности.

Работа устройства диверсифицированного безопасного управления описана со ссылкой на блок-схему на фиг.5 и обеспечивается процессорами P1, P2 и Р3.

На первом этапе 144 железнодорожная система известным образом направляет одни и те же входные данные Е в каждый из процессоров P1, P2 и Р3 для осуществления обработки соответственно 146, 148 и 150. На первом этапе 152 первый процессор Р1 инициализирует регистр 112 состояния начала последовательности, представленный на фиг. 5 регистром состояния V1-ds. Затем он задействует первый автомат 154, в данном случае автомат А, затем второй автомат 156, в данном случае В, затем третий автомат 158, в данном случае С, затем четвертый автомат 160, в данном случае D, согласно первой последовательности, связанной с первым процессором Р1 и показанной на фиг.3А.

В конце последовательности выходные данные, полученные на каждом автомате А, В, С, D, образуют на этапе 162 вектор состояния V1-fs, связанный с регистром 113 состояния конца последовательности.

На следующем тестовом этапе 164 вектор V1-ds состояния начала последовательности сравнивается с вектором V1-fs состояния конца последовательности.

В случае если векторы состояния V1-ds и V1-fs отличаются, исполнение первой последовательности А, В, С, D повторяют, при этом регистр 112 состояния начала последовательности предварительно обновляют вектором состояния V1-fs регистра 113 состояния конца последовательности. В случае если регистры состояния имеют одинаковый вектор состояния V1-ds и V1-fs на этапе 164, извлекают выходные данные на этапе 170.

Обработка 148, осуществляемая процессором Р2, аналогична обработке, производимой первым процессором Р1, за исключением порядка автоматов. Так, в начале обработки выполняют задачу инициализации 172 регистра состояния начала последовательности, в данном случае V2-ds. Вместе с тем, исполнение последовательности отличается, так как придерживаются второй последовательности, показанной на фиг.3В, а именно в порядке С, D, А, В.

Осуществляют также тест 176 сравнения векторов состояния начала последовательности V2-ds и конца последовательности V2-fs и обновление 178 регистра начала последовательности в случае, если результат теста оказался отрицательным.

Если тест показал положительный результат, на этапе 180 извлекают выходные данные S(P2) обработки второго процессора.

Точно так же обработка 150 третьего процессора Р3 аналогична обработке первого и второго процессоров P1, P2 за исключением порядка.

Осуществляют также этап инициализации 182 регистра 112 состояния начала последовательности. Прохождение последовательности автоматов осуществляется согласно третьей последовательности, показанной на фиг.3С, а именно последовательности D, С, В, А.

Точно так же выходные данные S(P3) автоматов поступают на регистр состояния начала последовательности на этапе 184. Осуществляют аналогичный тест 186 сравнения векторов состояния V3-ds и V3-fs регистра 112 состояния начала последовательности и регистра 113 состояния конца последовательности. Исполнение последовательности повторяют до тех пор, пока тест не окажется положительным.

В случае если тест оказывается отрицательным, регистр состояния конца последовательности обновляет на этапе 188 регистр 112 состояния начала последовательности. Если тест оказывается положительным, выходные данные S(P3) третьего процессора Р3 извлекаются на этапе 186 и направляются в блок 34 выбора команды. Каждый выходной сигнал S(P1), S(P2), S(P3) каждого процессора направляется в блок 34 выбора команды. На этапе выбора команды 192 сравниваются выходные значения каждого процессора.

В случае если все выходные значения оказываются равными, выходная команда С равна одному из выходных значений S(P1), S(P2), S(P3) и на этапе 194 подтверждается и направляется на приемный терминал 44 управления железнодорожной системы.

В случае если одно из этих данных отличается, на этапе 196 сигнализация оповещает о неисправности устройства диверсифицированного безопасного управления.

В варианте, последовательность, сформированная на основании совокупности автоматов 198, 200, 202, 204, 206, 208, 210, 212, 214, 216 второго варианта выполнения программной базы данных, описана со ссылками на фиг.6А, 6В, 6С, 6D и 6Е, рассматриваемыми в совокупности.

На фиг.6А эти автоматы распределены и обозначены Р, Q, R, S, Т, U, V, W, X, Y, Z.

Совокупность автоматов 198, 200, 202, 204, 206, 208, 210, 212, 214, 216 подразделена на три подгруппы 218, 220, 222 или SG1, SG2, SG3, соответственно первую подгруппу 218 или SG1, образованную автоматами Р, Q, R, вторую подгруппу 220 или SG2, образованную автоматами S, Т, V, W, и третью подгруппу 222 или SG3, образованную автоматами X, Y, Z.

Последовательность 224 подгрупп показана на фиг.6В в виде цикла 226 подгрупп, образованного последовательностью SG1, SG2, SG3, началом последовательности 228, в данном случае SG1, направлением прохождения 230, в данном случае по часовой стрелке, и концом 242 последовательности подгруппы 232, в данном случае SG3.

Последовательность 240 первой подгруппы SG1 показана на фиг.6С. Последовательность первой подгруппы 240 образована на основании цикла 236, в данном случае Р, Q, R, началом 238 последовательности которого в данном случае является автомат Q, направлением прохождения которого является направление 240, в данном случае по часовой стрелке, при этом концом 242 последовательности является автомат Р.

Последовательность 244 второй подгруппы SG2 показана на фиг.6D в виде цикла 246, в данном случае S, Т, V, W, при этом началом 248 этой последовательности является автомат S, прохождение цикла 250 осуществляется по часовой стрелке, и конец 252 последовательности определен автоматом W.

Наконец, последовательность третьей подгруппы SG3 сформирована в виде цикла 256, в данном случае X, Y, Z, при этом началом 258 последовательности является автомат Z, и прохождение 260 цикла осуществляется в направлении 260, в данном случае против часовой стрелки, и в этом случае конец 262 последовательности определяется автоматом X. Полученная таким образом последовательность автоматов образована логическим объединением частичных последовательностей 234, 244, 254 в соответствии с последовательностью подгрупп SG1, SG2, SG3.

Таким образом, последовательностью автоматов, описанной со ссылками на фигуры, является Q, R, Р, S, Т, V, W, Z, Y, X.

Таким образом, разные наборы команд, сформированные на основании разного соответствующего упорядочения модульных прикладных автоматических систем, позволяют использовать разные цепи активации схем в каждом из процессоров идентичной архитектуры, при этом цепь определяют относительно родовой архитектуры процессоров.

Таким образом, полученные отдельные наборы команд в первую очередь отвечают условиям диверсификации, налагаемым требованиями железнодорожной безопасности устройства управления.

Кроме того, способ выработки этих отдельных наборов команд является простым в осуществлении, так как позволяет использовать только одну плату для развертывания программного обеспечения.

Действительно, развертывание прикладных модулей с использованием только одного компилятора является простым, при этом прикладные модули можно повторно использовать от одной ветви обработки к другой.

В варианте, описанное выше устройство безопасного управления можно также использовать без внесения существенных модификаций для бортовых систем управления полетами на самолетах или космических аппаратах или для систем защиты или блокировки ядерных установок.

В варианте, описанное выше устройство безопасного управления можно использовать в любых областях обеспечения безопасности.

1. Устройство (2) диверсифицированного безопасного управления системой, содержащее: комплект из, по меньшей мере, двух процессоров (4, 6, 8) формирования команд, предназначенных для управления железнодорожной системой, установленных параллельно с возможностью приема на соответствующем входе (10, 12, 14) идентичных входных данных Е, при этом каждый процессор (4, 6, 8) выполнен с возможностью приема разных наборов команд, позволяющих производить вычисления и выдавать на соответствующие выходы (28, 30, 32) идентичные выходные данные S(P1), S(P2), S(P3) в соответствии с идентичными входными данными Е, блок (34) выбора команды, содержащий, по меньшей мере, два входа (36, 38, 40), при этом каждый вход (36, 38, 40) соединен с выходом (28, 30, 32) процессора (4, 6, 8), и командный выход (42), выполненный с возможностью выдачи командного сигнала, выбранного среди выходных данных, полученных от процессоров (4, 6, 8), в зависимости от заранее определенного критерия, при этом каждый набор команд, связанный с процессором (4, 6, 8), обеспечивает исполнение, по меньшей мере, двух модульных прикладных автоматических систем (46, 48, 50, 52), при этом модульные прикладные автоматические системы (46, 48, 50, 52) являются идентичными для всех наборов команд, каждый набор команд (16, 18, 20), связанный с процессором (4, 6, 8), может формировать планировщик (54, 56, 58) последовательной активации модульных прикладных автоматических систем (46, 48, 50, 52) согласно соответствующей последовательности (60, 70, 78), и каждый планировщик (54, 56, 58) отличается от других планировщиков (56, 58; 54, 58; 54, 56) присущей ему соответствующей последовательностью (60, 70, 80), отличающееся тем, что каждый планировщик может активировать и упорядочивать модульные прикладные автоматические системы согласно отдельной последовательности, образованной рядом (224) частичных последовательностей (234, 244, 254) модульных прикладных автоматических систем (198, 200, 202, 204, 206, 208, 210, 212, 214, 216), сгруппированных в подгруппы (218, 220, 222), входящие в совокупность модульных прикладных автоматических систем устройства (2) управления.

2. Устройство (2) диверсифицированного безопасного управления по п.1, отличающееся тем, что подгруппы (218, 220, 222) автоматических систем одинаковы для всех процессоров (4, 6, 8).

3. Устройство (2) диверсифицированного безопасного управления по одному из пп.1 и 2, отличающееся тем, что каждая модульная прикладная автоматическая система (46, 48, 50, 52) содержит входы автоматической системы и выходы автоматической системы (90, 96, 98, 104, 110), при этом вход автоматической системы является внешним, если он может принимать входную переменную данную (E1, E2) устройства (2) управления, при этом выход автоматической системы является внешним, если он может выдавать выходную переменную данную (S1, S2, S3) устройства (2) управления, при этом вход и выход одного и того же автоматической системы или двух разных автоматических систем являются внутренними, если они могут быть соединены друг с другом и производить между собой обмен одной и той же переменной данной (I1, I2), при этом совокупность входных переменных данных (86, 88, 92, 94, 100, 102, 106, 108) и выходных переменных данных (90, 96, 98, 104, 110) автоматических систем образует вектор состояния (114, 116, 118, 120, 122, 124, 126) устройства (2) управления, и тем, что устройство управления (2) для каждого процессора (4, 6, 8) содержит оперативное запоминающее устройство (22, 24, 26), содержащее: регистр (112) состояния начала исполнения последовательности автоматических систем, содержащий значения совокупности переменных состояния (E1, E2, I1, I2, S1, S2, S3) перед исполнением последовательности автоматических систем, регистр (113) состояния конца исполнения последовательности автоматических систем, содержащий значения совокупности переменных состояния вектора состояния, полученного после исполнения последовательности автоматических систем.

4. Устройство (2) диверсифицированного безопасного управления по п.3, отличающееся тем, что для каждого процессора (4, 6, 8) и в течение исполнения последовательности процессор может считывать только в регистре (112) состояния начала и записывать только в регистре (113) состояния конца.

5. Устройство (2) диверсифицированного безопасного управления по п.4, отличающееся тем, что для каждого процессора (4, 6, 8), регистр (112) состояния начала последовательности может быть записан и обновлен только в конце исполнения последовательности при помощи значений переменных состояния, содержащихся в регистре (113) конца последовательности, и тем, что каждый процессор (4, 6, 8) может повторять исполнение последовательности автоматов до момента, когда значения переменных состояния, по меньшей мере, двух соответствующих регистров (112, 113) состояния, станут одинаковыми.

6. Устройство (2) диверсифицированного безопасного управления по любому из пп.1 и 2, отличающееся тем, что каждый процессор (4, 6, 8) содержит программную базу данных (16, 18, 20), содержащую набор процессорных команд, выполненный с возможностью загрузки в процессор (4, 6, 8) и исполнения последовательности прикладных автоматических систем (46, 48, 50, 52) согласно последовательности, заданной планировщиком, связанным с процессором.

7. Устройство (2) диверсифицированного безопасного управления по п.6, отличающееся тем, что каждая программная база данных (16, 18, 20) содержит набор команд, сформированный одним и тем же компилятором.

8. Устройство (2) диверсифицированного безопасного управления по любому из пп.1 и 2, отличающееся тем, что блок (34) выбора команды является блоком решения мажоритарной выборки среди выходных данных (S(P1), S(P2), S(P3)), поступающих от всех процессоров (4, 6, 8), при этом блок (34) выполнен с возможностью сравнения выходных данных, поступающих от соответствующих выходов каждого процессора (4, 6, 8), и передачи выходных данных, мажоритарно общих относительно всех процессоров согласно заранее определенному критерию большинства.

9. Устройство (2) диверсифицированного безопасного управления по п.8, отличающееся тем, что блок (34) выбора команды является блоком решения единогласной выборки.

10. Устройство (2) диверсифицированного безопасного управления по любому из пп.1 и 2, отличающееся тем, что выполнено с возможностью управления системой железнодорожной безопасности.

11. Способ диверсифицированного безопасного управления системой, содержащий следующие этапы: по меньшей мере, в два процессора (4, 6, 8) загружают два разных набора команд из соответствующих программных баз данных (16, 18, 20), на соответствующие входы (10, 12, 14) параллельных процессоров (4, 6, 8) передают идентичные входные данные (Е), при помощи каждого процессора (4, 6, 8) исполняют соответствующий ему разный набор команд, позволяющий вычислять и выдавать на соответствующие выходы (28, 30, 32) идентичные выходные данные (S(P1), S(P2) S(P3)) в зависимости от идентичных входных данных Е, при этом исполнение набора команд процессором (4, 6, 8) содержит следующие этапы: исполняют, по меньшей мере, две модульные прикладные автоматические системы (46, 48, 50, 52), при этом модульные прикладные автоматические системы являются идентичными для каждого набора команд, согласно соответствующей последовательности, отличной от последовательностей других наборов команд, при этом отдельной последовательности, образованной рядом (224) частичных последовательностей (234, 244, 254) модульных прикладных автоматических систем (198, 200, 202, 204, 206, 208, 210, 212, 214, 216), сгруппированных в подгруппы (218, 220, 222), входящие в совокупность модульных прикладных автоматических систем устройства (2) управления, извлекают выходные данные (S(P1), S(P2), S(P3)), полученные в конце исполнения последовательности, выходные данные направляют (170, 180, 190) в блок выбора команды, и командный сигнал выбирают из выходных данных, поступивших из процессоров (4, 6, 8), в зависимости от определенного критерия.

12. Способ безопасного управления (143) по п.11, отличающийся тем, что дополнительно содержит следующие этапы: в зависимости от критерия выбора подтверждают или соответственно запрещают передачу команды, полученной из множества полученных выходных данных (S(P1), S(P2), S(Р3)), и в случае запрещения указывают (196) на наличие сбоя в работе, по меньшей мере, одного процессора (4, 6, 8).