Системы и способы для снижения потребления динамической мощности при работе электронного запоминающего устройства

Иллюстрации

Показать всеИзобретение относится к вычислительной технике, а именно к электронной памяти. Техническим результатом является снижение мощности в электронном запоминающем устройстве. Запоминающее устройство содержит последовательно сегментированную разрядную линию для доступа к данным в упомянутом запоминающем устройстве, повторитель с защелкой, управляющий сегментами разрядной линии, причем повторитель с защелкой управляется разрядами адреса памяти и определителями, выбранными из списка сигналов разрешения чтения и сигналов разрешения записи. Способ описывает работу данного запоминающего устройства. 4 н. и 11 з.п. ф-лы, 4 ил.

Реферат

Область техники, к которой относится изобретение

Данное описание относится к работе электронной памяти и, в частности, к системам и способам для снижения потребления мощности при работе запоминающих устройств.

Уровень техники

Величина потребляемой мощности имеет большое значение в операциях электронного запоминающего устройства. Потребляемая мощность разделяется на две категории, а именно резервная мощность и динамическая мощность. В резервном или статическом режиме память использует наименьшую мощность, так как не выполняются операции ни чтения, ни записи. Потребление динамической мощности происходит во время переключения, когда происходит доступ к памяти для чтения и/или записи.

Потребление мощности в памяти можно уменьшить, ограничивая частоту переключения и/или снижая линейную емкость, поскольку:

P=CV2fA,

где P - динамическая мощность; C - линейная емкость; V - напряжение, приложенное к рабочей строке; f - частота доступа к памяти; и A - коэффициент активности, т.е. число переключений, когда система выполняет циклы чтения и записи.

Часто потреблением мощности памяти управляют путем разделения памяти на группы и затем приведения в действие каждый раз только одной группы.

Одна из причин создания групп - уменьшение переключаемой емкости и уменьшение активности переключения, что в свою очередь снижает динамическую мощность. Обычно частота плохо поддается управлению, поскольку желательно управлять памятью на высоких частотах. Уменьшение операционного напряжения - очень мощное средство снижения динамической мощности, поскольку достигается "кубический" эффект при сопутствующем уменьшении частоты. Однако уменьшение напряжения оказывает влияние на характеристики. Ограничение размаха сигнала также уменьшает динамическую мощность, но такие схемы сложны. Уменьшение коэффициента активности (количество переключений на цикл) является еще одним эффективным методом снижения динамической мощности и связано со стробированием тактового сигнала, логической оптимизацией и методами проектирования схем (группировка является хорошим примером). В дополнение ко всему этому, надлежащее экранирование сигнала (временное, логическое и физическое) ведет к экономии динамической мощности, особенно в широких шинных структурах. Настоящее изобретение имеет преимущество над всеми этими методами.

Сущность изобретения

Снижение мощности в электронном запоминающем устройстве осуществляется путем сегментации разрядных линий и осуществления разрешения только для определенных сегментов разрядных линий в зависимости от того, где будет происходить доступ к памяти. В одном из вариантов изобретения разрядные линии сегментированы с помощью повторителей с защелкой для управления выбором адреса по отношению к сегментам за пределами первого сегмента. Повторители с защелкой в одном варианте могут оставаться в управляемом/неуправляемом состоянии при завершении цикла чтения/записи памяти. Это позволяет избежать последовательных разрешающих импульсов, когда к тому же самому сегменту осуществляется доступ в последовательных циклах.

В одном варианте описано запоминающее устройство, имеющее по меньшей мере одну сегментированную разрядную линию для доступа к данным в памяти таким образом, что разрядная линия содержит сегменты, приводимые в действие повторителем с защелкой. В одном варианте разрешенное/неразрешенное состояние повторителя с защелкой управляется определенными битами адреса памяти.

В одном варианте работа запоминающего устройства осуществляется для снижения мощности так, что определенные секторы сегментируются, так что менее чем вся память опрашивается для определенных доступов к памяти. Во время любого цикла опроса памяти является возможным в зависимости от адреса, по которому осуществляется доступ, осуществлять разрешение только для необходимых сегментов памяти.

Выше описаны в довольно широком аспекте признаки и технические преимущества настоящего раскрытия сущности изобретения, чтобы последующее подробное описание было более понятным. Будут описаны дополнительные признаки и преимущества, которые составляют предмет формулы изобретения. Специалистам должно быть понятно, что концепция и конкретные описанные варианты осуществления могут непосредственно использоваться в качестве основы для модификации или проектирования других структур для достижения целей настоящего устройства. Специалистам также должно быть понятно, что подобные эквивалентные конструкции находятся в пределах сущности и объема изобретения, определенных формулой изобретения. Новые признаки, которые характеризуют данное изобретение относительно организации и метода функционирования, вместе с дальнейшими целями и преимуществами будут более понятны из последующего описания при рассмотрении вместе с прилагаемыми чертежами. Однако необходимо понять, что каждый из чертежей представлен только с целью иллюстрации и описания, а не для ограничения настоящего изобретения.

Краткое описание чертежей

Для более полного понимания настоящего изобретения ссылки далее даются на последующее описание совместно с приложенными чертежами.

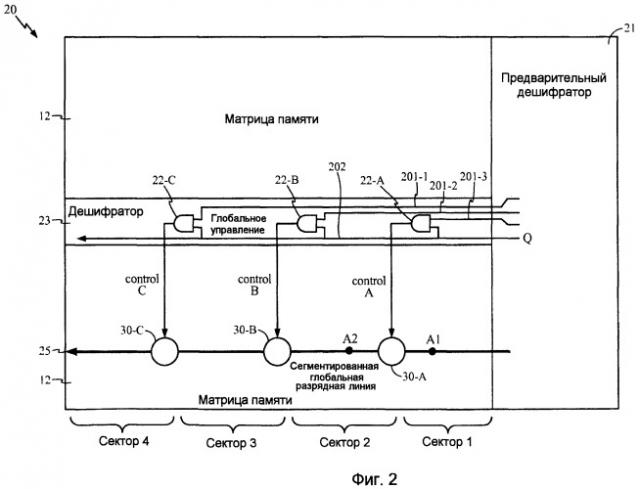

Фиг.1 - блок-схема, иллюстрирующая типовое запоминающее устройство предшествующего уровня техники.

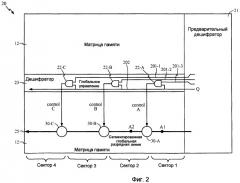

Фиг.2 - блок-схема, иллюстрирующая сегментированные разрядные линии, использующие по меньшей мере один повторитель с защелкой.

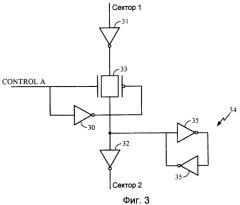

Фиг.3 - схема соединений, иллюстрирующая один вариант повторителя с защелкой, используемого в варианте осуществления по фиг.2.

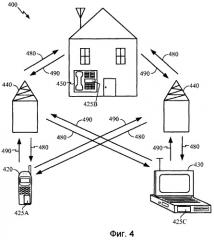

Фиг.4 - блок-схема, иллюстрирующая пример системы беспроводной связи, в которой можно выгодным образом использовать вариант осуществления изобретения.

Подробное описание изобретения

Фиг.1 иллюстрирует типовое ЗУ 10 предшествующего уровня техники. Это запоминающее устройство (ЗУ) может представлять собой статическое ЗУПВ, динамическое ЗУПВ, магниторезистивное ЗУПВ или другие типы памяти. Запоминающее устройство 10 обычно создается с использованием предварительного дешифратора, такого как предварительный дешифратор 11, и дешифратора, такого как дешифратор 13. Матрицы 12 и 14 памяти являются матрицами, содержащими ячейки памяти. Матрицы 12 и 14 памяти состоят из ряда глобальных разрядных строк (например, 15), которые могут использоваться для чтения и/или записи.

Запоминающее устройство потребляет динамическую мощность в соответствии с ее размером (длина разрядных линий) и мощностью памяти, как было упомянуто выше. Емкость C разрядных линий определяется, главным образом, технологией изготовления и составляет приблизительно 0,25 фемтофарад на микрон. Таким образом, 300-микронная разрядная линия будет иметь ассоциированную с ней емкость 75 фемтофарад. Соответственно, емкость 75 fF будет минимальной емкостью переключения. Как будет рассмотрено далее, уменьшение потребления мощности может достигаться выборочным изменением количества элементов памяти, которые активированы для данного доступа к памяти.

На фиг.2 показан вариант осуществления изобретения с использованием по меньшей мере одного повторителя 30-A, 30-B, 30-C с защелкой внутри запоминающего устройства 20. Повторители 30-A, 30-B, 30-C с защелкой могут быть использованы для разбиения глобальной разрядной линии в сегментированную разрядную линию 25, таким образом позволяя эффективно уменьшить активную длину разрядной линии и, следовательно, емкости для нескольких циклов памяти. Уменьшение емкости приводит к общему уменьшению потребления мощности памяти.

Дешифратор 23 повторителя с защелкой определяет, какой повторитель 30-A, 30-B, 30-C с защелкой активирован в определенный момент времени в зависимости от того, к какому элементу матрицы осуществляется доступ. Возбудители 22-A, 22-B и 22-C дешифратора защелки находятся внутри дешифратора 23 повторителя с защелкой. Возбудители 22-A, 22-B и 22-C дешифратора защелки фиксируют повторители 30-A, 30-B, 30-C в заданный момент времени. Возбудители 22-A, 22-B и 22-C дешифратора могут активировать только один повторитель с защелкой или множество повторителей 30-A, 30-B, 30-C с защелкой в заданное время.

В представленном варианте осуществления матрица ЗУ и глобальная разрядная линия разделены на четыре сектора, и сегменты разрядной линии отделены тремя повторителями 30-А, 30-В и 30-С с защелкой. Сегмент разрядной строки для сектора 1 в данном варианте осуществления всегда находится во включенном состоянии, и, таким образом, нет необходимости в наличии повторителя с защелкой внутри сегментированной разрядной линии 25 для сектора 1. С целью осуществления доступа к элементу ЗУ в секторе 2 повторитель 30-А с защелкой должен быть активирован. Таким же образом повторитель 30-В с защелкой управляет доступом к ЗУ в секторе 3, а повторитель 30-С с защелкой управляет доступом к памяти в секторе 4.

Хотя на фиг.2 изображено четыре сектора, на самом деле память может быть разделена на любое количество секторов в зависимости от потребностей пользователя. Сокращение емкости разрядной линии может быть достигнуто с использованием данного секторного подхода. Например, если имеется доступ к сектору 1, тогда возбудитель дешифратора (например, 22-А) отсекается, и таким образом остается только емкость разрядной линии до повторителя 30-А с защелкой. Если же необходим доступ к сектору 2, возбудитель 22-А дешифратора активирует повторитель 30-А с защелкой, и емкость линии увеличивается. Доступ к секторам 3 и 4 вызовет дальнейшее увеличение емкости, когда возбудители 22-В и/или 22-С дешифратора активируют повторители 30-В и 30-С с защелкой для доступа к секторам 3 и 4 соответственно.

Заметим, что хотя на фиг.2 изображена только одна сегментированная разрядная линия 25, для 64-х разрядного ЗУ ввода-вывода будут присутствовать наборы из 64-х разрядных линий. Для многопортового ЗУ должен существовать один набор ресурсов (возбудитель дешифратора и повторитель с защелкой) для каждого порта. Однопортовое ЗУ имеет один набор сегментированных разрядных линий 25 для чтения и один набор сегментированных разрядных линий 25 для записи.

Возбудители 22-А, 22-В, 22-С дешифраторов и повторители 30-А, 30-В и 30-С с защелкой будут вводить задержку во время доступа и потреблять мощность и, таким образом, могут повлиять на характеристики ЗУ. Несмотря на это, в целом характеристики улучшаются, поскольку, как было изложено выше, по статистике большинство доступов осуществляется в средней части ЗУ. Более того, каждый вводимый повторитель 30-А, 30-В, 30-С с защелкой уменьшает задержку относительно дальнего конца разрядной линии вследствие более коротких длин разрядных линий. Задержка линии пропорциональна R*C. R и C соответственно обратно пропорциональны длине линии. Таким образом, задержка обратно пропорциональна квадрату длины линии. Когда линия расщепляется на две части, задержка в результате этого сокращается в четыре раза. По этой причине при использовании повторителя 30-А с защелкой происходит увеличение быстродействия.

Более того, повторители 30-А, 30-В и 30-С с защелкой увеличивают крутизну сигналов, вводимых в логические схемы, снижая таким образом вероятность короткого замыкания. Крутизна входного сигнала на логической схеме определяет, какое время прибор находится в режиме короткого замыкания с одновременно включенными нагрузочным и разгрузочным транзисторами. Обычно мощность короткого замыкания составляет 10-15% всей динамической мощности. Но если крутизна входного сигнала действительно недостаточна, мощность короткого замыкания может составлять значительную величину. Разделение линии на сегменты и добавление повторителей в целом улучшает крутизну входного сигнала в каждой секции.

Единственный недостаток при добавлении логических схем и повторителей заключается в необходимости увеличения пространства на подложке. Однако при совершенствовании технологии и уменьшении размеров от 45 нанометров до 32 нанометров и менее дополнительное пространство становится доступным без увеличения площади подложки.

Далее описано управление возбудителем дешифратора, основанное на адресации памяти. При работе каждое ЗУ требует определенного количества разрядов адреса каждый раз, когда осуществляется доступ к памяти. Например, рассмотрим 8-разрядную адресную структуру. Такая структура будет иметь разряды от a0 до а7, которые позволяют осуществить доступ к 256 ячейкам памяти. Разряд а7 - это наиболее значимый разряд (MSB - старший значащий бит) адреса. Если разряд а7 является нулем, то доступ будет осуществляться в секторах 1 или 2, а если разряд a7 является 1, то доступ будет осуществляться в секторах 3 и 4. Таким образом, если MSB равен единице, сигнал будет послан через выводы 201-2, 201-3 к вероятно активным повторителям 30-А и 30-В с защелкой. Активация повторителя может зависеть от определяющего сигнала, посланного по выводу Q, как будет изложено далее.

Адреса обычно возникают рано в цикле чтения или записи (до нарастания фронта тактового импульса) таким образом, что система предварительного дешифратора "знает" заранее, в какие сектора будет осуществляться доступ. Используя это знание, предварительный дешифратор (если разряд a7 равен 1) может подготовиться к запуску возбудителей 22-А и 22-В дешифратора (и связанных с ними повторителей 30-А и 30-В с защелкой), в то время как запуск возбудителя 22-С дешифратора (и связанного с ним повторителя 30-С с защелкой) еще должен быть определен. И наоборот, если разряд a7 равен 0, только возбудитель 22-А дешифратора и связанный с ним повторитель 30-С с защелкой получат возможность запуска, причем их состояние запуска будет определяться на основании анализа следующего наиболее значимого разряда a6.

При использовании разряда a6 предварительный дешифратор 21 может разрешить состояние возбудителей 22-А и 22-С дешифратора и связанных с ними повторителей 30-А и 30-С с защелкой. Значение разряда а6 определяет, будет ли целевой доступ к памяти осуществляться в верхнем или нижнем секторе из секторов, выбранных разрядом а7. Таким образом, предположим, что разряд а7 находится в состоянии 1 и a6 также в состоянии 1, тогда возбудитель 22-С дешифратора и связанный с ним повторитель 30-С с защелкой будут активированы сигналом по выводу 201-1, поскольку доступ к памяти будет осуществляться в секторе 4. Таким же образом, если разряд а7 находится в состоянии 0 и разряд а6 также в состоянии 0, то возбудители дешифратора или повторители с защелками будут активированы, поскольку целевой доступ к памяти будет осуществляться в секторе 1.

В одном варианте осуществления изобретения возбудители 22-А, 22-В и 22-С дешифратора частично управляются сигналами на выводах 201-1, 201-2, 201-3 соответственно от предварительного дешифратора 21. Чтобы избежать переключения без необходимости, определители, такие как сигналы разрешения чтения или записи, могут быть использованы через вывод Q из предварительного дешифратора 21 в дополнение к сигналам, относящимся к разрядам адреса, для осуществления разрешения для различных секторов. В этом варианте осуществления возбудители 22-А, 22-В и 22-С дешифратора могут быть логическими схемами "И". Например, если получены оба сигнала: сигнал разрешения записи и сигнал разряда адреса, возбудитель 22-А дешифратора и повторитель 30-А с защелкой будут активированы. Если определитель не используется, то возбудители 22-А, 22-В и 22-С дешифраторов могут быть инверторами, а не логическими схемами "И". Также заметим, что любая из ряда конфигураций доступа к памяти может использоваться для управления возбудителями 22-А, 22-В и 22-С дешифраторов, включая посылку информации непосредственно из другого местоположения относительно выбора определенного сектора.

На фиг.3 показан один пример повторителя 30-А с защелкой, используемого в варианте осуществления по фиг.2. Повторитель 30-А с защелкой расположен между точками А1 и А2 (фиг.2) сегментированной разрядной линии 25. Как показано на чертеже, повторитель 30-А содержит два последовательно соединенных инвертора 31 и 32. Изображена также защелка 34 (включающая в себя два инвертора 35), которая открывается или закрывается в зависимости от переключателя, такого как вентиль 33 пропускания. Вентиль 33 пропускания открывается и закрывается в ответ на сигнал на управляющей линии control A, полученный от возбудителя 22-А дешифратора для сектора 2. Отметим, что структура 30-А показана только в качестве примера, т.к. для выполнения описанной функции могут применяться и другие структуры.

При работе схемы, если предположить, что а7 находится в состоянии 1 (и определяющий сигнал установлен), повторитель 30-А с защелкой должен включаться. Таким образом, вентиль 33 пропускания получает сигнал 1 из управляющей линии control A. В ответ на это N-канал вентиля 33 пропускания переходит в состояние 1, а Р-канал переходит в состояние 0, включая повторитель с защелкой. Если повторитель с защелкой включен, данные сегмента разрядной линии сектора 1 переходят в сегмент разрядной линии сектора 2, и также осуществляется обновление защелки 34 этими данными.

В результате того что защелка 34 сохраняет значение данных, защелка 34 затем осуществляет управление значением разрядной линии в сегменте выше повторителя 30-А с защелкой, в данном случае сегментом разрядной линии сектора 2. Будучи установленными, данные остаются в том же состоянии до момента их активного изменения путем повторного открытия вентиля 33 пропускания. Вследствие этого сегмент разрядной линии сектора 2 сохраняет фиксированное значение, т.е. сегмент разрядной линии сектора 2 управляется повторителем 30-А с защелкой. Если следующее значение данных, вводимое в сектор 2, является тем же, что и у предыдущих данных, то нет необходимости разряда сегмента разрядной линии сектора 2, поскольку на разрядной линии сектора 2 уже имеется фиксированное значение. Таким образом, рассматриваемая структура имеет эффект предыстории, заключающийся в том, что если все повторители 30-А, 30-В и 30-С с защелками открыты и на всех сегментах разрядной линии должна появиться 1 для следующего рабочего цикла, ни один из сегментов разрядной линии не будет снова разряжаться.

Некоторые применения ЗУ можно адаптировать для использования преимуществ структуры такого ЗУ таким образом, чтобы можно было хранить данные в соответствии с их ожидаемой частотой доступа. Соответственно, путем хранения данных, имеющих высокую частоту доступа, в верхней половине ЗУ, а данных с более низкой частотой доступа - в нижней половине, можно получить более значительную экономию мощности, чем при произвольном хранении данных.

Заметим, что несмотря на то, что обсуждаются в основном разрядные линии, сущность данного изобретения может быть применена к линиям слов, а также к линиям слов в сочетании с разрядными линиями. В таком устройстве линии слов будут сегментированы контроллерами сегментов. Контроллеры сегментов управляются отдельными сигналами управления, поступающими на них вне адресного поля, ограничивая работу ЗУ той частью, где происходит доступ к памяти в данное время.

На фиг.4 показан пример системы беспроводной связи 400, в которой применен вариант данного изобретения. Чтобы проиллюстрировать изобретение, на фиг.4 показаны три дистанционных устройства 420, 430 и 450 и две базовые станции 440. Понятно, что такие системы беспроводной связи могут иметь намного больше дистанционных устройств и базовых станций. Дистанционные устройства 420, 430 и 450 включают усовершенствованные полноразрядные матрицы 425А, 425В и 425С соответственно, которые являются вариантами осуществления изобретения, как будет описано ниже. На фиг.4 показаны сигналы 480 прямой линии связи от базовых станций 440 к дистанционным устройствам 420, 430 и 450 и сигналы 490 обратной линии связи от дистанционных устройств 420, 430 и 450 к базовым станциям 440.

На фиг.4 дистанционное устройство 420 представляет собой мобильный телефон, дистанционное устройство 430 - портативный компьютер, а дистанционное устройство 450 - стационарное дистанционное устройство в системе беспроводного локального шлейфа. Например, дистанционные устройства могут быть сотовыми телефонами, карманными устройствами персональной системы связи (PCS), портативными устройствами с блоками передачи данных, такими как персональный цифровой помощник, либо стационарными блоками передачи данных, например, устройства для считывания данных измерений. Хотя на фиг.4 согласно данному изобретению показаны дистанционные устройства, изобретение не ограничено проиллюстрированными примерами устройств. Изобретение может быть также применено в приборах, которые имеют полноразрядные матрицы памяти.

Хотя в качестве примера приведена конкретная схема, специалистам должно быть понятно, что не все описанные схемы необходимы для реализации данного изобретения. К тому же некоторые хорошо известные схемы не были описаны, чтобы сконцентрировать внимание на изобретении. Также, хотя изобретение ссылается на состояния логического "0" и логической "1" в определенных позициях, специалист поймет, что данные логические значения можно переключать. При этом соответственно изменится остальная часть схемы, но это не будет влиять на работу согласно настоящему изобретению.

Несмотря на то что настоящее изобретение и его преимущества были описаны подробно, необходимо понять, что возможны различные изменения, замены и перестановки в пределах объема и сущности данного изобретения, которые определены формулой изобретения. Кроме того, объем настоящей заявки не ограничивается отдельными примерами данного процесса, машины, производства, структур, средств, методов и действий, раскрытых в описании. Из данного описания процессов, машин, производства, структур, средств, методов или действий, которые существуют в настоящее время или будут разработаны в будущем и которые осуществляют в основном ту же самую функцию или достигают того же самого результата, что и соответствующие описанные выше варианты, специалистам должно быть понятно, что тот же самый результат может быть достигнут при использовании в них настоящего изобретения. Соответственно, прилагаемые пункты формулы изобретения предполагают включение в свой объем таких процессов, машин, производства, структур, средств, методов и действий.

1. Запоминающее устройство, содержащее последовательно сегментированную разрядную линию для доступа к данным в упомянутом запоминающем устройстве; повторитель с защелкой, управляющий сегментами разрядной линии, причем повторитель с защелкой управляется разрядами адреса памяти и определителями, выбранными из списка сигналов разрешения чтения и сигналов разрешения записи.

2. Запоминающее устройство по п.1, дополнительно содержащее защелку для сохранения состояния упомянутого повторителя с защелкой при множественных доступах.

3. Способ снижения мощности электронного запоминающего устройства, содержащий выбор сегмента разрядной линии на основе адресных разрядов доступа к памяти и обновление данных по меньшей мере одного повторителя с защелкой на упомянутой разрядной линии для, по существу, одновременного запуска множества последовательных сегментов разрядной линии, включая выбранный сегмент разрядной линии.

4. Способ по п.3, дополнительно содержащий сохранение обновленного значения упомянутого по меньшей мере одного повторителя с защелкой при множественном доступе.

5. Способ по п.3, дополнительно содержащий задержку упомянутого выбора на основе некоторых определителей в дополнение к упомянутым адресным разрядам.

6. Способ по п.3, дополнительно содержащий управление упомянутым по меньшей мере одним повторителем с защелкой, по меньшей мере частично, на основе значения старшего разряда адресных разрядов.

7. Способ снижения мощности электронного запоминающего устройства, содержащий выбор сегмента линии слов на основе адресных разрядов адреса памяти и обновление данных по меньшей мере одного повторителя с защелкой по упомянутой линии слов для, по существу, одновременного запуска множества последовательных сегментов линии слов, включая выбранный сегмент линии слов.

8. Способ по п.7, дополнительно содержащий управление упомянутым по меньшей мере одним повторителем с защелкой, по меньшей мере частично, на основе значения старшего разряда адресных разрядов.

9. Запоминающее устройство, содержащее множество матриц памяти, причем упомянутые матрицы памяти адаптированы для хранения данных;множество последовательно сегментированных разрядных линий, причем по меньшей мере одна разрядная линия предназначена для управления доступом к секторам упомянутых матриц памяти; и по меньшей мере один повторитель с защелкой, расположенный в каждой последовательно сегментированной разрядной линии, причем повторитель с защелкой содержит защелку, действующую для сохранения состояния упомянутого повторителя с защелкой в течение циклов памяти.

10. Запоминающее устройство по п.9, дополнительно содержащее логическую схему для запуска упомянутого повторителя с защелкой, причем упомянутая логическая схема реагирует на определенные разряды адреса доступа, принятого памятью.

11. Запоминающее устройство по п.10, дополнительно содержащее схему управления для установки сигналов для управления упомянутой логической схемой, причем упомянутая схема управления функционирует, по меньшей мере частично, с использованием значений, содержащихся в по меньшей мере одной разрядной позиции адреса, принятого памятью, причем упомянутый адрес соответствует целевому сектору.

12. Запоминающее устройство по п.11, в котором упомянутая схема управления дополнительно действует для обеспечения определителей для дополнительного управления разрешением для упомянутой логической схемы.

13. Запоминающее устройство по п.10, дополнительно содержащее схему для разрешения упомянутому повторителю с защелкой оставаться в разрешенном состоянии в течение более чем одного цикла доступа к памяти.

14. Запоминающее устройство по п.9, в котором упомянутый повторитель с защелкой содержит пару логических схем, разделенных переключателем пропускания, причем упомянутый переключатель пропускания действует для разрешения прохождения данных от первой из упомянутой пары логических схем ко второй из упомянутой пары логических схем, когда упомянутый повторитель с защелкой находится в разрешенном состоянии.

15. Запоминающее устройство по п.9, дополнительно содержащее по меньшей мере один повторитель с защелкой для разделения последовательных сегментов линии слов.