Устройство считывания с временной задержкой и накоплением сигналов с многоэлементных фотоприемников инфракрасного излучения

Иллюстрации

Показать всеУстройство считывания с временной задержкой и накоплением сигналов с многоэлементных фотоприемников инфракрасного излучения относится к области интегральной микроэлектроники и предназначено для систем обработки оптической информации. Устройство содержит m каналов считывания. Каждый канал считывания выполнен из блока считывания с n ячейками считывания, блока каскадов ВЗН сигналов с n каскадами ВЗН сигналов и снабжен k-разрядным сдвиговым регистром, k - число разрядов распределенного аналого-цифрового преобразователя. Блок считывания соединен N разрядной шиной сигналов сравнения напряжений с блоком каскадов ВЗН. Каждая ячейка считывания соединена с соответствующим N-тым разрядом N разрядной шины сигналов сравнения напряжений. Ячейка считывания выполнена в составе интегрирующего усилителя, ячейки выборки и хранения, компаратора, триггера-защелки, логического элемента «И». Аналоговые элементы - интегрирующий усилитель, ячейка выборки и хранения, компаратор последовательно соединены в указанном порядке относительно одного из входов каждого аналоговыми шинами. Интегрирующий усилитель соединен с фотоприемником. Каскад ВЗН выполнен в составе параметрического мультиплексора сигналов сравнения, логического элемента «И», k-разрядного счетчика, k-разрядного элемента с тремя состояниями на выходе, последовательно соединенных в указанном порядке, а также содержит дополнительный k-разрядный сдвиговый регистр. Один из N разрядных входов параметрического мультиплексора соединен с N разрядной шиной сигналов сравнения напряжений. Выход k-разрядного элемента, являющийся выходом каскада ВЗН, соединен К разрядной шиной считывания данных из канала считывания с k-разрядным сдвиговым регистром канала считывания. Выход k-разрядного сдвигового регистра каждого канала считывания соединен шиной передачи данных сдвиговых регистров каналов считывания в направлении увеличения номера канала считывания с k-разрядным сдвиговым регистром следующего по номеру канала считывания. Выход m-того канала считывания соединен с шиной выходных данных устройства. Технический результат заключается в расширении динамического диапазона и возможности считывания сигналов каждым каналом с неограниченного количества фоточувствительных элементов фотоприемника. 6 з.п. ф-лы, 5 ил.

Реферат

Техническое решение относится к области интегральной микроэлектроники и может быть использовано в системах обработки оптической информации.

Известно устройство считывания с временной задержкой и накоплением (ВЗН) сигналов с многоэлементных фотоприемников инфракрасного излучения (патент РФ №2236064 на изобретение, МПК:7 H01L 27/14), выполненное на полупроводниковой подложке, содержащее многоканальную систему считывания в составе m каналов считывания, блока памяти, при этом каждый из m каналов считывания выполнен из блока считывания с n ячейками считывания, блока хранения и суммирования сигналов с ВЗН с n ячейками хранения и суммирования сигналов с ВЗН (каскадов ВЗН), блока записи и хранения информации о дефектных элементах, где m - количество каналов считывания, n - количество каскадов временной задержки и накопления (ВЗН), трех групп шин управления по n в каждой. Ячейка считывания входом соединена с фотоприемником, первым выходом связана с блоком памяти, вторым выходом с первой управляющей шиной, третьим выходом с выходами ячеек считывания других каскадов и входами ячеек хранения и суммирования сигналов с ВЗН. Ячейка считывания содержит узел ввода, выполненный в составе усилителя и первого МДП-транзистора, при этом исток первого МДП-транзистора, являющийся входом ячейки считывания, соединен с выходом фотоприемника, его затвор соединен с выходом усилителя, вход усилителя соединен с истоком первого МДП-транзистора; кроме этого ячейка считывания содержит интегрирующую емкость, второй и третий МДП-транзисторы, причем исток второго МДП-транзистора соединен со стоком первого МДП-транзистора, сток второго МДП-транзистора, являющийся третьим выходом ячейки считывания, соединен со стоками вторых МДП-транзисторов ячеек считывания других каскадов, затвор второю МДЧ-транзистора соединен с истоком третьего МДП-транзистора, затвор третьего МДП-транзистора, являющийся вторым выходом ячейки считывания, соединен с первой управляющей шиной, сток третьего МДП-транзистора, являющийся первым выходом ячейки считывания, соединен с блоком памяти, одна обкладка интегрирующей емкости соединена с истоком второго МДП-транзистора, а вторая ее обкладка соединена с полупроводниковой подложкой. Ячейка хранения и суммирования сигналов с ВЗП первым входом соединена с ячейками считывания, вторым входом соединена со второй управляющей шиной, на выходе первый выход предназначен для соединения с мультиплексором, а второй выход соединен с третьей управляющей шиной. Ячейка хранения и суммирования сигналов с ВЗН выполнена в составе четвертого и пятого МДП-транзисторов, второй интегрирующей емкости, при этом исток четвертого МДП-транзистора, являющийся первым выходом ячейки хранения и суммирования сигналов с ВЗН, предназначен для соединения с мультиплексором, сток четвертого МДП-транзистора соединен с истоком пятого МДП-транзистора, затвор четвертого МДП-транзистора, являющийся вторым выходом ячейки хранения и суммирования сигналов с ВЗН, соединен с третьей управляющей шиной, затвор пятою МДП-транзистора, являющийся вторым входом ячейки хранения и суммирования сигналов с ВЗН, соединен со второй управляющей шиной, а сток пятого МДП-транзистора, являющийся первым входом, соединен со стоками пятых МДП-транзисторов ячеек хранения и суммирования сигналов с ВЗН других каскадов и ячейками считывания, вторая интегрирующая емкость одной обкладкой соединена с истоком пятого МДП-транзистора, а второй обкладкой соединена с полупроводниковой подложкой.

Блок хранения и суммирования сигналов с ВЗН с n ячейками хранения и суммирования сигналов с ВЗН выполнен аналоговым. Устройство считывания реализовано с возможностью вывода данных из него только в аналоговой форме.

В приведенном аналоге к недостаткам относятся ограничение уровня чувствительности фотоприемного устройства при использовании данных устройств считывания с временной задержкой и накоплением сигналов с многоэлементных фотоприемников, ограничение по динамическому диапазону, кроме того, ограничение количества фоточувствительных элементов фотоприемника, с которых возможно считывание сигналов каждым каналом.

Недостатки связаны с разбросом параметров транзисторов, составляющих аналоговые тракты, а также с наличием электромагнитной интерференции проводников, по которым из устройства выводится полезный аналоговый сигнал для последующей внешней обработки.

В известном устройстве используется ВЗН в аналоговой форме, что препятствует считыванию каждым каналом сигналов с неограниченного количества фоточувствительных элементов фотоприемника.

Известно устройство считывания с временной задержкой и накоплением (ВЗН) сигналов с многоэлементных фотоприемников инфракрасного излучения (патент РФ №2325728 на изобретение, МПК:8 H01L 27/14), выполненное на полупроводниковой подложке, содержащее n узлов ввода, где n - количество ВЗН каскадов, n узлов коммутации, (n+1) узлов выборок, (n+1) шин управления, шину управления сбросом. шину напряжения сброса, каждый узел ввода выполнен в составе МДП-транзистора, усилителя, интегрирующей емкости, МДП-транзистора сброса и повторителя напряжения, при этом МДП-транзистор истоком соединен с фотоприемником, затвором - с выходом усилителя, вход которого соединен с истоком МДП-транзистора, сток МДП-транзистора соединен с первой обкладкой интегрирующей емкости, вторая обкладка которой соединена с полупроводниковой подложкой, исток МДП-транзистора сброса соединен с шиной напряжения сброса, его затвор - с шиной управления сбросом, а сток соединен со стоком МДП-транзистора и входом повторителя напряжения, выход которого соединен с входом соответствующего узла коммутации, каждый узел коммутации содержит первый, второй, …, (n+1) коммутационные МДП-транзисторы, истоки которых соединены, являясь входом узла коммутации, стоки i-х коммутационных МДП-транзисторов, где i от 1 до (n+1), из каждого узла коммутации соединены, а затворы первого, второго, …, (n+1) коммутационных транзисторов j-ю узла коммутации соединены, соответственно, с 1+(j-1), 2+(j-1), …, n, (n+1), 1, 2, …, (j-1)-й шиной управления, где j от 1 до n, каждый узел выборок выполнен в составе первой емкости, первого выходного МДП-транзистора, n вторых коммутационных МДП-транзисторов, (n-1) вторых емкостей выборок, (n-1) вторых выходных МДП-транзисторов. при этом первая емкость одной обкладкой соединена с подложкой, а второй - с истоком первою выходного МДП-транзистора, сток первого выходного МДП-транзистора соединен с выходом устройства, затвор первого выходного МДП-транзистора первого, второго, …, (n+1) узлов выборок соединен, соответственно, с (n+1), первой, второй,..., n-й шинами управления, истоки первого, второго, …, n-го вторых коммутационных МДП-тразисторов соединены, их стоки соединены, соответственно, с истоками первого выходною МДП-транзистора и истоками второго, третьего, …, n-го вторых выходных МДП-транзисторов, стоки которых соединены с выходом устройства, одна обкладка второй, третьей …, n-й вторых емкостей выборок соединены с подложкой, а вторые обкладки вторых емкостей соединены, соответственно, с истоками второго, третьего, …, n-го вторых выходных МДП-транзисторов, затворы которых соединены с затвором первого выходного МДП-транзистора, соединенные истоки вторых коммутационных МДП-транзисторов в первом, втором, …, (n+1) узлах выборок соединены, соответственно, со стоками первого, второго, …, (n+1) вторых коммутационных МДП-транзисторов первого узла коммутации, затворы первого, второго, …, n-го вторых коммутационных МДП-транзисторов m-го узла выборок соединены соответственно с m, (m+1), …, n, (n+1), 1, 2, …, (m-2) шинами управления, где m от 1 до (n+1).

К недостаткам данного аналога относятся ограничение уровня чувствительности фотоприемного устройства при использовании данных устройств считывания с временной задержкой и накоплением сигналов с многоэлементных фотоприемников, ограничение по динамическому диапазону, а также ограничение количества фоточувствительных элементов фотоприемника, с которых возможно считывание сигналов каждым каналом.

Недостатки обусловлены разбросом параметров транзисторов, составляющих аналоговые тракты, а также наличием электромагнитной интерференции проводников, но которым из устройства выводится полезный аналоговый сигнал для последующей внешней обработки.

В приведенном устройстве используется ВЗН в аналоговой форме, что препятствует достижению возможности считывания каждым каналом сигналов с неограниченного количества фоточувствительных элементов фотоприемника.

За ближайшее к заявляемому техническому решению принято устройство считывания с временной задержкой и накоплением (ВЗН) сигналов с многоэлементных фотоприемников инфракрасного излучения (И.И. Ли «Устройство считывания для ИК ФПУ с режимом временной задержки и накопления», Автометрия, 2007 г., г.43, №4, с.56-62), выполненное на полупроводниковой подложке, содержащее многоканальную систему считывания в составе m каналов считывания, трех дешифраторов с n ячейками, одного и второго сдвиговых регистров с m ячейками, общей шины записи информации о дефектных элементах, общей шины выхода, при этом каждый из m каналов считывания выполнен из блока считывания с n ячейками считывания, блока хранения и суммирования сигналов с ВЗН с n ячейками хранения и суммирования сигналов с ВЗН (n каскадами ВЗН), блока записи и хранения информации о дефектных элементах с n ячейками записи и хранения информации о дефектных элементах, двух МДП-транзисторов, соответствующей каналу считывания ячейки одного сдвигового регистра и соответствующей каналу считывания ячейки второго сдвигового регистра, шины передачи фотосигналов, шины передачи информации о дефектных элементах, шины ВЗН сигналов, шины записи информации о дефектных элементах, где m - количество каналом считывания, n - количество каскадов временной задержки и накопления (ВЗН), каждая ячейка считывания на входе первым входом связана с фотоприемником, вторым входом связана с шиной передачи информации о дефектных элементах, на выходе первым выходом связана с шиной передачи фотосигналов, вторым выходом связана с соответствующей ячейкой первого дешифратора, каждая ячейка хранения и суммирования сигналов с ВЗН на входе первым входом связана с шиной передачи фотосигналов, вторым входом связана с соответствующей ячейкой второго дешифратора, а на выходе первым выходом связана с шиной ВЗН сигналов, вторым выходом связана с соответствующей ячейкой третьего дешифратора, к шине ВЗН сигналов подключен сток одного МДП-транзистора, его затвор соединен с соответствующей каналу ячейкой одного сдвигового регистра, а исток соединен с общей шиной выхода, каждая ячейка записи и хранения информации о дефектных элементах первым входом соединена с шиной записи дефектных элементов, вторым входом - со вторым выходом соответствующей ячейки хранения и суммирования сигналов с ВЗН, который соединен с соответствующей ячейкой третьего дешифратора, а на выходе - первым выходом соединена с шиной передачи информации о дефектных элементах, вторым выходом связана со вторым выходом соответствующей ячейки считывания, который соединен с соответствующей ячейкой первого дешифратора, с соответствием номеров ячеек считывания, ячеек хранения и суммирования сигналов с ВЗН, ячеек записи и хранения информации о дефектных элементах, ячеек дешифраторов, к шине записи информации о дефектных элементах подключен исток другого МДП-транзистора, его затвор соединен с соответствующей каналу ячейкой другого сдвигового регистра, а сток соединен с общей шиной записи информации о дефектных элементах. Ячейка считывания выполнена в составе узла ввода, двух МДП-транзисторов, вход узла ввода, являющийся первым входом рассматриваемой ячейки, предназначен для подачи фотосигналов и соединен с фотоприемником, выход узла ввода электрически соединен с истоком МДП-транзистора, сток которого, являющийся первым выходом рассматриваемой ячейки, соединен с шиной передачи фотосигналов, а затвор - со стоком второго МДП-транзистора, при этом исток второго МДП-транзистора, являющийся вторым входом рассматриваемой ячейки, соединен с шиной передачи информации о дефектных элементах, а затвор, являющийся вторым выходом рассматриваемой ячейки, соединен с соответствующей ячейкой первою дешифратора. Ячейка хранения и суммирования сигналов с ВЗН выполнена в составе ячейки сумматора, в котором количество ячеек равно количеству ВЗН каскадов, двух МДП-транзисторов, исток первого МДП-транзистора соединен с входом ячейки сумматора, его сток, являющийся первым входом рассматриваемой ячейки, соединен с шиной передачи фотосигналов, а затвор, являющийся вторым входом рассматриваемой ячейки, соединен с соответствующей ячейкой второго дешифратора, сток второго МДП-транзистора соединен с выходом ячейки сумматора, его исток, являющийся первым выходом рассматриваемой ячейки, соединен с шиной ВЗН сигналов, а затвор, являющийся вторым выходом рассматриваемой ячейки, соединен с соответствующей ячейкой третьего дешифратора. Ячейка записи и хранения информации о дефектных элементах выполнена в составе ячейки ОЗУ, в котором количество ячеек равно количеству ВЗН каскадов, двух МДП-транзисторов, сток первого МДП-транзистора соединен с входом ячейки ОЗУ, его исток, являющийся первым входом рассматриваемой ячейки, соединен с шиной записи информации о дефектных элементах, а затвор, являющийся вторым входом рассматриваемой ячейки, соединен с затвором второго МДП-транзистора ячейки хранения и суммирования сигналов с ВЗН, являющимся вторым выходом ячейки хранения и суммирования сигналов с ВЗН и соединенным с соответствующей ячейкой третьего дешифратора, исток второго МДП-транзистора рассматриваемой ячейки соединен с выходом ячейки ОЗУ его сток, являющийся первым выходом рассматриваемой ячейки, соединен с шиной передачи информации о дефектных элементах, а затвор, являющийся вторым выходом рассматриваемой ячейки, соединен с затвором второго МДП-транзистора ячейки считывания, являющимся вторым выходом ячейки считывания и соединенным с соответствующей ячейкой первого дешифратора. Узел ввода выполнен в виде предусилителя. Шины выполнены с возможностью передачи сигналов в аналоговой форме.

Организация удаления из ВЗН сигналов фотосигналов дефектных фотоприемных каналов включает следующее.

Если в ячейке ОЗУ записана «логическая 1», то при появлении напряжения на выходах соответствующих ячеек первого и третьего дешифраторов на затвор первого МДП-транзистора ячейки считывания поступает высокое напряжение, фотосигнал с соответствующего фотоприемного канала поступает в аналоговом виде на шину передачи фотосигналов. Если в ячейке ОЗУ записан «логический 0», то на затвор первого МДП-транзистора подается низкое напряжение и происходит блокирование передачи фотосигнала дефектного фотоприемного канала на шину передачи фотосигналов.

В приведенном ближайшем аналоге к недостаткам относится, во-первых, ограничение уровня чувствительности фотоприемного устройства при использовании данных устройств считывания с временной задержкой и накоплением сигналов с многоэлементных фотоприемников, во-вторых, невозможность расширения динамического диапазона - соответственно, ограничение динамического диапазона, в-третьих, ограничение количества фоточувствительных элементов фогоприемника, с которых возможно считывание сигналов каждым каналом.

Недостатки возникают из-за разброса параметров транзисторов, составляющих аналоговые тракты, а также наличия электромагнитной интерференции проводников, по которым из устройства выводится полезный аналоговый сигнал для последующей обработки, обуславливают ограничение по динамическому диапазону.

В ближайшем аналоге используется ВЗН в аналоговой форме, что препятствует достижению возможности считывания каждым каналом сигналов с неограниченного количества фоточувствительных элементов фотоприемника.

Техническим результатом является:

- снятие ограничения чувствительности фотоприемного устройства;

- расширение динамического диапазона;

- достижение возможности считывания каждым каналом сигналов практически с неограниченного количества фоточувствительных элементов фотоприемника.

Технический результат достигается в устройстве считывания с временной задержкой и накоплением (ВЗН) сигналов с многоэлементных фотоприемников инфракрасного излучения, содержащем многоканальную систему считывания в составе m каналов считывания, при этом каждый из m каналов считывания выполнен из блока считывания с n ячейками считывания, блока каскадов ВЗН сигналов с n каскадами ВЗН сигналов, кроме того, каждый канал считывания снабжен k-разрядным сдвиговым регистром, k - число разрядов распределенного аналого-цифрового преобразователя, блок считывания соединен N разрядной шиной сигналов сравнения напряжений с блоком каскадов ВЗН, при этом каждая n-тая ячейка считывания соединена с соответствующим N-тым разрядом N разрядной шины сигналов сравнения напряжений, с соответствием номера ячейки считывания номеру разряда указанной шины, каждая ячейка считывания выполнена в составе интегрирующего усилителя, ячейки выборки и хранения, компаратора, триггера-защелки, логического элемента «И», имеющих по два входа и одному выходу, при этом аналоговые элементы - интегрирующий усилитель, ячейка выборки и хранения, компаратор последовательно соединены в указанной последовательности относительно одного из входов каждого аналоговыми шинами, один из входов интегрирующего усилителя предназначен для соединения с фотоприемником, выход компаратора соединен с инвертирующим входом логического элемента «И», второй вход логического элемента «И» соединен с выходом триггера-защелки, выход логического элемента «И», являющийся выходом ячейки считывания соединен с соответствующим разрядом N разрядной шины сигналов сравнения напряжений, с соответствием номера ячейки считывания номеру разряда, указанной шины, второй вход интегрирующего усилителя соединен с шиной разрешения интегрирования, второй вход ячейки выборки и хранения соединен с шиной разрешения выборки, второй вход компаратора соединен с шиной пилообразного сигнала, один из входов триггера-защелки соединен с соответствующим разрядом M разрядной шины выборки канала считывания, с соответствием номера канала считывания номеру разряда указанной шины, второй вход его соединен с соответствующим разрядом N разрядной шины данных включения/выключения ячейки считывания, с соответствием номера ячейки считывания номеру разряда указанной типы, каждый каскад ВЗН выполнен в составе параметрического мультиплексора сигналом сравнения, логического элемента «И», k-разрядного счетчика, k-разрядного элемента с тремя состояниями на выходе, дополнительного k-разрядного сдвигового регистра, параметрический мультиплексор сигналов сравнения, логический элемент «И», k-разрядный счетчик, k-разрядный элемент с тремя состояниями на выходе, последовательно соединены в указанной последовательности, первый, N разрядный, вход параметрического мультиплексора соединен с N разрядной шиной сигналов сравнения напряжений, второй, N разрядный, вход соединен с N разрядной шиной текущей фазы ВЗН, третий вход соединен с шиной разрешения счета счетчиков каскадов ВЗН и пилообразного сигнала, выход параметрического мультиплексора сигналов сравнения соединен шиной разрешения счета с первым входом логического элемента «И», второй вход логического элемента «И» соединен с шиной синхронизации счетчиков каскадов ВЗН и пилообразного сигнала, выход логического элемента «И» соединен со входом k-разрядного счетчика, k-разрядный выход счетчика соединен К разрядной шиной текущею состояния счетчика с первым, k-разрядным входом, k-разрядного элемента с тремя состояниями на выходе, второй вход которого соединен с выходом дополнительного k-разрядного сдвигового регистра, первый вход дополнительного k-разрядного сдвигового регистра соединен с соответствующим N-тым разрядом N разрядной шины текущей фазы ВЗН, с соответствием номера каскада ВЗН номеру разряда указанной шины, а второй вход - с шиной разрешения параллельной загрузки в сдвиговые регистры каналов считывания, выход k-разрядного элемента с тремя состояниями на выходе, являющийся выходом каскада ВЗН, соединен К разрядной шиной считывания данных из канала считывания с первым входом k-разрядного сдвигового регистра канала считывания, второй вход которого соединен с шиной разрешения параллельной загрузки в сдвиговые регистры каналов считывания, третий вход - с шиной синхронизации считывания данных устройства, а четвертый вход k-разрядного сдвигового регистра первого канала считывания выполнен с возможностью подачи сигнала «логический ноль», четвертый вход k-разрядного сдвигового регистра в других каналах считывания выполнен с возможностью подачи сигнала с выхода k-разрядного сдвигового регистра предыдущего канала считывания, выход k-разрядного сдвигового регистра каждого канала считывания соединен шиной передачи данных сдвиговых регистров каналов считывания в направлении увеличения номера канала считывания с четвертым входом k-разрядного сдвигового регистра следующего по номеру канала считывания, выход m-того канала считывания соединен с шиной выходных данных устройства.

Устройство считывания снабжено генератором пилообразного напряжения, один вход которого соединен с шиной разрешения счета счетчиков каскадов ВЗН и пилообразного сигнала, второй вход соединен с шиной синхронизации счетчиков каскадов ВЗН и пилообразного сигнала, а выход соединен с шиной пилообразного сигнала.

Устройство считывания выполнено на полупроводниковой подложке.

В устройстве считывания ячейка выборки и хранения выполнена в составе емкости и полевого транзистора, исток которого соединен аналоговой шиной с выходом интегрирующего усилителя, сток соединен с одной обкладкой емкости, и с аналоговой шиной, соединенной с входом компаратора, затвор соединен с шиной разрешения выборки, вторая обкладка емкости соединена с общей точкой полупроводниковой подложки, на которой выполнено устройство.

В устройстве считывания параметрический мультиплексор сигналов сравнения выполнен с возможностью реализации его логической функции, определенной формулой:

Ri=E∧[ P1∧I((N+i-1)mod N)+1

∨ P2∧I((N+i-2)modN)+1

∨ P3∧I((N+i-3)modN)+1

∨ …

∨ PN∧I(imodN)+1],

где Ri - выходное значение мультиплексора с параметром IDX, равным i,

E - разрешение счета, подано на третий вход мультиплексора;

{P1, … PN} - вектор значений, определяющих текущую фазу ВЗН, поданный на второй вход мультиплексора;

{I1, … IN} - вектор значений результатов сравнения, поданный на первый вход мультиплексора.

В устройстве считывания, в блоке считывания с n ячейками считывания, блоке каскадов ВЗН сигналов с n каскадами ВЗН сигналов n равно 4, соответственно, в N разрядных шинах - N-разрядная шина сигналов сравнения напряжений, N-разрядная тина текущей фазы ВЗН, N равно 4.

В устройстве считывания параметрический мультиплексор сигналов сравнения реализован на полевых транзисторах, при этом в параметрическом мультиплексоре сигналов сравнения с параметром IDX=1 исток первого транзистора соединен со вторым разрядом N-разрядной шины сигналов сравнения напряжений, его затвор соединен с четвертым разрядом N-разрядной шины текущей фазы, исток второго транзистора соединен с третьим разрядом N-разрядной шины сигналов сравнения напряжений, его затвор соединен с третьим разрядом N-разрядной шины текущей фазы, исток третьего транзистора соединен с четвертым разрядом N-разрядной шины сигналов сравнения напряжений, его затвор соединен со вторым разрядом N-разрядной шины текущей фазы, исток четвертого транзистора соединен с первым разрядом N-разрядной шины сигналов сравнения напряжений, его затвор соединен с первым разрядом N-разрядной шины текущей фазы, стоки перечисленных транзисторов соединены, исток пятого транзистора соединен со стоками первого, второго, третьего и четвертого транзисторов, затвор пятого транзистора соединен с шиной разрешения счета счетчиков каскадов ВЗН и пилообразного сигнала, а его сток соединен с шиной разрешения счета, в параметрическом мультиплексоре сигналов сравнения с параметром IDX=2 исток первого транзистора соединен с третьим разрядом N-разрядной шины сигналов сравнения напряжений, его затвор соединен с четвертым разрядом N-разрядной шины текущей фазы, исток второго транзистора соединен с четвертым разрядом N-разрядной шины сигналов сравнения напряжений, его затвор соединен с третьим разрядом N-разрядной шины текущей фазы, исток третьего транзистора соединен с первым разрядом N-разрядной шины сигналов сравнения напряжений, его затвор соединен со вторым разрядом N-разрядной шины текущей фазы, исток четвертого транзистора соединен со вторым разрядом N-разрядной шины сигналов сравнения напряжений, его затвор соединен с первым разрядом N-разрядной шины текущей фазы, стоки перечисленных транзисторов соединены, исток пятого транзистора соединен со стоками первого, второго, третьего и четвертого транзисторов, затвор пятого транзистора соединен с шиной разрешения счета счетчиков каскадов ВЗН и пилообразного сигнала, а его сток соединен с шиной разрешения счета, в параметрическом мультиплексоре сигналов сравнения с параметром IDX=3 исток первого транзистора соединен с четвертым разрядом N-разрядной шины сигналов сравнения напряжений, его затвор соединен с четвертым разрядом N-разрядной шины текущей фазы, исток второго транзистора соединен с первым разрядом N-разрядной шины сигналов сравнения напряжений, его затвор соединен с третьим разрядом N-разрядной шины текущей фазы, исток третьего транзистора соединен со вторым разрядом N-разрядной шины сигналов сравнения напряжений, его затвор соединен со вторым разрядом N-разрядной шины текущей фазы, исток четвертого транзистора соединен с третьим разрядом N-разрядной шины сигналов сравнения напряжений, его затвор соединен с первым разрядом N-разрядной шины текущей фазы, стоки перечисленных транзисторов соединены, исток пятого транзистора соединен со стоками первого, второго, третьего и четвертого транзисторов, затвор пятого транзистора соединен с тиной разрешения счета счетчиков каскадов ВЗН и пилообразного сигнала, а его сток соединен с шиной разрешения счета, в параметрическом мультиплексоре сигналов сравнения с параметром IDX=4 исток первого транзистора соединен с первым разрядом N-разрядной шины сигналов сравнения напряжений, его затвор соединен с четвертым разрядом N-разрядной шины текущей фазы, исток второго транзистора соединен со вторым разрядом N-разрядной шины сигналов сравнения напряжений, его затвор соединен с третьим разрядом N-разрядной шины текущей фазы, исток третьего транзистора соединен с третьим разрядом N-разрядной шины сигналов сравнения напряжений, его затвор соединен со вторым разрядом N-разрядной шины текущей фазы, исток четвертого транзистора соединен с четвертым разрядом N-разрядной шины сигналов сравнения напряжений, его затвор соединен с первым разрядом N-разрядной шины текущей фазы, стоки перечисленных транзисторов соединены, исток пятого транзистора соединен со стоками первого, второго, третьего и четвертого транзисторов, затвор пятого транзистора соединен с шиной разрешения счета счетчиков каскадов ВЗН и пилообразного сигнала, а его сток соединен с шиной разрешения счета.

Сущность технического решения поясняется нижеследующим описанием и прилагаемыми фигурами.

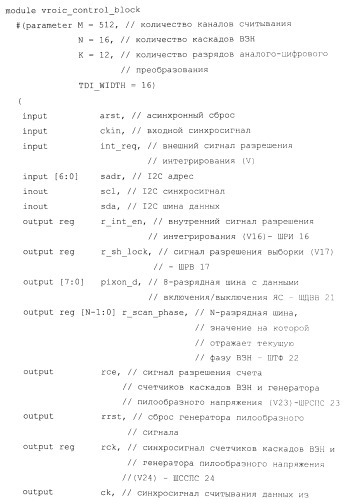

На Фиг.1 представлена схема m канального устройства считывания с ВЗН, кроме непосредственно устройства на схеме показан генератор пилообразного напряжения, где 1 - канал считывания (КС); 2 - ячейка считывания (ЯС); 3 - каскад ВЗН; 4 -интегрирующий усилитель (ИУ); 5 - ячейка выборки и хранения (ЯВХ); 6 - компаратор; 7 - триггер-защелка; 8 - логический элемент «И» (ЛЭ«И»); 9 - параметрический мультиплексор сигналов сравнения (ПМСС); 10 - логический элемент «И» (ЛЭ«И»); 11 - k-разрядный счетчик; 12 - k-разрядный элемент с тремя состояниями на выходе (k-разрядный элемент); 13 - k-разрядный сдвиговый регистр (СР); 14 - генератор пилообразного напряжения (ГПН); 15 - N-разрядная шина сигналов сравнения напряжений (ШССН); 16 - шина разрешения интегрирования (ШРИ); 17 - шина разрешения выборки (ШРВ); 18 - шина пилообразного сигнала (ШПС); 19 - шина разрешения счета (ШРС); 20 - K-разрядная шина текущего состояния счетчика (ШТСС); 21 - N-разрядная шина данных включения/выключения ячейки считывания (ШДВВ); 22 - N-разрядная шина текущей фазы ВЗН (ШТФ); 23 - шина разрешения счета счетчиков каскадов ВЗН и пилообразного сигнала (ШРСПС); 24 - шина синхронизации счетчиков каскадов ВЗН и пилообразного сигнала (ШССПС); 25 - шина синхронизации считывания данных устройства (ШССД); 26 - шина разрешения параллельной загрузки в сдвиговые регистры каналов считывания (ШРПЗ); 27 - K-разрядная шина считывания данных из канала считывания (ШСД); 28 - шина передачи данных сдвиговых регистров каналов считывания в направлении увеличения номера канала считывания (ШПД); 29 - шина выходных данных устройства (ШВД); 30 - M-разрядная шина выборки канала считывания для записи данных включения/выключения ячейки считывания (ШВКС).

На Фиг.2 приведена принципиальная схема одной из возможных реализации ячейки выборки и хранения ячейки считывания, где VT - транзистор; C - емкость; 17 - шина разрешения выборки (ШРВ); 31 и 32 - аналоговые шины.

На Фиг 3 представлены принципиальные схемы возможных реализации параметрического мультиплексора сигналов сравнения с параметром IDX=1 (A), с параметром IDX=2 (Б), с параметром IDX=3 (В), параметром IDX=4 (Г), при количестве каскадов ВЗН N=4, где 15.1, 15.2, 15.3 и 15.4 - 1, 2, 3 и 4 разряды N-разрядной шины сигналов сравнения напряжений, соответственно; 19 - шина разрешения счета; 22.1, 22.2, 22.3 и 22.4 - 1, 2, 3 и 4 разряды N-разрядной шины текущей фазы ВЗН, соответственно; 23 - шина разрешения счета счетчиков каскадов ВЗН и пилообразного сигнала (ШРСПС); VT1-VT5 - полевые транзисторы.

На Фиг.4 представлены временные диаграммы управляющих напряжений при прямом направлении сканирования в случае количества каскадов ВЗН N=4 в каждом канале считывания, где V16 - напряжение шины разрешения интегрирования, V17 - напряжение шины разрешения выборки; V18 - напряжение шины пилообразного сигнала; V19.1, V19.2, V19.3 и V19.4 - напряжения сигналов разрешения счета, соответственно, на шинах разрешения счета 1, 2, 3 и 4 каскадов ВЗН канала считывания; V22.1, V22.2, V22.3 и V22.4 - напряжения, соответственно, 1, 2, 3 и 4 разрядов N-разрядной шины текущей фазы ВЗН; V23 - напряжение шины разрешения счета счетчиков каскадов ВЗН и пилообразного сигнала; V26 - напряжение шины разрешения параллельной загрузки в сдвиговые регистры каналов считывания; V29 - напряжение шины выходных данных устройства; V - напряжение внешнего сигнала разрешения интегрирования.

На Фиг.5 представлены временные диаграммы управляющих напряжений при прямом направлении сканирования, во время второй фазы ВЗН (сигнал V22.2 принимает значение «логической 1»), в течение времени одного акта интегрирования фотосигнала и аналого-цифрового преобразования, в случае количества каскадов ВЗН N=4 в каждом канале считывания: временная диаграмма в начале акта интегрирования и аналогово-цифрового преобразования (диапазон А); временная диаграмма в конце акта аналогово-цифрового преобразования (диапазон Б); временная диаграмма в конце акта интегрирования (диапазон В); где V16 - напряжение шины разрешения интегрирования; V17 - напряжение шины разрешения выборки; V18 - напряжение шины пилообразного сигнала; V19.1, V19.2, V19.3 и V19.4 - напряжения сигналов разрешения счета, соответственно, на шинах разрешения счета 1, 2, 3 и 4 каскадов ВЗН канала считывания; V20.1, V20.2, V20.3 и V20.4 - напряжения сигналов текущего состояния счетчика, соответственно, на 1, 2, 3 и 4 каскадах ВЗН канала считывания; V22.1, V22.2, V22.3 и V22.4 - напряжения, соответственно, 1, 2, 3 и 4 разрядов N-разрядной шины текущей фазы ВЗН, V23 напряжение шины разрешения счета счетчиков каскадов ВЗН и пилообразного сигнала; V24 - напряжение шины синхронизации счетчиков каскадов ВЗН и пилообразного сигнала; V25 - напряжение шины синхронизации считывания данных устройства; V26 -напряжение шины разрешения параллельной загрузки в сдвиговые регистры каналов считывания; V27 - напряжение шины считывания данных из канала считывания; V29 - напряжение шины выходных данных устройства; V - напряжение внешнего сигнала разрешения интегрирования.

Достижение технического результата в предлагаемом техническом решении (см. Фиг.1) базируется на использовании аналого-цифрового преобразования и на конструктивном выполнении устройства считывания, при котором устройство комплектуется с подразделением на аналоговую и цифровую части. В аналоговой части отсутствуют какие-либо цифровые элементы, которые бы изменяли свое состояние в процессе интегрирования и аналого-цифрового преобразования сигнала. В цифровой части отсутствуют какие-либо аналоговые элементы. Элементы, обрабатывающие фотосигнал в аналоговой форме, сосредоточены во входной части каждого m-того канала считывания (КС) 1, а именно, во входной части каждой n-той ячейки считывания (ЯС) 2 m-того канала считывания (КС) 1, в которой начинается обработка считываемого ей: нала с фотоприемника. Такими элементами являются: интегрирующий усилитель (ИУ) 4, ячейка выборки и хранения (ЯВХ) 5, компаратор 6. Входная часть ячейки считывания (ЯС) 2, сформированная указанными элементами, соединена непосредственно с фотоприемником, в частности, с контактной площадкой для соединения фотоприемника с устройством считывания. Подразделение устройства на аналоговую и цифровую части с отсутствием в аналоговой части цифровых элементов и линий связи, которые могут изменять свое состояние в течение времени интегрирования аналогового сигнала позволяет исключить внесение дополнительных шумов в полезный сигнал. В результате локализации аналоговых элементов устройства считывания во входной части существенно ослабляется взаимная интерференция между аналоговыми сигналами соседних ячеек устройства.

В устройстве считывания реализован распределенный аналого-цифровой преобразователь. В отличие от приведенных известных технических решений на выходе ячеек считывания присутствует сигнал не в аналоговой, а в цифровой форме. Преобразование фотосигнала в цифровую форму происходит в ячейке считывания (ЯС) 2. Сигнал в цифровой форме поступает в каскад ВЗН 3, и далее, его обработка осуществляется в цифровой форме. Применение ВЗН в цифровой форме позволяет реализовать каждый канал считывания (КС) 1 практически в отношении неограниченною числа фоточувствительных элементов фотоприемника. Таким образом, за счет распределенного по ячейкам считывания аналого-цифрового преобразователя снимаются ограничения, обусловленные применением ВЗН в аналоговой форме.

Устройство считывания с временной задержкой и накоплением (ВЗН) сигналов с многоэлементных фотоприемников инфракрасного излучения выполнено на полупроводниковой подложке.

В общем случае выполнения устройство считывания с временной задержкой и накоплением (ВЗН) сигналов с многоэлементных фотоприемников инфракрасного излучения содержит многоканальную систему считывания в составе m каналов считывания (КС) 1, каждый канал выполнен из блока считывания с n ячейками считывания (ЯС) 2, блока каскадов ВЗН сигналов с n каскадами ВЗН 3 сигналов и снабжен k-разрядным сдвиговым регистром (СР) 13, k - число разрядов распределенного аналого-цифрового преобразователя (см. Фиг.1). Блок считывания соединен N разрядной шиной сигналов сравнения напряжений (ШССН) 15 с блоком каскадов ВЗН. При этом каждая n-тая ячейка считывания (ЯС) 2 соединена с соответствующим N-тым разрядом N разрядной шины сигналов сравнения напряжений (ШССН) 15, с соответствием номера ячейки считывания (ЯС) 2 номеру разряда указанной шины.

Ячейка считывания (ЯС) 2 выполнена в составе интегрирующего усилителя (ИУ) 4, ячейки выборки и хранения (ЯВХ) 5, компаратора 6, триггера-защелки 7, логическою элемента «И» (ЛЭ«И») 8, каждый из которых имеет по два входа и одному выходу (см. Фиг.1). В ЯС