Способ организации выполнения операции умножения двух чисел в модулярно-позиционном формате представления с плавающей точкой на универсальных многоядерных процессорах

Иллюстрации

Показать всеИзобретение относится к вычислительной технике и может быть использовано для выполнения операции умножения чисел, представленных в модулярно-позиционном формате с плавающей точкой на универсальных многоядерных процессорах. Техническим результатом является повышение скорости вычисления за счет замены операции умножения t-разрядных позиционных мантисс сомножителей n параллельно выполняемыми операциями умножения q-разрядных знакопозиций чисел в системе счисления в остаточных классах. Способ реализуется на универсальном многоядерном вычислителе, содержащем g k-разрядных вычислительных ядер, каждое из которых обеспечивает выполнение системы из f операций, в состав которых входят операции алгебраического умножения и алгебраического сложения над числами, представленными в позиционных целочисленных форматах данных. При организации выполнения операций умножения каждое число, множитель и множимое, представляется в модулярно-позиционном формате с плавающей точкой в виде (1+k+q·n) - элементного вектора.

Реферат

Изобретение относится к вычислительной технике и предназначено для выполнения операции умножения чисел, представленных в модулярно-позиционном формате с плавающей точкой на универсальных многоядерных процессорах.

Известен итерационный способ умножения чисел, представленных в одном из позиционных двоичных форматов с плавающей точкой, определенных стандартом IEEE-754. В этом способе умножение состоит из последовательности сложений с накоплением мантисс сомножителей, которые выполняются последовательно, сложения порядков и сложения по модулю два знаков сомножителей. Последовательность сложений с накоплением мантисс сомножителей выполняется следующим образом. При сдвигах мантиссы множителя освободившиеся разряды заполняются нулями. Если первый бит t-разрядной позиционной мантиссы множителя равен единице, то первое слагаемое является мантиссой множимого, иначе первое слагаемое равно нулю. Если второй бит мантиссы множителя равен единице, то второе слагаемое является мантиссой множимого, сдвинутой на один разряд влево, иначе второе слагаемое равно нулю. К сумме первого и второго слагаемого прибавляется мантисса множимого, сдвинутая на два разряда влево, если второй бит мантиссы множителя равен единице, иначе прибавляется нуль. Затем к полученной сумме прибавляется мантисса множимого, сдвинутая на три разряда влево, если третий бит мантиссы множителя равен единице, иначе прибавляется нуль. И так далее до t-го разряда мантиссы множителя, к накопленной сумме прибавляется мантисса множимого, сдвинутая на v разрядов влево, если t-ый бит мантиссы множителя равен единице, иначе прибавляется нуль. В итоге накопленная сумма является искомым произведением мантисс сомножителей. Далее выполняется сложение смещенных позиционных порядков сомножителей, тем самым получается порядок результата. Знак результата определяется сложением по модулю два знаков сомножителей.

Недостаток итерационного способа умножения позиционных двоичных чисел с плавающей точкой состоит в том, что, во-первых, при умножении мантисс выполняется t-1 операций суммирования t-разрядных операндов. Если принять, что операция суммирования t-разрядных операндов выполняется за t тактов процессора, то общее время выполнения операции умножения мантисс позиционных операндов с плавающей точкой составит t·(t-1) тактов. Во-вторых, процесс формирования суммы является последовательным процессом.

Техническим результатом применения способа организации выполнения операции умножения двух чисел в модулярно-позиционном формате представления с плавающей точкой на универсальных многоядерных процессорах является повышение скорости вычисления за счет замены операции умножения t-разрядных позиционных мантисс сомножителей n параллельно выполняемыми операциями умножения q-разрядных знакопозиций чисел в системе счисления в остаточных классах, причем q≈t/n. Если принять за время суммирования пары t-разрядных чисел t тактов работы процессора, а за время суммирования пары q-разрядных чисел q тактов работы процессора, то, при условии, что число вычислительных ядер универсального многоядерного процессора не меньше n, а операция умножения q-разрядных чисел может быть выполнена посредством q-1 операции сложения q-разрядных чисел, то предельное ускорение вычислений S составляет: S ≈ t ⋅ ( t − 1 ) q ⋅ ( q − 1 )

Описание способа организации выполнения операции умножения двух чисел в модулярно-позиционном формате представления с плавающей точкой на универсальных многоядерных процессорах: реализация способа осуществляется посредством подачи набора электрических, нейронных либо других сигналов на устройства управления каждого вычислительного ядра многоядерного процессора универсального назначения, которые, в соответствии с данными сигналами, формируют управляющие команды для операционных устройств соответствующих вычислительных ядер.

В позиционных двоичных форматах с плавающей точкой стандарта IEEE-754 любое вещественное число представляется трехэлементным набором:

| [M,e,S|M∈[0,2),е∈[еmin,emax],S∈{0,1}], | (1) |

где М- рациональная мантисса, е - порядок числа, еmin=2-2w-1 и еmax=2w-1-1, s - знак числа.

Величина чисел, записанных в таком формате, выражается формулой -1s·М·2е. Машинными представлениями чисел вида (1) являются (w+t+1) - разрядные двоичные векторы 〈srw…r2r1dt…d2d1〉, где разряды c d1 по dt отводятся под представление рациональных двоичных мантисс М=dt·dt-1…d2d1, разряды с r1, по rw отводятся под представление целочисленных двоичных порядков е, записанных в форме с избытком Е=rwrw-1…r2r1=е+еmax, разряд s выражает знак числа.

Определим целочисленную мантиссу М'=dtdt-1…d2d1 как t-разрядное неотрицательное целое двоичное число, такое что М=М'·21-t. Определим перемещенный порядок λ как целое двоичное число со знаком, такое, что λ=е-t+1, где е-w-разрядный порядок числа, представленного в двоичном формате (1).

Зададим n целочисленных положительных q-разрядных оснований системы остаточных классов Р1,Р2,…,Рn таких, что ∀i1,i2∈{l,2,…,n},i1≠i2:gcd( p i 1 , p i 2 )=1, q<k, где gcd( p i 1 , p i 2 ) - наибольший общий делитель для p i 1 и p i 2 , k - размер разрядной сетки процессора.

Целочисленную мантиссу М'=dtdt-1…d2d1 преобразуем в систему остаточных

классов с заданными основаниями р1,р2,…,рn, получая тем самым модулярную мантиссу M ˜ =〈m1,m2,…,mn〉:

M ˜ = 〈 m 1 , m 2 , … m n 〉 = 〈 | M ' | p 1 , | M ' | p 2 , … , | M ' | p n 〉 ,

где mi∈[0,pi-1], i=1,2,…,n - q-разрядные цифры (модулярные разряды) модулярной мантиссы M ˜ , q - разрядность оснований р1,р2,…,рn, | M ' | p i - операция получения остатка от деления M' на i-ое основание рi.

Таким образом, число с плавающей точкой вида (1) можно преобразовать к следующему модулярно-позиционному формату:

[ 〈 m 1 , m 2 , … m n 〉 , λ , s | , m i ∈ [ 0, p i − 1 ] , λ ∈ [ λ ' min , λ ' max ] , s ∈ { 0,1 } ] . (2)

где (m1,m2,…,mn) - набор знакопозиций (модулярных разрядов) модулярной мантиссы M ˜ , λ - позиционный перемещенный порядок, представляющий собой целое двоичное число со знаком.

Диапазон допустимых значений модулярных мантисс M ˜ =〈m1,m2,…,mn〉 в системе остаточных классов с основаниями р1,р2,…,рn определяется интервалом [ 0, P = ∏ i = 1 n p i ) , таким образом, t-разрядная позиционная мантисса М=d1.dt-1…d2d1 может быть представлена в системе остаточных классов набором из n взаимно независимых q-разрядных знакопозиций 〈m1,m2,…,mn〉, причем q≈t/n (для случая, если все основания р1,р2,…,рn q-разрядные).

Примеры преобразования позиционных чисел с плавающей точкой в модулярно-позиционный формат: пусть числа представлены в 10-разрядном двоичном формате вида (1), в котором под смещенный порядок Е отводится четыре бита (максимальный порядок еmax=24-1-1=7, соответственно е=Е-7), под дробную часть мантиссы - пять бит (т.е. t=6, причем целая часть d6 рациональной мантиссы М в явном виде не записана) и под знак числа - один бит. Пусть для представления модулярных мантисс в модулярно-позиционном формате [〈m1,m2,…,mn〉,λ,s] используется три основания: p1=3=22-1, p2=7=23-1, p3=31=25-l.

Пример 1: необходимо перевести число Х=[1.5,-1,0]=-1°·1.5·2-1, представленное в двоичном формате [М,е,s], в модулярно-позиционный формат [〈m1,m2,…,mn〉,λ,s].

С учетом принятых характеристик двоичного формата [М,е,s], число Х будет записано в памяти ЭВМ в виде двоичного вектора 〈0011010000〉. Для его преобразования в модулярно-позиционный формат (2) необходимо выполнить следующие действия:

1. Выделить составные части числа X: знак числа s=0, дробная часть рациональной мантиссы d5…d2d1=100002, смещенный (избыточный) порядок Е=01102=6.

2. Восстановить целую часть d6 мантиссы M=d6.d5…d2d1: d6=1, т.к. Е>0, следовательно М=1.100002.

3. Определить порядок е: е=Е-еmax=6-7=-1, т.к. Е>0.

4. Определить перемещенный позиционный порядок λ и целочисленную мантиссу M':λ=e-t+1=-1-6+1=-6,M'=d6d5…d2d1=1100002=48.

5. Найти модулярную мантиссу M ˜ =〈m1,m2,m3〉: M ˜ =〈|48|3,|48|7,|48|31〉=〈0,6,17〉.

В результате получается число X, представленное в модулярно-позиционном формате с плавающей точкой: X=[〈0,6,17〉,-6,0]=-10·〈0,6,17〉·2-6.

Пример 2: необходимо перевести число X=[0.625-6,1]=-11·0.625·2-6 из двоичного формата [М,е,s] в модулярно-позиционный формат [〈m1,m2,…,mn〉,λ,s].

С учетом принятых характеристик двоичного формата [М,е,s], число Х будет записано в памяти ЭВМ в виде двоичного вектора 〈1000010100〉. Для его преобразования в модулярно-позиционный формат (2) необходимо выполнить следующие действия:

1. Выделить составные части числа X: знак числа s=1, дробная часть d5…d2d1=101002, смещенный порядок Е=00002=0.

2. Восстановить целую часть d6 мантиссы M=d6·d5…d2d1: d6=0, т.к. Е=0, следовательно М=0.101002.

3. Определить порядок е: е=еmin=2-24-1=-6, т.к. Е=0.

4. Определить перемещенный порядок λ и целочисленную мантиссу М': λ=e-t+1=-6-6+1=-11, M'=d6d5…d2d1=0101002=20.

5. Найти модулярную мантиссу M ˜ =〈m1,m2,m3〉: M ˜ =〈|20|3,|20|7,|20|31〉=(2, 6, 20). В результате получается число X, представленное в модулярно-позиционном формате с плавающей точкой: X=[〈2, 6, 20〉,-11,1]=-11·〈2, 6, 20〉·2-11.

Пусть A=[〈 m 1 A , m 2 A , … m n A 〉],λA,SA], B=[〈 m 1 B , m 2 B , … m n B 〉],λB,SB] - числа, представленные в модулярно-позиционном формате с плавающей точкой, где M ˜ A =[〈 m 1 A , m 2 A , … m n A 〉],λA,SA], M ˜ B =[〈 m 1 B , m 2 B , … m n B 〉],λB,SB] - модулярные мантиссы чисел А и В соответственно. Тогда способ умножения С=А·В чисел А и В, представленных в модулярно-позиционном формате с плавающей точкой (2), на универсальном k-разрядном процессоре, содержащем g вычислительных ядер, определяется следующим образом.

1. Множитель A=[〈 m 1 A , m 2 A , … m n A 〉],λA,SA] и множимое B=[〈 m 1 B , m 2 B , … m n B 〉],λB,SB], представленные в модулярно-позиционном формате с плавающей точкой, загружают в универсальный k-разрядный процессор, содержащий g вычислительных ядер, следующим образом:

1.1. Если число g вычислительных ядер процессора превышает число n оснований р1,р2,…,рn системы остаточных классов, используемых для представления модулярных мантисс M ˜ A =〈 m 1 A , m 2 A , … m n A 〉 и M ˜ B =〈 m 1 B , m 2 B , … m n B 〉 чисел А и В соответственно, то:

- в первое ядро универсального многоядерного процессора загружают q-разрядные двоичные представления первых знакопозиций m 1 A и m 1 B модулярных мантисс M ˜ A =〈 m 1 A , m 2 A , … m n A 〉, и M ˜ B =〈 m 1 B , m 2 B , … m n B 〉 чисел А и В соответственно, а также

основание системы остаточных классов pi, разрядность q которого не превышает размер k разрядной сетки процессора;

- параллельно с этим, во второе ядро универсального многоядерного процессора загружают q-разрядные двоичные представления вторых знакопозиций m 2 A и m 2 B модулярных мантисс M ˜ A и M ˜ B чисел А и В соответственно, а также основание системы остаточных классов р2, разрядность q которого не превышает размер k разрядной сетки процессора; и т.д.;

- параллельно с этим, в n-ое ядро универсального многоядерного процессора загружают q-разрядные двоичные представления n-ых знакопозиций m n A и m n B модулярных мантисс M ˜ A и M ˜ B чисел А и В соответственно, а также основание системы остаточных классов рn, разрядность q которого не превышает размер k разрядной сетки процессора;

- параллельно с этим, в (n+1)-ое ядро универсального многоядерного процессора загружают k-разрядные двоичные порядки λA и λB, а также знаки sA и sB чисел А и В соответственно.

1.2. Если число n оснований p1, p2,…,pn системы остаточных классов используемых для представления модулярных мантисс M ˜ A =〈 m 1 A , m 2 A , … m n A 〉 и M ˜ B =〈 m 1 B , m 2 B , … m n B 〉 равно числу g вычислительных ядер универсального вычислителя, либо превышает его, то:

- q-разрядные двоичные представления первых знакопозиций m 1 A и m 1 B модулярных мантисс M ˜ A и M ˜ B чисел А и В соответственно, а также q-разрядное основание системы остаточных классов р1 загружают в первое ядро универсального многоядерного процессора;

- параллельно с этим, q-разрядные двоичные представления вторых знакопозиций m 2 A и m 2 B модулярных мантисс M ˜ A и M ˜ B чисел А и В соответственно, а также q-разрядное основание системы остаточных классов p2 загружают во второе ядро универсального многоядерного процессора; и т.д.;

- параллельно с этим, q-разрядные двоичные представления (g-1)-ыx знакопозиций m g − 1 A и m g − 1 B модулярных мантисс M ˜ A и M ˜ B чисел А и В соответственно, а также q-разрядное основание системы остаточных классов pg-1 загружают в (g-1)-ое ядро универсального многоядерного процессора;

- q-разрядные двоичные представления g-ых знакопозиций m g A и m g B модулярных мантисс M ˜ A и M ˜ B чисел А и В соответственно, а также q-разрядное основание системы остаточных классов pg загружают в первое ядро универсального многоядерного процессора;

- q-разрядные двоичные представления (g+1)-ыx знакопозиций m g + 1 A и m g + 1 B модулярных мантисс M ˜ A и M ˜ B чисел А и В соответственно, а также q-разрядное основание системы остаточных классов pg+1 загружают во второе ядро универсального многоядерного процессора;

- и т.д., пока не будут загружены n-ые знакопозиций m n A и m n B модулярных мантисс M ˜ A =〈 m 1 A , m 2 A , … m n A 〉 и M ˜ B =〈 m 1 B , m 2 B , … m n B 〉 чисел А и В соответственно;

- параллельно с этим, k-разрядные двоичные порядки λА и λB, а также знаки sA и sB чисел А и В соответственно загружают в g-oe ядро универсального многоядерного процессора.

2. После того как множитель A=[〈 m 1 A , m 2 A , … m n A 〉,λA,SA] и множимое B=[〈 m 1 B , m 2 B , … m n B 〉,λB,SB], представленные в модулярно-позиционном формате с плавающей точкой, загружены в универсальный k-разрядный процессор, содержащий g вычислительных ядер, операция их умножения выполняется следующим образом:

2.1. Если число g вычислительных ядер процессора превышает число n оснований p1,p2,…;pn системы остаточных классов, используемых для представления модулярных мантисс M ˜ A =〈 m 1 A , m 2 A , … m n A 〉 и M ˜ B =〈 m 1 B , m 2 B , … m n B 〉 чисел А и В соответственно, то:

- в первом вычислительном ядре процессора выполняется операция целочисленного умножения m 1 C = | m 1 A ⋅ m 1 B | p 1 по модулю р1 q-разрядных двоичных представлений знакопозиций m 1 A и m 2 B модулярных мантисс M ˜ A =〈 m 1 A , m 2 A , … m n A 〉 и M ˜ B =〈 m 1 B , m 2 B , … m n B 〉 чисел А и В соответственно, путем нахождения значения

m 1 C = | m 1 A ⋅ m 1 B | p 1 = m 1 A ⋅ m 1 B − ⌊ m 1 A ⋅ m 1 B p 1 ⌋ ⋅ p 1 , где ⌊ m 1 A ⋅ m 1 B p 1 ⌋ - наибольшее целое, не превышающее m 1 A ⋅ m 1 B p 1 ; все операции являются целочисленными и выполняются в позиционной двоичной системе счисления;

- параллельно с этим, во втором вычислительном ядре процессора выполняется m 2 C = | m 2 A ⋅ m 2 B | p 2 по модулю р2 q-разрядных двоичных представлений знакопозиций m 2 A и m 2 B модулярных мантисс M ˜ A и M ˜ B чисел А и В соответственно; все операции являются целочисленными и выполняются в позиционной двоичной системе счисления; и т.д.;

- параллельно с этим, в n-ом вычислительном ядре процессора выполняется операция умножения m n C = | m n A ⋅ m n B | p n по модулю рn q-разрядных двоичных представлений знакопозиций m n A и m n B модулярных мантисс M ˜ A и M ˜ B чисел А и В соответственно; все операции являются целочисленными и выполняются в позиционной двоичной системе счисления;

- параллельно с этим, в (n+1)-м вычислительном ядре процессора выполняется сложение двоичных порядков λA и λB, а также сложение по модулю два sC=|sA+sB|2 знаков sA и SB чисел А и В соответственно.

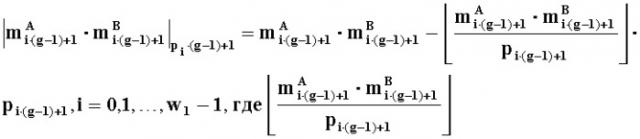

2.2. Если число n оснований р1,p2,…,pn системы остаточных классов используемых для представления модулярных мантисс M ˜ A =〈 m 1 A , m 2 A , … m n A 〉 и M ˜ B =〈 m 1 B , m 2 B , … m n B 〉 равно числу g вычислительных ядер универсального вычислителя, либо превышает его, и в каждое j-oe вычислительное ядро из первых (g-1) вычислительных ядер процессора загружено wj знакопозиций

m i ⋅ ( g − 1 ) + j A и m i ⋅ ( g − 1 ) + j B , i=0,1,…,w1-1, то:

- в первом вычислительном ядре процессора последовательно выполняются операции умножения m i ⋅ ( g − 1 ) + 1 C = | m i ⋅ ( g − 1 ) + 1 A ⋅ m i ⋅ ( g − 1 ) + 1 B | p i ⋅ ( g − 1 ) + 1 по модулям pi·(g-1)+1, i=0,1,…,w1-1, g-разрядньгх двоичных представлений всех w1 загруженных в него знакопозиций m i ⋅ ( g − 1 ) + 1 A и m i ⋅ ( g − 1 ) + 1 B , i=0,1,…,w1-1 модулярных мантисс M ˜ A =〈 m 1 A , m 2 A , … m n A 〉 и M ˜ B =〈 m 1 B , m 2 B , … m n B 〉 чисел А и В соответственно, путем нахождения значений | m i ⋅ ( g − 1 ) + 1 A ⋅ m i ⋅ ( g − 1 ) + 1 B | p i ⋅ ( g − 1 ) + 1 = m i ⋅ ( g − 1 ) + 1 A ⋅ m i ⋅ ( g − 1 ) + 1 B − ⌊ m i ⋅ ( g − 1 ) + 1 A ⋅ m i ⋅ ( g − 1 ) + 1 B p i ⋅ ( g − 1 ) + 1 ⌋ ⋅ p i ⋅ ( g − 1 ) + 1 , i = 0,1, … , w 1 − 1, г д е ⌊ m i ⋅