Князьков Владимир Сергеевич (RU)

Изобретатель Князьков Владимир Сергеевич (RU) является автором следующих патентов:

Способ установки узла усиления

Изобретение относится к строительству, а именно к усилениям строительных конструкций. Достигаемый технический результат заключается в обеспечении надежности и безопасности конструкции. Способ установки узла усиления в виде накладной сборной из уголков и планок стальной обоймы на строительной конструкции типа колонны, заключающийся в размещении обоймы на постели из бетона или раствора, создании тре...

2282701

Ячейка однородной вычислительной среды

Изобретение относится к вычислительной технике и может быть использовано для построения однородных вычислительных структур, выполняющих функцию счетчика, с представлением результата в унитарном или двоичном коде и для применения в устройстве для сжатия двоичных векторов. Техническим результатом является повышение функциональных возможностей ячейки за счет введения операции подсчета числа единиц с...

2284568

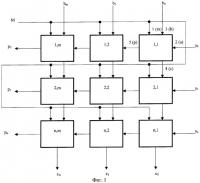

Ячейка однородной структуры

Изобретение относится к вычислительной технике и может быть использовано для построения однородных вычислительных структур, выполняющих арифметическое сложение двоичных векторов, упорядоченное хранение и трансляцию информации при массовой параллельной обработке данных. Техническим результатом является повышение функциональных возможностей ячейки за счет реализации операции арифметического сложения...

2285285

Ячейка однородной структуры

Изобретение относится к вычислительной технике и может быть использовано для построения однородных вычислительных структур, выполняющих параллельную логическую и арифметическую обработку данных. Техническим результатом является расширение функциональных возможностей устройства за счет реализации операции хранения и обработки информации в непозиционной системе счисления. Устройство содержит семь эл...

2295147

Ячейка однородной структуры

Изобретение относится к вычислительной технике и может быть использовано для построения однородных вычислительных структур, выполняющих параллельную логическую и арифметическую обработку данных. Техническим результатом является расширение функциональных возможностей устройства за счет реализации операции хранения и обработки информации в непозиционной системе счисления. Устройство содержит шесть э...

2300800

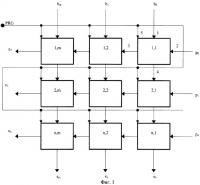

Однородная вычислительная структура для выполнения операций по заданному модулю

Изобретение относится к вычислительной технике и может быть использовано для выполнения арифметических операций над числами, представленными в непозиционной модулярной системе счисления. Техническим результатом является повышение функциональных возможностей устройства. Устройство содержит N2 полных сумматоров, элементов И, где K=N-1, (N-2)(N-1) элементов ИЛИ, управляющих входов. 3 ил.

2310223

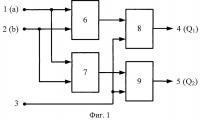

Ячейка однородной вычислительной среды и устройство для сжатия двоичных векторов на базе ячеек однородной вычислительной среды

Изобретение относится к вычислительной технике и предназначено для построения однородных вычислительных сред, выполняющих сжатие массивов двоичных векторов в конвейерном режиме. Техническим результатом является повышение надежности однородной вычислительной среды за счет сокращения числа связей между ячейками однородной вычислительной среды и повышение быстродействия за счет использования более б...

2450327

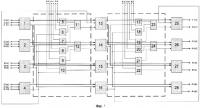

Ячейка однородной вычислительной среды, однородная вычислительная среда и устройство для конвейерных вычислений суммы м n-разрядных чисел

Изобретения относятся к вычислительной технике и могут быть использованы при построении быстродействующих арифметических устройств ЭВМ на базе однородных вычислительных сред. Техническим результатом является повышение быстродействия и надежности. Ячейка однородной вычислительной среды содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент И, два триггера. 3 н.п. ф-лы, 8 ил., 1 табл.

2475815

Ячейка однородной вычислительной среды, однородная вычислительная среда и устройство для конвейерных арифметических вычислений по заданному модулю

Изобретения относятся к вычислительной технике и могут быть использованы для построения однородных вычислительных сред, выполняющих арифметические операции над парами двоичных векторов по заданному модулю. Техническим результатом является повышение быстродействия и надежности. Ячейка однородной вычислительной среды содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент И, два триггера. 3 н.п. ф-лы, 6 ил., 3 т...

2477513

Способ организации умножения чисел с плавающей запятой, представленных в системе остаточных классов

Изобретение относится к вычислительной технике и предназначено для построения быстродействующих параллельно-конвейерных умножителей. Техническим результатом является повышение скорости вычисления. Способ содержит этапы, на которых осуществляют параллельную запись остатка по основанию pi множимого в элементы памяти матрицы i-го умножителя, параллельно выполняют подсчет количества единиц bi в кажд...

2485574

Однородная вычислительная среда для конвейерных вычислений суммы m n-разрядных чисел

Изобретение относится к вычислительной технике и предназначено для построения быстродействующих многооперандных параллельно-конвейерных сумматоров для обработки массивов целых положительных чисел. Техническим результатом является повышение быстродействия за счет параллельно-конвейерного выделения бит переносов разрядного среза слагаемых в следующий разрядный срез и формирования разрядов искомой...

2486576

Способ организации вычислений суммы n m-разрядных чисел

Изобретение относится к вычислительной технике и предназначено для построения быстродействующих многооперандных параллельно-конвейерных сумматоров, для обработки массивов целых положительных чисел. Техническим результатом является повышение скорости вычисления. Способ содержит этапы, на которых параллельно подсчитывают количество единиц bi (i=1, m) в m n-разрядных двоичных векторах, сдвигают дво...

2491612

Способ деления целых двоичных чисел без остатка начиная с младших разрядов

Изобретение относится к вычислительной технике и предназначено для построения быстродействующих параллельно-конвейерных делителей, обрабатывающих массивы положительных целых чисел. Техническим результатом является повышение скорости вычисления. Способ содержит этапы, на которых происходит параллельная запись делителя в ячейки матрицы на элементах памяти, первый разряд частного становится равным...

2498393

Способ организации умножения чисел с плавающей запятой, представленных в системе остаточных классов

Изобретение относится к вычислительной технике и предназначено для построения быстродействующих параллельно-конвейерных умножителей. Техническим результатом является повышение скорости вычисления. Способ содержит этапы: осуществляют параллельную запись остатка по основанию p1 множимого в элементы памяти, параллельно выполняют подсчет количества единиц bi в каждом столбце i-ой матрицы, сдвигают д...

2500018

Устройство для выравнивания порядков m двоичных чисел

Изобретение относится к вычислительной технике и предназначено для построения однородных вычислительных сред, выполняющих функцию выравнивания порядков двоичных чисел. Техническим результатом является повышение быстродействия за счет параллельно-конвейерного нахождения максимального порядка с помощью анализа разрядных срезов операндов, а затем вычисления разностей максимального порядка и остальн...

2503991

Способ организации выполнения операции умножения двух чисел в модулярно-позиционном формате представления с плавающей точкой на универсальных многоядерных процессорах

Изобретение относится к вычислительной технике и может быть использовано для выполнения операции умножения чисел, представленных в модулярно-позиционном формате с плавающей точкой на универсальных многоядерных процессорах. Техническим результатом является повышение скорости вычисления за счет замены операции умножения t-разрядных позиционных мантисс сомножителей n параллельно выполняемыми операц...

2509345

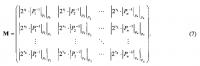

Устройство для сравнения чисел в системе остаточных классов на основе интервально-позиционных характеристик

Изобретение относится к вычислительной технике и предназначено для выполнения операции сравнения двух чисел, представленных в системе остаточных классов. Техническим результатом является повышение быстродействия и обеспечение контроля корректности результата операции сравнения. Представленные положения обеспечиваются за счет использования новой интервально-позиционной характеристики модулярной а...

2557444

Устройство для определения знаков чисел в системе остаточных классов

Изобретение относится к вычислительной технике и предназначено для выполнения операции определения знака числа, представленного в системе остаточных классов. Техническим результатом является повышение быстродействия и обеспечение контроля корректности определения знака. Устройство содержит группу входных регистров для хранения числа, представленного в коде симметричной системы остаточных классов...

2557446

Способ организации параллельно-конвейерных вычислений в однородной вычислительной среде с коммутационно-потоковым управлением

Изобретение относится к вычислительной технике и предназначено для построения быстродействующих многооперандных параллельно-конвейерных сумматоров для обработки массивов целых положительных чисел. Техническим результатом является повышение быстродействия. Ячейки каждой подобласти однородной вычислительной среды настраивают на выполнение уникальной операции, где m - общее количество операций. Исх...

2558613

Способ организации выполнения операции умножения двух чисел в модулярно-индексном формате представления с плавающей точкой на универсальных многоядерных процессорах

Изобретение относится к средствам для выполнения операции умножения чисел, представленных в модулярно-индексном формате с плавающей точкой, на универсальных многоядерных процессорах. Техническим результатом является повышение скорости вычисления. В способе, выполняемом на универсальном многоядерном вычислителе, содержащим q k разрядных вычислительных ядер, осуществляют операции алгебраического ум...

2652460

Способ организации выполнения операции умножения двух чисел в модулярно-логарифмическом формате представления с плавающей точкой на гибридных многоядерных процессорах

Изобретение относится к вычислительной технике и предназначено для выполнения операции умножения двух чисел в модулярно-логарифмическом формате с плавающей точкой. Техническим результатом является упрощение выполнения операции умножения. Способ осуществляется на гибридных многоядерных процессорах и содержит процедуру умножения двух чисел в модулярном формате с плавающей точкой, включая контроль пе...

2666285