Логический вентиль

Иллюстрации

Показать всеИзобретение относится к электронике и предназначено для использования в интегральных логических устройствах на комплементарных униполярных полевых транзисторах структуры металл-окисел-полупроводник (МОП) с индуцированными каналами p и n типов проводимости и биполярных транзисторах n-p-n и p-n-p структур. Техническим результатом является повышение надежности за счет снижения паразитных емкостей базовых узлов. Логический вентиль содержит МОП-ключи p и n типов проводимости, истоковые выводы которых соответственно подключены к шинам положительного и отрицательного полюсов напряжения питания, эмиттерные повторители на биполярных транзисторах n-p-n и p-n-p структур, коллекторы которых соответственно подключены к шинам положительного и отрицательного полюсов напряжения питания, а эмиттеры соединены с выходом логического вентиля, МОП-ключи p и n типов проводимости составляют более двух комплементарных пар, в каждой из которых стоковые выводы МОП-ключей соединены и подключены к базе биполярного транзистора соответствующего эмиттерного повторителя. 3 ил.

Реферат

Изобретение относится к электронике и предназначено для использования в интегральных логических устройствах на комплементарных униполярных полевых транзисторах структуры металл-окисел-полупроводник (МОП) с индуцированными каналами p и n типов проводимости и биполярных транзисторах n-p-n и p-n-p структур.

Известны логические вентили, выполненные на комплементарных МОП-транзисторах, см., например, Горюнов Е.П. Элементы и узлы ЭЦВМ. Учеб. пособие для втузов. М.: Высшая школа, 1976 [1], с. 176, рис. 9.22. Р- и n-МОП-транзисторы в таких вентилях составляют ключи, попеременно подключающие выход вентиля к шинам положительного и отрицательного полюсов напряжения питания, формируя, таким образом, выходные уровни логических единицы и нуля. Недостатком таких устройств является низкая нагрузочная способность из-за низкой проводимости каналов МОП-транзисторов.

Повысить нагрузочную способность логического вентиля на комплементарных МОП-транзисторах позволяет дополнение его биполярными транзисторами n-p-n и p-n-p структур, образующими выходные эмиттерные повторители, см. [1], с. 224, рис. 11.2. Данное решение по технической сущности и достигаемому положительному эффекту наиболее близко к изобретению.

Наиболее близкий аналог содержит МОП-ключ p типа проводимости и биполярный транзистор n-p-n структуры, истоковый вывод и коллектор которых соединены с шиной положительного полюса напряжения питания, а также n-МОП-ключ и биполярный p-n-p транзистор, истоком и коллектором подключенные к шине отрицательного полюса напряжения питания. Базы биполярных транзисторов соединены и подключены к стоковым выводам МОП-ключей, а эмиттеры соединены и являются выходом логического вентиля.

Устройство работает следующим образом.

При формировании логической единицы на выходе логического вентиля в p-МОП-ключе открывается канал, соединяющий базы биполярных транзисторов с шиной положительного полюса напряжения питания. В это время в n-МОП-ключе канала нет. Вследствие этого на базы биполярных транзисторов выходных эмиттерных повторителей поступает потенциал положительного полюса источника питания.

Нулевое состояние логического вентиля возникает при наличии канала в n-МОП-ключе и отсутствии его в p-МОП-ключе, когда базовый узел выходных биполярных транзисторов подключен к шине отрицательного полюса напряжения питания.

Высокая нагрузочная способность устройства достигается благодаря способности эмиттерных повторителей многократно усиливать передаваемый на выход ток МОП-ключей. Быстродействие логического вентиля, таким образом, в большей степени определяет не скорость перезаряда емкости нагрузки, а задержка переключения напряжения базового узла. Емкость этого узла в основном складывается из емкостей объединяемых в нем стоков транзисторов МОП-ключей, количество которых возрастает при усложнении реализуемой вентилем логической функции.

Это является недостатком устройства-аналога, ограничивающим его функциональные возможности при необходимости получения высокого быстродействия.

Задачей изобретения является достижение технического результата, заключающегося в расширении функциональных возможностей устройства без снижения быстродействия.

Технический результат достигается для логического вентиля, содержащего МОП-ключи p и n типов проводимости, истоковые выводы которых соответственно подключены к шинам положительного и отрицательного полюсов напряжения питания, эмиттерные повторители на биполярных транзисторах n-p-n и p-n-p структур, коллекторы которых соответственно подключены к шинам положиттельного и отрицательного полюсов напряжения питания, а эмиттеры соединены с выходом логического вентиля, отличающегося тем, что МОП-ключи p и n типов проводимости составляют более двух комплементарных пар, в каждой из которых стоковые выводы МОП-ключей соединены и подключены к базе биполярного транзистора соответствующего эмиттерного повторителя.

Указанное выполнение логического элемента позволяет снизить паразитные емкости базовых узлов выходных эмиттерных повторителей за счет уменьшения количества объединяемых в них стоков МОП-транзисторов.

Отличительным признаком изобретения является то, что в составе устройства содержится более двух пар комплементарных МОП-ключей и более двух эмиттерных повторителей.

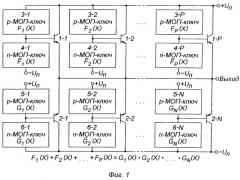

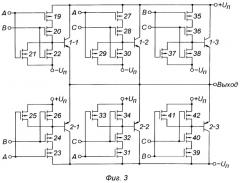

Изобретение поясняется чертежами Фиг. 1-3, на которых изображены структурная схема логического вентиля и принципиальные электрические схемы мажоритарного инвертора 2 из 3, рассматриваемого в качестве примера реализации устройства, в решениях с одной и шестью парами КМОП-ключей.

Логический вентиль Фиг. 1 содержит эмиттерные повторители в количестве Р на биполярных транзисторах 1-1-1-P n-p-n структуры и N эмиттерных повторителей на биполярных транзисторах 2-1-2-N p-n-p структуры, эмиттеры транзисторов 1-1-1-Р и 2-1-2-N соединены с выходом логического вентиля, Р пар КМОП-ключей, состоящих из МОП-ключей 3-1-3-Р р типа проводимости и МОП-ключей 4-1-4-Р n типа проводимости, стоковые узлы которых попарно соединены и соответственно подключены к базовым выводам n-p-n транзисторов 1-1-1-Р, N пар КМОП-ключей, состоящих из МОП-ключей 5-1-5-N p типа проводимости и МОП-ключей 6-1-6-N n типа проводимости, стоковые узлы которых попарно соединены и соответственно подключены к базовым выводам p-n-p транзисторов 2-1-2-N. Коллекторы n-p-n транзисторов 1-1-1-Р, истоковые узлы p-МОП-ключей 3-1-3-Р и 5-1-5-N подключены к шине +UП положительного полюса напряжения питания. Коллекторы p-n-p транзисторов 2-1-2-N, истоковые узлы n-МОП-ключей 4-1-4-Р и 6-1-6-N подключены к шине -UП отрицательного полюса напряжения питания.

Работа устройства основана на попеременном подключении при помощи КМОП-ключей 3-1-3-Р, 4-1-4-Р и 5-1-5-N, 6-1-6-N базовых выводов одного и более n-p-n транзисторов 1-1-1-Р к шине +UП или базовых выводов одного и более n-p-n транзисторов 2-1-2-N к шине -UП для формирования на выходе соответственно напряжения высокого или низкого логического уровня. Во всех определенных состояниях логического вентиля исключено одновременное наличие высокого уровня напряжения на базах n-p-n транзисторов 1-1-1-Р и низкого уровня напряжения на базах p-n-р транзисторов 2-1-2-N.

Объединенные по выходам эмиттерные повторители на транзисторах 1-1-1-Р выполняют дизъюнкцию логических сигналов, поступающих на их базы, поэтому логические уровни напряжений на стоковых узлах пар КМОП-ключей 3-1-3-Р и 4-1-4-Р определяют функции F1(X), F2(X), … ,FP(X), дизъюнкция которых декомпозирует общую функцию устройства. Для этого проводимости р-МОП-ключей 3-1-3-Р соответствуют этим функциям, а проводимости n-МОП-ключей 4-1-4-Р - их инверсиям F ¯ 1 ( X ) , F ¯ 2 ( X ) , … , F ¯ P .

Транзисторы 2-1-2-N формируют нулевые состояния функции F(X), для чего управляющие ими пары КМОП-ключей 5-1-5-N и 6-1-6-N выполняют группу функций G1(X), G2(X), … ,GN(X), конъюнкция которых тождественна функции устройства. Проводимости р-МОП-ключей 5-1-5-N соответствуют функциям G1(X), G2(X), … ,GN(X), а проводимости n-МОП-ключей 6-1-6-N - их инверсиям G ¯ 1 ( X ) , G ¯ 2 ( X ) , … , G ¯ N ( X ) .

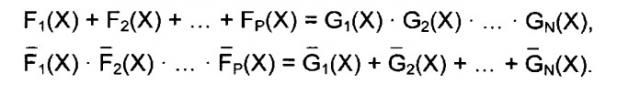

Таким образом, цепи р-МОП-транзисторов, содержащиеся в ключах 3-1-3Р, представляют собой отдельные параллельные цепи эквивалентного единого р-МОП-ключа, а n-МОП-транзисторные цепи ключей 6-1-6-N соответствуют отдельным параллельным цепям эквивалентного единого n-МОП-ключа. Математическую взаимосвязь функций проводимости КМОП-ключей 3-1-3-Р, 4-1-4-Р, 5-1-5-N, 6-1-6-N отражают следующие логические формулы:

Логический вентиль может принимать состояние ′′Выключено′′, если для него предусмотрены состояния, в которых на всех базах n-p-n транзисторов 1-1-1-Р соответствующие КМОП-ключи 3-1-3-Р и 4-1-4-Р формируют напряжения низкого уровня, а КМОП-ключи 5-1-5-N и 6-1-6-N создают высокое напряжение на базах всех p-n-р транзисторов 4-1-4-N.

Рассмотрим пример реализации логического вентиля с функцией мажоритарного инвертора 2 из 3, которая принимает значения логической единицы в случаях, когда не менее двух из трех ее аргументов равны логическому нулю, или значения логического нуля, если не менее двух ее аргументов равны логической единице. Логическую единицу и логический нуль соответственно представляют напряжения высокого и низкого уровней.

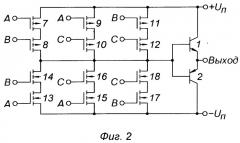

На чертеже Фиг. 2 показана принципиальная электрическая схема, содержащая по одной паре КМОП-ключей и эмиттерных повторителей.

Мажоритарный инвертор содержит с первого по шестой МОП-транзисторы 7-12 с каналом p типа проводимости и с первого по шестой МОП-транзисторы 13-18 с каналом n типа проводимости, составляющие p- и n-МОП-ключи. Затворы p-МОП-транзисторов 7-12 и n-МОП-транзисторов 13-18 с первых по шестые соответственно попарно соединены и подключены к первому А, второму В, первому А, третьему С, второму В, третьему С входам устройства. Стоки первых МОП-транзисторов 7 и 13 соединены с истоками вторых МОП-транзисторов 8 и 14 соответствующих типов. Стоки третьих МОП-транзисторов 11 и 17 соединены с истоками четвертых МОП-транзисторов 10 и 16 соответствующих типов. Стоки пятых МОП-транзисторов 11 и 17 соединены с истоками шестых МОП-транзисторов 12 и 18 совпадающих типов. Истоки первых, третьих и пятых МОП-транзисторов р- и n типов 7, 9, 11 и 13, 15, 17 соответственно подключены к шинам +UП и -UП положительного и отрицательного полюсов напряжения питания. Стоки вторых, четвертых и шестых МОП-транзисторов 8, 10, 12 и 14, 16, 18 подключены к базам образующих выходные эмиттерные повторители n-p-n транзистора 1 и p-n-р транзистора 2, коллекторы которых соответственно подключены к шинам +UП и -UП, а эмиттеры являются выходом устройства.

МОП-транзисторы 7-18 образуют цепи между базами транзисторов 1 и 2 и шинами +UП и -UП, содержащие по два последовательно соединенных транзистора, подключения затворов которых к трем входам А, В, С устройства составляют все три возможных комбинации по два из трех: А, В - р-МОП-транзисторы 7, 8 и n-МОП-13, 14;

A, С - p-МОП-транзисторы 9, 10 и n-МОП-15, 16;

B, С - p-МОП-транзисторы 11, 12 и n-МОП-17, 18.

Двухтранзисторные последовательные цепи образуют сквозные p-каналы при наличие не менее двух логических нулей среди поступающих на входы А, В, С устройства сигналов или n-каналы, когда среди трех входных сигналов А, В, С более одной логической единицы. Это обеспечивает формирование на выходе логического уровня, противоположного преобладающему на входах А, В, С.

Многоключевое решение мажоритарного инвертора 2 из 3 представляет принципиальная схема на чертеже Фиг. 3, она содержит шесть эмиттерных повторителей на n-p-n транзисторах 1-1, 1-2, 1-3 и p-n-р транзисторах 2-1, 2-2, 2-3 и шесть пар КМОП-ключей.

Первая пара КМОП-ключей состоит из первого, второго р-МОП-транзисторов 19, 20 и первого, второго n-МОП-транзисторов 21, 22. Сток транзистора 19 подключен к истоку транзистора 20, сток которого вместе со стоками транзисторов 21, 22 соединены с базой n-p-n транзистора 1-1.

Вторая пара КМОП-ключей состоит из третьего, четвертого n-МОП-транзисторов 23, 24 и третьего, четвертого p-МОП-транзисторов 25, 26. Сток транзистора 23 подключен к истоку транзистора 24, сток которого вместе со стоками транзисторов 25, 26 соединены с базой p-n-р транзистора 2-1.

Третья пара КМОП-ключей состоит из пятого, шестого p-МОП-транзисторов 27, 28 и пятого, шестого n-МОП-транзисторов 29, 30. Сток транзистора 27 подключен к истоку транзистора 28, сток которого вместе со стоками транзисторов 29, 30 соединены с базой n-p-n транзистора 1-2.

Четвертая пара КМОП-ключей состоит из седьмого, восьмого n-МОП-транзисторов 31, 32 и седьмого, восьмого p-МОП-транзисторов 33, 34. Сток транзистора 31 подключен к истоку транзистора 32, сток которого вместе со стоками транзисторов 33, 34 соединены с базой p-n-р транзистора 2-2.

Пятая пара КМОП-ключей состоит из восьмого, девятого р-МОП-транзисторов 35, 36 и восьмого, девятого n-МОП-транзисторов 37, 38. Сток транзистора 35 подключен к истоку транзистора 36, сток которого вместе со стоками транзисторов 37, 38 соединены с базой n-p-n транзистора 1-3.

Шестая пара КМОП-ключей состоит из десятого, одиннадцатого n-МОП-транзисторов 39, 40 и десятого, одиннадцатого p-МОП-транзисторов 41, 42. Сток транзистора 39 подключен к истоку транзистора 40, сток которого вместе со стоками транзисторов 41, 42 соединены с базой p-n-р транзистора 2-3.

Истоки p-МОП-транзисторов 19, 25, 26, 27, 33, 33, 34, 41, 42 и коллекторы n-p-n транзисторов 1-1, 1-2, 1-3 соединены с шиной +UП положительного полюса напряжения питания, а истоки n-МОП-транзисторов 21, 22, 23, 29, 30, 31, 37, 38, 39 и коллекторы p-n-р транзисторов 2-1, 2-2, 2-3 соединены с шиной -UП отрицательного полюса напряжения питания. Затворы транзисторов 19, 21, 23, 25, 27, 29, 31, 33 соединены с первым входом А устройства, затворы транзисторов 20, 22, 24, 26, 35, 37, 39, 41 соединены со вторым входом В устройства, а затворы транзисторов 28, 30, 32, 34, 36, 38, 40, 42 соединены с третьим входом С устройства.

Каждая из P-канальных цепей, содержащих пары p-МОП-транзисторов 19 и 20, 27 и 28, 35 и 36 эквивалентна одной из параллельных цепей из пар p-МОП-транзисторов 7 и 8, 9 и 10, 11 и 12 соответственно в двухключевой схеме (фиг. 2). Комплементарные им n-канальные цепи на транзисторах 21 и 22, 29 и 30, 37 и 38 имеют соответствующие инверсные проводимости.

N-канальные цепи на парах n-МОП-транзисторов 23 и 24, 31 и 32, 39 и 40 соответственно эквивалентны параллельным цепям из пар n-МОП-транзисторов 13 и 14, 15 и 16, 17 и 18 в схеме на чертеже фиг. 2. Проводимости комплементарных им цепей из р-МОП-транзисторов 21 и 22, 29 и 30, 37 и 38 соответственно инверсны.

Первая, третья и пятая пары КМОП-ключей, управляющие n-p-n транзисторами, формируют напряжения высокого уровня в случаях одновременного наличия логических нулей на парах входов А и В, А и С, В и С, что соответствует логическим выражениям A ¯ B ¯ , A ¯ C ¯ , B ¯ C ¯ , а вторая, четвертая и шестая пары КМОП-ключей, управляющие p-n-p транзисторами, создают низкие уровни в случаях логических единиц на тех же парах входов, в соответствии с выражениями A B ¯ , A C ¯ , B C ¯ .

Объединение эмиттеров транзисторов 1-1, 1-2, 1-3 и 2-1, 2-2, 2-3 в узле выхода выполняет дизъюнкцию сигналов со стоковых узлов первой, третьей и пятой пар КМОП-ключей, то есть A ¯ B ¯ + A ¯ C ¯ + B ¯ C ¯ , и конъюнкцию сигналов со стоковых узлов второй, четвертой и шестой пар - ( A ¯ + B ¯ ) ( A ¯ + C ¯ ) ( B ¯ + C ¯ ) , эквивалентную выражению A ¯ B ¯ + A ¯ C ¯ + B ¯ C ¯ в силу ее самодвойственности.

Преимущество многоключевого решения мажоритарного инвертора 2 из 3 в быстродействии достигается уменьшением паразитных емкостей в узлах баз его биполярных транзисторов, определяемых количеством объединяемых в них транзисторных выводов, что позволяет ускорить процессы изменения напряжений в них при переключениях выходных состояний. В схеме фиг. 3 эта емкость снижена примерно в двое, так как ее создают три стоковых и один базовый выводы, в то время как в схеме фиг. 2 она складывается из паразитных емкостей шести стоков и двух баз.

Многоключевое решение логического вентиля на комплементарных МОП и биполярных транзисторах тем эффективнее, чем больше параллельных цепей можно выделить в отдельные КМОП-ключи.

Логический вентиль, содержащий МОП-ключи p и n типов проводимости, истоковые выводы которых соответственно подключены к шинам положительного и отрицательного полюсов напряжения питания, эмиттерные повторители на биполярных транзисторах n-p-n и p-n-p структур, коллекторы которых соответственно подключены к шинам положительного и отрицательного полюсов напряжения питания, а эмиттеры соединены с выходом логического вентиля, отличающийся тем, что МОП-ключи p и n типов проводимости составляют более двух комплементарных пар, в каждой из которых стоковые выводы МОП-ключей соединены и подключены к базе биполярного транзистора соответствующего эмиттерного повторителя.