Усилитель и устройство обработки сигналов

Иллюстрации

Показать всеГруппа изобретений относится к усилителю устройства обработки сигналов. Технический результат заключается в обеспечении возможности усиления входного сигнала, содержащего низкочастотный компонент. Когда переключатель (SW1) задается выключенным, а переключатель (SW2) задается включенным, напряжение контактного вывода (205) SigOut стабилизируется с помощью опорного напряжения, и напряжение смещения прикладывается к конденсатору (C1). Изменяя переключатель (SW2) из включенного состояния в выключенное при напряжении смещения, сохраненном в конденсаторе (C1), сигнал обнаружения, который вводится через контактный вывод (201) SigIn, усиливается с помощью опорного напряжения в качестве опорного уровня, и усиленный сигнал выводится из контактного вывода (205) SigOut. 2 н. и 10 з.п. ф-лы, 27 ил.

Реферат

ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

[0001] Изобретение относится к усилителю и устройству обработки сигналов.

УРОВЕНЬ ТЕХНИКИ

[0002] Магнитный датчик является датчиком для обнаружения рисунков магнитного поля в обнаруживаемом теле с использованием элемента на магниторезистивном эффекте, имеющего такое свойство, что значение сопротивления изменяется согласно приложенному магнитному полю. Поскольку степень намагничивания в рисунке магнитного поля, который имеют бумажные деньги или другое обнаруживаемое тело, является низкой, изменение значения сопротивления элемента на магниторезистивном эффекте является низким. Соответственно, в магнитном датчике, который использует магниторезистивные элементы с мостовым соединением, напряжение средней точки, сформированное из средней точки элементов на магниторезистивном эффекте с мостовым соединением, является низким, так что, например, требуется усиление с большим коэффициентом усиления, к примеру, 1000.

[0003] Напряжение средней точки, сформированное из средней точки элементов на магниторезистивном эффекте с мостовым соединением, колеблется вследствие изменений в отдельных элементах на магниторезистивном эффекте, колебаний напряжения источника питания, а также колебаний температуры. Следовательно, затем напряжение средней точки усиливается с большим коэффициентом усиления, может возникать насыщение усилителя, так что не получается корректная обнаруженная форма сигнала. В области техники, раскрытой в патентных документах 1 и 2, усиливается только измененная часть, исключая часть постоянного тока. Помимо этого, в области техники, раскрытой в патентных документах 3-6, усиливается только измененная часть, исключая напряжение смещения.

СПИСОК БИБЛИОГРАФИЧЕСКИХ ССЫЛОК

ПАТЕНТНЫЕ ДОКУМЕНТЫ

[0004] Патентный документ 1. Публикация не прошедшей экспертизу заявки на полезную модель (Япония) № H05-085060

Патентный документ 2. Публикация не прошедшей экспертизу заявки на патент (Япония) № 2000-162296.

Патентный документ 3. Публикация не прошедшей экспертизу заявки на патент (Япония) № 2010-223862.

Патентный документ 4. Публикация не прошедшей экспертизу заявки на патент (Япония) № H7-287802.

Патентный документ 5. Публикация не прошедшей экспертизу заявки на патент (Япония) № 2000-195003.

Патентный документ 6. Публикация не прошедшей экспертизу заявки на патент (Япония) № 2001-16052.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

ТЕХНИЧЕСКАЯ ЗАДАЧА

[0005] Например, в области техники, раскрытой в патентном документе 1, сигнал постоянного тока в обнаруженном сигнале удаляется с использованием фильтра верхних частот, в котором частота среза определяется посредством электростатической емкости и сопротивления. Тем не менее, когда низкочастотный компонент включается в обнаруженный сигнал, требуется конденсатор, имеющий электростатическую емкость порядка мкФ, так что схема обработки сигналов становится более крупной.

[0006] С учетом вышеприведенного, задача настоящего изобретения заключается в том, чтобы уменьшать размер усилителя и устройства обработки сигналов, допускающих усиление входного сигнала, содержащего низкочастотный компонент.

РЕШЕНИЕ ЗАДАЧИ

[0007] Чтобы решить вышеописанную задачу, усилитель по настоящему изобретению содержит первый резистор, первый операционный усилитель, второй резистор, второй операционный усилитель, первый конденсатор, первый переключатель, третий резистор, второй переключатель и схему управления. Входной сигнал подается на инвертирующий входной контактный вывод первого операционного усилителя из входного сигнального контактного вывода через первый резистор. Один конец второго резистора подключается к инвертирующему входному контактному выводу первого операционного усилителя, а другой конец подключается к выходному контактному выводу первого операционного усилителя. Предписанное опорное напряжение подается на неинвертирующий входной контактный вывод второго операционного усилителя, и выходной контактный вывод второго операционного усилителя подключается к неинвертирующему входному контактному выводу первого операционного усилителя. Один конец первого конденсатора подключается к инвертирующему входному контактному выводу второго операционного усилителя, а другой конец подключается к выходному контактному выводу второго операционного усилителя. Один конец первого переключателя подключается к инвертирующему входному контактному выводу второго операционного усилителя, а другой конец подключается к выходному контактному выводу второго операционного усилителя. Третий резистор и второй переключатель подключены последовательно с одним концом, подключенным к выходному контактному выводу первого операционного усилителя, а другим концом, подключенным к инвертирующему входному контактному выводу второго операционного усилителя. Схема управления принимает ввод управляющих сигналов усилителя и включает, и выключает первый переключатель и второй переключатель в предписанном порядке на основе управляющих сигналов усилителя. Посредством процесса переключения схемы управления первый операционный усилитель усиливает входной сигнал с помощью опорного напряжения в качестве опорного уровня, и усиленный сигнал выводится из выходного сигнального контактного вывода, подключенного к выходному контактному выводу первого операционного усилителя.

ПРЕИМУЩЕСТВА ИЗОБРЕТЕНИЯ

[0008] С помощью настоящего изобретения, можно уменьшать размер усилителя и устройства обработки сигналов, допускающих усиление входного сигнала, содержащего низкочастотный компонент

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

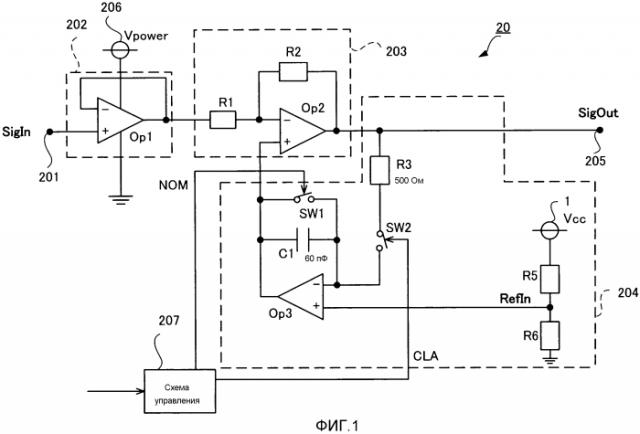

[0009] Фиг. 1 является чертежом, показывающим примерную структуру усилителя согласно первому предпочтительному варианту осуществления настоящего изобретения;

Фиг. 2 является чертежом, показывающим другую примерную структуру усилителя согласно первому предпочтительному варианту осуществления;

Фиг. 3 является чертежом, показывающим другую примерную структуру усилителя согласно первому предпочтительному варианту осуществления;

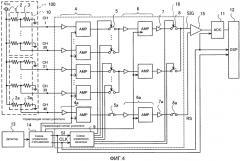

Фиг. 4 является чертежом, показывающим примерную структуру устройства обработки сигналов согласно первому предпочтительному варианту осуществления;

Фиг. 5 является блок-схемой последовательности операций способа, показывающей один пример действия обработки сигналов, выполняемой посредством устройства обработки сигналов согласно первому предпочтительному варианту осуществления;

Фиг. 6 является диаграммой переходов состояний для переключателей в первом предпочтительном варианте осуществления;

Фиг. 7 является чертежом, показывающим формы сигнала напряжения во время коррекции напряжения средней точки контактного вывода SigOut в усилителе согласно первому предпочтительному варианту осуществления;

Фиг. 8 является чертежом, показывающим частотные характеристики во время коррекции напряжения средней точки усилителя согласно первому предпочтительному варианту осуществления;

Фиг. 9 является временной диаграммой для различных управляющих сигналов в первом предпочтительном варианте осуществления;

Фиг. 10 является чертежом, показывающим частотные характеристики во время считывания сигналов в нормальном режиме усилителя согласно первому предпочтительному варианту осуществления;

Фиг. 11 является чертежом, показывающим процесс подавления ненужной волны в устройстве обработки сигналов согласно первому предпочтительному варианту осуществления;

Фиг. 12 является чертежом, показывающим форму сигнала напряжения в высокоскоростном режиме контактного вывода SigOut усилителя согласно первому предпочтительному варианту осуществления;

Фиг. 13 является чертежом, показывающим частотные характеристики во время считывания сигналов в высокоскоростном режиме усилителя согласно первому предпочтительному варианту осуществления;

Фиг. 14 является чертежом, показывающим другую примерную структуру устройства обработки сигналов согласно первому предпочтительному варианту осуществления;

Фиг. 15 является чертежом, показывающим отклонение напряжения средней точки в дифференциальном усилителе, содержащемся в устройстве обработки сигналов согласно второму предпочтительному варианту осуществления настоящего изобретения;

Фиг. 16 является чертежом, показывающим примерную структуру усилителя согласно третьему предпочтительному варианту осуществления настоящего изобретения;

Фиг. 17 является диаграммой переходов состояний для переключателей согласно третьему предпочтительному варианту осуществления;

Фиг. 18 является чертежом, показывающим примерную структуру усилителя согласно четвертому предпочтительному варианту осуществления настоящего изобретения;

Фиг. 19 является диаграммой переходов состояний для переключателей согласно четвертому предпочтительному варианту осуществления;

Фиг. 20 является чертежом схемы для комплементарных переключателей, предоставленных в усилителе согласно пятому предпочтительному варианту осуществления настоящего изобретения;

Фиг. 21 является чертежом, показывающим примерную структуру устройства обработки сигналов согласно шестому предпочтительному варианту осуществления настоящего изобретения;

Фиг. 22 является чертежом, показывающим примерную структуру устройства обработки сигналов согласно седьмому предпочтительному варианту осуществления настоящего изобретения;

Фиг. 23 является временной диаграммой для различных управляющих сигналов согласно восьмому предпочтительному варианту осуществления настоящего изобретения;

Фиг. 24 является другой временной диаграммой для различных управляющих сигналов согласно восьмому предпочтительному варианту осуществления настоящего изобретения;

Фиг. 25 является диаграммой переходов состояний для переключателей согласно девятому предпочтительному варианту осуществления настоящего изобретения;

Фиг. 26 является диаграммой переходов состояний для переключателей согласно девятому предпочтительному варианту осуществления; и

Фиг. 27 является диаграммой переходов состояний для переключателей согласно девятому предпочтительному варианту осуществления.

ПОДРОБНОЕ ОПИСАНИЕ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ

[0010] Ниже подробно описываются предпочтительные варианты осуществления настоящего изобретения со ссылкой на чертежи. На чертежах, части, которые являются идентичными или эквивалентными, помечаются идентичными условными обозначениями.

[0011] ПЕРВЫЙ ПРЕДПОЧТИТЕЛЬНЫЙ ВАРИАНТ ОСУЩЕСТВЛЕНИЯ

Фиг. 1 является чертежом, показывающим примерную структуру усилителя согласно первому предпочтительному варианту осуществления настоящего изобретения. С использованием фиг. 1, описывается усилитель согласно первому предпочтительному варианту осуществления настоящего изобретения на предмет принципа усиления входного сигнала. Усилитель 20 содержит усилитель 202 повторителя напряжения, содержащий операционный усилитель Op1 (далее называемый «op-amp» (операционным усилителем)), инвертирующий усилитель 203, схему 204 DC обратной связи и схему 207 управления. Входной сигнал вводится из контактного вывода 201 SigIn, который является входным сигнальным контактным выводом, и вводится в инвертирующий усилитель 203 через усилитель 202 повторителя напряжения. Электрический потенциал неинвертирующего входного контактного вывода операционного усилителя Op2 (первого операционного усилителя), которым обеспечен инвертирующий усилитель 203, определяется посредством схемы 204 DC обратной связи.

[0012] Инвертирующий усилитель 203 содержит резистор R1 (первый резистор), резистор R2 (второй резистор) и операционный усилитель Op2. Резистор R1 размещается между выходным контактным выводом усилителя 202 повторителя напряжения и инвертирующим входным контактным выводом операционного усилителя Op2, и резистор R2 подключается на одном конце к инвертирующему входному контактному выводу операционного усилителя Op2, а на другом конце - к выходному контактному выводу операционного усилителя Op2.

[0013] Схема 204 DC обратной связи содержит операционный усилитель Op3 (второй операционный усилитель), конденсатор C1 (первый конденсатор), переключатель SW1 (первый переключатель), резистор R3 (третий резистор), переключатель SW2 (второй переключатель) и резисторы R5 и R6. Резистор R3 и переключатель SW2 подключены последовательно с одним концом, подключенным к выходному контактному выводу операционного усилителя Op2, а другим концом, подключенным к инвертирующему входному контактному выводу операционного усилителя Op3. Опорное напряжение, которое является значением напряжения источника 1 питания постоянного тока, разделенным посредством резистора R5 и резистора R6 (RefIn на чертеже), подается на неинвертирующий входной контактный вывод операционного усилителя Op3.

[0014] Например, допустим, что можно изменять соответствующие значения сопротивления резисторов R5 и R6 через непредставленный переключатель с использованием в качестве резисторов R5 и R6 сопротивления в 45 кОм, сформированного посредством последовательного подключения 90 резисторов на 500 Ом, подключенных последовательно. Например, в случае 1, значение сопротивления резистора R5 составляет 28,5 кОм, а значение сопротивления резистора R6 составляет 16,5 кОм. В случае 2, значение сопротивления резистора R5 составляет 22,5 кОм, а значение сопротивления резистора R6 составляет 22,5 кОм. При условии, что источник питания постоянного тока имеет 4,5 В, опорное напряжение в случае 1 составляет 1,65 В, а опорное напряжение в случае 2 составляет 2,25 В.

[0015] Конденсатор 1 и переключатель SW1 оба подключены на одном конце к инвертирующему входному контактному выводу операционного усилителя Op3, а на другом конце - к выходному контактному выводу операционного усилителя Op3. Операционные усилители Op1, Op2 и Op3 подключаются к источнику 206 питания IC. На фиг. 1 обозначения подключения операционных усилителей Op2 и Op3 к источнику 206 питания IC пропущены. Инвертирующий усилитель 203 и схема 204 DC обратной связи формируют усилитель схемы фиксации уровня DC.

[0016] Схема 207 управления принимает ввод NOM-сигнала и CLA-сигнала, которые являются управляющими сигналами усилителя, и отправляет NOM-сигнал в переключатель SW1 и CLA-сигнал в переключатель SW2. Переключатели SW1 и SW2 изменяются между включенным и выключенным состоянием на основе уровня сигнала NOM-сигнала и CLA-сигнала, соответственно. Посредством процесса переключения схемы 207 управления, настройки включения и выключения переключателей SW1 и SW2 переключаются в предписанном порядке, и за счет этого входной сигнал усиливается в операционном усилителе Op2, и усиленный сигнал выводится через контактный вывод 205 SigOut, который является выходным сигнальным контактным выводом.

[0017] Фиг. 2 является чертежом, показывающим другую примерную структуру усилителя согласно первому предпочтительному варианту осуществления. Усилитель 20, показанный на фиг. 2, содержит конденсатор C2 (второй конденсатор), подключенный параллельно к резистору R2, в дополнение к структуре усилителя 20, показанного на фиг. 1. Посредством предоставления конденсатора C2 сохраняется запас по фазе инвертирующего усилителя 203.

[0018] Фиг. 3 является чертежом, показывающим другую примерную структуру усилителя согласно первому предпочтительному варианту осуществления. Усилитель 20, показанный на фиг. 3, дополнительно содержит резистор R4 (четвертый резистор) и переключатель SW3 (третий переключатель), в дополнение к структуре усилителя 20, показанного на фиг. 3. Резистор R4 и переключатель SW3 подключены последовательно с одним концом, подключенным к выходному контактному выводу операционного усилителя Op2, а другим концом, подключенным к инвертирующему входному контактному выводу операционного усилителя Op3. Усилитель 20 по фиг. 3 допускает выполнение следящего действия, и инвертирующий усилитель 203 и схема 204 DC обратной связи формируют следящий усилитель схемы фиксации уровня DC. Когда запас по фазе удовлетворяет искомым характеристикам даже в том случае, если конденсатор C2 исключается, можно обеспечивать большую компактность усилителя посредством исключения конденсатора C2. То же является истинным в нижеописанных предпочтительных вариантах осуществления.

[0019] Схема 207 управления принимает ввод NOM-сигнала, SER-сигнала и CLA-сигнала, которые являются управляющими сигналами усилителя, и отправляет NOM-сигнал в переключатель SW1, SER-сигнал в переключатель SW2 и CLA-сигнал в переключатель SW3. Переключатели SW1, SW2 и SW3 изменяются между включенным и выключенным состоянием на основе уровня сигнала NOM-сигнала, SER-сигнала и CLA-сигнала, соответственно.

[0020] Фиг. 4 является чертежом, показывающим примерную структуру устройства обработки сигналов согласно первому предпочтительному варианту осуществления. Фиг. 4 показывает пример устройства обработки сигналов, используемого в магнитном датчике. Устройство обработки сигналов содержит датчик 100, детектор 13, схему 14 управления считыванием, IC 16 (интегральную схему) усилителя, дифференциальный усилитель 15, ADC 11 (аналого-цифровой преобразователь) и процессор 12 цифровых сигналов (в дальнейшем называемый "DSP"). Обнаруживаемое тело, такое как бумажные деньги, транспортируется вдоль непредставленного маршрута транспортировки.

[0021] Устройство обработки сигналов обнаруживает предписанную физическую величину, которая изменяется вследствие обнаруживаемого тела, и использует элементы 2 и 3 на MR (магниторезистивном эффекте) с мостовым соединением в качестве устройств обнаружения для вывода сигналов обнаружения, напряжения которых изменяются в соответствии с изменениями предписанной физической величины. MR-элемент 2 и MR-элемент 3 имеют мостовое соединение, и один конец MR-элемента 2 подключается к источнику 1 питания постоянного тока, и один конец MR-элемента 3 заземляется. Напряжение средней точки MR-элементов 2 и 3 выводится в качестве сигнала обнаружения. MR-микросхема 10 содержит множество MR-элементов 2 и 3 с мостовым соединением. Датчик 100 содержит, например, множество MR-микросхем 10, размещенных линейно. MR-элементы 2 и 3 включают в себя, по меньшей мере, часть маршрута транспортировки в области обнаружения, и можно определять изменения предписанной физической величины, сформированные посредством обнаруживаемого тела, проходящего по маршруту транспортировки. MR-элементы 2a и 3a имеют структуры, идентичные структурам MR-элементов 2 и 3, соответственно, но ни одна из частей маршрута транспортировки не включается в их область обнаружения.

[0022] IC 16 усилителя содержит канальные усилители 4 и 4a, канальные переключатели 5 и 5a, выходные усилители 6 и 6a, выходные буферы 7 и 7a, выходные переключатели 8 и 8a и схему 9 управления каналами. Канальный усилитель 4 для каналов CH1-CH39 подключается к точкам подключения MR-элементов 2 и 3, соответственно, а канальный усилитель 4a для канала CH40 подключается к точке подключения MR-элементов 2a и 3a. Выводы множества канальных усилителей 4 вводятся в выходные усилители 6 через канальный переключатель 5, соответственно, и вывод канального усилителя 4a вводится в выходной усилитель 6a через канальный переключатель 5a. Выводы выходных усилителей 6 вводятся в выходные буферы 7, соответственно, и вывод выходного усилителя 6a вводится в выходной буфер 7a. Выходные переключатели 8, соответственно, подключаются к выходным буферам 7, и выходной переключатель 8a подключается к выходному буферу 7a.

[0023] Детектор 13 обнаруживает поступление обнаруживаемого тела на маршрут транспортировки и выводит сигнал обнаружения, указывающий отсутствие или присутствие поступления обнаруживаемого тела на маршрут транспортировки, в схему 14 управления считыванием. Схема 14 управления считыванием отправляет управляющий сигнал усилителя, уровень сигнала которого изменяется на основе сигнала обнаружения, в канальные усилители 4 и выходные усилители 6. Помимо этого, схема 14 управления считыванием отправляет SI-сигнал для управления считыванием, который представляет собой сигнал управления каналами, уровень сигнала которого изменяется на основе сигнала обнаружения, в схему 9 управления каналами и DSP 12 и отправляет CLK-сигнал, указывающий время считывания, который представляет собой сигнал управления каналами, в схему 9 управления каналами, ADC 11 и DSP 12.

[0024] Канальные усилители 4 имеют усилители 20, показанные на любом из фиг. 1-3. Усилители, которые имеют канальные усилители 4, показанные на фиг. 4, означают усилители схемы фиксации уровня DC или следящие усилители схемы фиксации уровня DC. Канальные усилители 4 усиливают сигналы обнаружения посредством переключения переключателей, которые имеют усилители 20, между включенным и выключенным состоянием в предписанном порядке на основе управляющих сигналов усилителя, отправленных из схемы 14 управления считыванием, и выводят усиленные сигналы. Каждый канальный переключатель 5 переключается между включенным и выключенным состоянием в предписанном порядке на основе сигналов управления переключателем, выводимых посредством схемы 9 управления каналами, на основе SI-сигнала и CLK-сигнала. Посредством переключения каждого канального переключателя 5 между включенным и выключенным состоянием в предписанном порядке, усиленные сигналы, выводимые посредством каждого канального усилителя 4, вводятся в выходной усилитель 6 в предписанном порядке, например, для каждых 20 каналов. Например, канальные переключатели 5 CH1-CH39 переключаются из выключенного во включенное состояние по порядку, соответственно, и переключаются в выключенное состояние после того, как заданное время истекло.

[0025] Выходные усилители 6 имеют усилители 20, показанные на любом из фиг. 1-3. Усилители, которые имеют выходные усилители 6, показанные на фиг. 4, означают усилители схемы фиксации уровня DC или следящие усилители схемы фиксации уровня DC. Выходные усилители 6 переключают переключатели, предоставленные в усилителях 20, между включенным и выключенным состоянием в предписанном порядке на основе управляющего сигнала усилителя, выводимого из схемы 14 управления считыванием, и за счет этого усиливают усиленные сигналы и выводят их в выходные буферы 7. Каждый выходной усилитель 8 переключается между включенным и выключенным состоянием в предписанном порядке на основе сигналов управления переключателем, которые схема 9 управления каналами выводит на основе CLK-сигнала. Посредством переключения каждого выходного переключателя 8 между включенным и выключенным состоянием в предписанном порядке, усиленные сигналы, усиленные посредством выходных усилителей 6, подвергаются последовательному преобразованию. Посредством канальных переключателей 5, выходных усилителей 6, выходных буферов 7, выходных переключателей 8 и схемы 9 управления каналами схемы управления, взаимодействующих и выступающих в качестве параллельно-последовательного преобразователя, усиленные сигналы преобразуются в последовательности, и SIG-сигналы, представляющие собой последовательные сигналы, вводятся в дифференциальный усилитель 15.

[0026] Канальный усилитель 4a имеет структуру, идентичную структуре канального усилителя 4. Хорошо, если канальный переключатель 5a обычно находится во включенном состоянии и имеет такую структуру, что включение/выключение повторяется синхронно с включением/выключением каждого канального переключателя 5. Выходной усилитель 6a имеет структуру, идентичную структуре выходных усилителей 6. Выходной буфер 7a имеет структуру, идентичную структуре выходных буферов 7. Хорошо, если выходной переключатель 8a обычно находится во включенном состоянии и имеет такую структуру, что включение/выключение повторяется синхронно с включением/выключением каждого выходного переключателя 8. Сигнал обнаружения, который является напряжением средней точки MR-элементов 2a и 3a, усиливается посредством канального усилителя 4a и выходного усилителя 6a и вводится в качестве RS-сигнала в дифференциальный усилитель 15.

[0027] Дифференциальный усилитель 15 усиливает разность между SIG-сигналом и RS-сигналом и выводит результат в ADC 11. ADC 11 преобразует вывод дифференциального усилителя 15 в цифровой на основе CLK-сигнала и отправляет результат в DSP 12. DSP 12 выполняет предписанную обработку сигналов на основе SI-сигнала и CLK-сигнала.

[0028] Фиг. 5 является блок-схемой последовательности операций способа, показывающей один пример действий обработки сигналов, выполняемой посредством устройства обработки сигналов согласно первому предпочтительному варианту осуществления. Фиг. 6 является диаграммой переходов состояний для переключателей согласно первому предпочтительному варианту осуществления. Фиг. 6 выражает как включенное или выключенное состояние каждого переключателя, который имеет усилитель 20, на каждом этапе обработки сигналов и выражает как H (высокий) или L (низкий) уровень управляющего сигнала усилителя для управления переключателями. Действия устройства обработки сигналов поясняются с использованием фиг. 5 и 6. Здесь считается, что канальные усилители 4 и 4a и выходные усилители 6 и 6a имеют усилители 20, показанные на фиг. 3.

[0029] Во-первых, пояснение приводится для нормального режима, в котором схема 204 DC обратной связи не проводит следящее действие. Усилители 20, которые имеют канальные усилители 4 и 4a и выходные усилители 6 и 6a, выполняют инициализацию (этап S1). На этапе S1 переключатель SW1 усилителя 20, который, соответственно, имеют канальные усилители 4 и 4a и выходные усилители 6 и 6a, задается включенным, а переключатели SW2 и SW3 задаются выключенными.

В это время схема 204 DC обратной связи имеет структуру, идентичную структуре усилителя 206 повторителя напряжения, опорное напряжение прикладывается к неинвертирующему входному контактному выводу операционного усилителя Op2, и усиленный сигнал, вычисленный посредством умножения значения, вычисленного посредством деления значения сопротивления резистора R2 на значение сопротивления резистора R1, на DC-позицию сигнала, вводимого в контактный вывод 201 SigIn, выводится из контактного вывода 205 SigOut. Опорное напряжение на этапе S1 составляет 2,25 В.

[0030] Детектор 13 выполняет обнаружение того, поступило или нет обнаруживаемое тело на маршрут транспортировки (этап S2). Когда отсутствует поступление обнаруживаемого тела на маршрут транспортировки (этап S3: N), процесс обнаружения этапа S2 продолжается. Когда определяется поступление обнаруживаемого тела на маршрут транспортировки (этап S3: Y), сигнал обнаружения детектора 13 переходит к H-уровню, и переключатель SW3 переключается из выключенного во включенное состояние. Помимо этого, опорное напряжение становится равным 1,65 В.

[0031] Кроме того, усилитель 20, который имеют канальные усилители 4 и 4a и выходные усилители 6 и 6a, выполняет коррекцию напряжения средней точки (этап S4). В усилителе 20, когда переключатели SW1 и SW2 задаются выключенными, а переключатель SW3 задается включенным, обратная связь применяется таким образом, что напряжение контактного вывода 205 SigOut совпадает с опорным напряжением 1,65 В, так что напряжение контактного вывода 205 SigOut стабилизируется при опорном напряжении 1,65 В. Фиг. 7 является чертежом, показывающим форму сигнала напряжения во время коррекции напряжения средней точки контактного вывода SigOut в усилителе согласно первому предпочтительному варианту осуществления. Верхняя часть по фиг. 7 показывает форму сигнала напряжения контактного вывода SigOut, а нижняя часть по фиг. 7 показывает изменение CLA-сигнала. Когда CLA-сигнал имеет H-уровень, переключатель SW3 находится во включенном состоянии. Например, при условии, что емкость конденсатора C1 составляет 60 пФ, а значение сопротивления резистора R4 составляет 500 Ом, после того как переключатель SW3 переключается из выключенного во включенное состояние, напряжение контактного вывода 205 SigOut стабилизируется при 1,65 В за короткое время приблизительно в 20 мкс.

[0032] Фиг. 8 является чертежом, показывающим частотные характеристики во время коррекции напряжения средней точки для усилителя согласно первому предпочтительному варианту осуществления. В вышеописанном примере, нижний предел частоты среза усилителя 20 является высоким и превышает 1 МГц, так что прохождение низкочастотного компонента через усилитель 20 невозможно.

[0033] На этапе S4, когда напряжение контактного вывода 205 SigOut стабилизировано при 1,65 В, напряжение, приложенное к конденсатору C1, сохраняется в качестве напряжения смещения. После этого, CLA-сигнал изменяется на L-уровень, и переключатель SW3 переключается из включенного в выключенное состояние. Фиг. 9 является временной диаграммой для каждого управляющего сигнала в первом предпочтительном варианте осуществления. После того, как сигнал обнаружения изменяется на H-уровень, CLA-сигнал изменяется на H-уровень. Кроме того, после того как фиксированное время истекло, CLA-сигнал изменяется на L-уровень.

[0034] Устройство обработки сигналов выполняет процесс считывания (этап S5). Схема 14 управления считыванием выполняет управление таким образом, что SI-сигнал, который представляет собой сигнал управления каналами, изменяется на H-уровень. Как показано на фиг. 9, CLA-сигнал изменяется на L-уровень после того, как заданное время истекло, после чего SI-сигнал изменяется на H-уровень.

[0035] На этапе S5-S9, переключатели SW1, SW2 и SW3 задаются выключенными, и усилитель 20 работает посредством напряжения смещения, сохраненного в конденсаторе C1. Посредством утечки электрического заряда, накопленного в конденсаторе C1, в схему и т.п., напряжение смещения конденсатора C1 варьируется. Тем не менее, при считывании обнаруживаемого тела, такого как бумажные деньги, например, при условии, что скорость транспортировки составляет 0,5-2 м/сек, хорошо, если напряжение смещения может сохраняться приблизительно в течение 100 миллисекунд. Например, когда операционный усилитель с использованием MOSFET (полевых транзисторов на основе перехода металл-оксид-полупроводник) используется для операционного усилителя Op3, если электростатическая емкость конденсатора C1 составляет несколько десятков пФ, можно сохранять напряжение смещения в течение времени, необходимого для считывания обнаруживаемого тела. Фиг. 10 является чертежом, показывающим частотные характеристики в ходе считывания сигналов в нормальном режиме усилителя согласно первому предпочтительному варианту осуществления. Диапазон пропускания усилителя 20 в ходе считывания сигналов составляет от нескольких Гц до 1 МГц, так что появляется возможность усиливать низкочастотные компоненты.

[0036] На этапе S5 каждый канальный усилитель 4 удаляет постоянный компонент тока сигнала обнаружения, который является напряжением средней точки каждого MR-элемента 2 и 3, и усиливает сигнал обнаружения с использованием опорного напряжения в качестве опорного уровня. Каждый выходной усилитель 6 удаляет постоянный компонент тока усиленных сигналов, вводимых по порядку с переключением канальных переключателей 5 между включенным и выключенным состоянием, и усиливает с помощью опорного напряжения в качестве опорного уровня, идентичного опорному уровню канальных усилителей 4. Посредством переключения выходных переключателей 8 между включенным и выключенным состоянием в предписанном порядке, усиленные сигналы, выводимые посредством выходных усилителей 6, вводятся в дифференциальный усилитель 15 по порядку в качестве SIG-сигналов, как показано в самой нижней части по фиг. 9. Каждое число на фиг. 9 указывает номер канала.

[0037] Помимо этого, канальный усилитель 4a удаляет часть постоянного тока сигнала обнаружения, который является напряжением средней точки MR-элементов 2a и 3a, и усиливает сигнал обнаружения с помощью опорного напряжения в качестве опорного уровня. Выходной усилитель 6a удаляет постоянный компонент тока усиленного сигнала и усиливает усиленный сигнал с помощью опорного напряжения в качестве опорного уровня, идентичного опорному уровню канального усилителя 4a. Вывод выходного усилителя 6a становится RS-сигналом.

[0038] Дифференциальный усилитель 15 подавляет ненужные компоненты (этап S6). Область обнаружения MR-элементов 2a и 3a не содержит частей маршрута транспортировки, так что сигнал обнаружения для CH40 состоит из постоянного компонента тока и ненужных компонентов, наложенных посредством колебания питающего напряжения, помех при передаче синхросигналов и т.п. С другой стороны, сигналы обнаружения для CH1-CH39 состоят из постоянного компонента тока, переменного компонента тока и ненужных компонентов. MR-элементы 2a и 3a формируются линейно в датчике 100 вместе с MR-элементами 2 и 3, так что ненужные компоненты, включенные в сигнал обнаружения CH40, являются сигналом, фактически синфазным с ненужными компонентами, включенными в сигналы обнаружения других каналов.

[0039] Фиг. 11 является чертежом, показывающим процесс подавления ненужной волны в устройстве обработки сигналов согласно первому предпочтительному варианту осуществления. Дифференциальный усилитель 15 усиливает разность между SIG-сигналом и RS-сигналом. Как показано в части A во времени считывания CH1, когда ненужные компоненты, которые являются синфазными и имеют идентичную амплитуду, накладываются на SIG-сигнал и RS-сигнал, соответственно, сигнал, в котором исключены ненужные компоненты, выводится из дифференциального усилителя 15. Помимо этого, как показано в части B во времени считывания CH2, когда ненужные компоненты, которые являются синфазными и имеют взаимно различные амплитуды, накладываются на SIG-сигнал и RS-сигнал, соответственно, сигнал, в котором подавляется ненужный компонент, выводится из дифференциального усилителя 15. Другими словами, синфазные ненужные компоненты, наложенные на SIG-сигнал и RS-сигнал, подавляются посредством дифференциального усилителя 15, и сигнал, в котором улучшается отношение "сигнал-шум" (отношение S/N), выводится из дифференциального усилителя 15.

[0040] ADC 11 преобразует в цифровой сигнал, выводимый из дифференциального усилителя 15 (этап S7), и отправляет результат в DSP 12. DSP 12 сохраняет цифровой сигнал, выводимый посредством ADC 11 (этап S8). Когда процесс считывания не повторяется предписанное число раз, определенное в соответствии со временем прохождения обнаруживаемого тела, такого как бумажные деньги (этап S9: N), процесс возвращается к этапу S5, и процесс считывания повторяется. Когда процесс считывания повторяется предписанное число раз (этап S9: Y), процесс возвращается к этапу S2 и выполняет процесс обнаружения бумажных денег. Устройство обработки сигналов многократно выполняет вышеописанный процесс.

[0041] DSP 12 подвергает обработке сигналов цифровые сигналы, сохраненные на этапе S8 вышеописанной обработки сигналов, в произвольное время и выводит результат в качестве данных обнаружения магнитного датчика.

[0042] Когда частотные характеристики обнаруженного сигнала не концентрируются на стороне высокого диапазона в несколько десятков кГц или больше, усилитель 20 не должен выполнять действие в высокоскоростном режиме, которое вызывает следящее действие схемы 204 DC обратной связи, описанной ниже. Соответственно, хорошо, если структура канальных усилителей 4 и 4a является такой, что предоставляется усилитель 20 по фиг. 1 или фиг. 2. В этом случае, в усилителе 20 по фиг. 1 или фиг. 2, переключатели SW1 и SW2 включаются и выключаются идентично переключателям SW1 и SW3 усилителя 20 на фиг. 3, как показано на фиг. 5, так что можно выполнять действие обработки сигналов, как описано выше.

[0043] Далее поясняется действие в высокоскоростном режиме, которое вызывает следящее действие в схеме 204 DC обратной связи. Когда частотные компоненты, содержащиеся в сигнале обнаружения, превышают несколько десятков кГц, можно стабилизировать напряжение контактного вывода 205 SigOut усилителя 20, равным опорному напряжению посредством вызывания следящего действия при постоянной времени, определенной посредством электростатической емкости конденсатора C1 и значения сопротивления резистора R3 в схеме 204 DC обратной связи усилителя 20, который имеют канальные усилители 4 и 4a. Чтобы отличать от каждого этапа начиная с этапа S2 в нормальном режиме, показанном на фиг. 5, каждый этап в высокоскоростном режиме должен помечаться в качестве этапов S2'-S9'. Состояние переключателя на этапе 1 в случае высокоскоростного режима является идентичным состоянию в нормальном режиме.

[0044] В высо