Способ автоматического регулирования уровня выходного сигнала и система для его осуществления

Иллюстрации

Показать всеГруппа изобретений относится к области радиоэлектроники и системам управления и может быть использована для регулирования уровня выходного сигнала генераторов в широком частотном диапазоне. Техническим результатом является обеспечение гибкой настройки закона управления в регуляторе, а также обеспечение внесения корректирующих параметров. Система для реализации способа состоит из аналоговой и цифровой частей. Аналоговая часть включает блок управления уровнем, направленный ответвитель, диодный детектор, усилитель. Цифровая часть состоит из ПЛИС, АЦП и ЦАП. 2 н.п. ф-лы, 1 ил., 1 табл.

Реферат

Изобретение относится к области радиоэлектроники и системам управления и применяется для регулирования уровня выходного сигнала генераторов в широком частотном диапазоне.

Предшествующий уровень техники

Для регулирования уровня выходного сигнала применяются как схемы с аналоговым регулятором, реализуемым на базе операционного усилителя, так и схемы с цифровым регулятором, реализуемым программно на базе цифрового микроконтроллера. Решение на основе цифрового регулятора имеет такое преимущество, как программное изменение коэффициентов регулятора при изменении объекта управления, не требующее применения дополнительных внешних цепей. Для линейного изменения уровня выходного сигнала, определяемого в дБм, при линейном изменении опорного сигнала в цепи обратной связи системы управления применяются логарифмические детекторы, однако их частотный диапазон работы не покрывает рабочий диапазон разрабатываемых генераторов гармонического сигнала.

Известна аналоговая система АРМ со схожими возможностями, которую используют в генераторе Agilent серии PSG. В системе реализованы режимы разомкнутой петли, удержания управляющего сигнала и изменения коэффициентов регулятора (Agilent Technologies PSG Signal Generators Service Guide, Part Number: E8251-90259, USA, December 2003).

Известная система является аналоговой, поэтому обладает малой расширяемостью и гибкостью, кроме того, наличие множества компонентов удорожает и усложняет разработку платы, ручная настройка параметров регулятора, фиксированные коэффициенты регулятора.

Известна цифровая система коррекции квадратур для векторного генератора, которая содержит петлю обратной связи, состоящую из направленного ответвителя, детектора огибающей, аналого-цифрового преобразователя (АЦП), процессора, цифроаналогового преобразователя (ЦАП) и управляемого аттенюатора, для подстройки уровня сигнала перед квадратурным демодулятором. Другая цепочка оцифровывает I-составляющую сигнала модулирующего сигнала, и корректирует уровень выходного сигнала с помощью управляемого аттенюатора. Здесь цифровое управление аттенюатором не содержит каких-либо дополнительных режимов и служит для подстройки выходного уровня. Вычисление управляющего сигнала основано на сравнении оцифрованного сигнала с табличными значениями из памяти (US 6941118, МПК H03G3/20, опубл. 19.04.2002).

Сущность изобретения

Основной технической задачей, решаемой с помощью предложенных решений, является создание способа и системы для его осуществления, позволяющих более гибко настраивать закон управления в регуляторе, а также вносить какие-либо корректирующие параметры или корректирующие цепочки в цифровой части системы.

В отношении способа эта задача, в соответствии с изобретением, решается признаками, приведенными в п. 1 формулы изобретения. В отношении системы эта задача, в соответствии с изобретением, решается признаками, приведенными в п. 2 формулы изобретения.

Способ заключается в сравнении оцифрованного сигнала петли обратной связи с цифровым сигналом уставки.

В соответствии с изобретением СВЧ-сигнал преобразуют в низкочастотный, который поступает на АЦП, затем оцифрованный сигнал поступает в программируемую логическую интегральную схему (ПЛИС), обеспечивающую линейное изменение уровня выходного сигнала при линейном изменении уставки, где его сравнивают с уставкой, далее, по реализованному в ПЛИС закону управления, формируют управляющий сигнал и с помощью ЦАП преобразуют цифровой сигнал в аналоговый.

Система включает последовательно соединенные направленный ответвитель, диодный детектор и АЦП, образующие петлю обратной связи.

В соответствии с изобретением система снабжена ПЛИС, при этом выход ПЛИС соединен с входом ЦАП, выход которого соединен с входом блока управления уровнем, выход которого соединен с входом направленного ответвителя, выход которого соединен с входом диодного детектора, выход которого соединен с входом АЦП, выход которого соединен с входом ПЛИС.

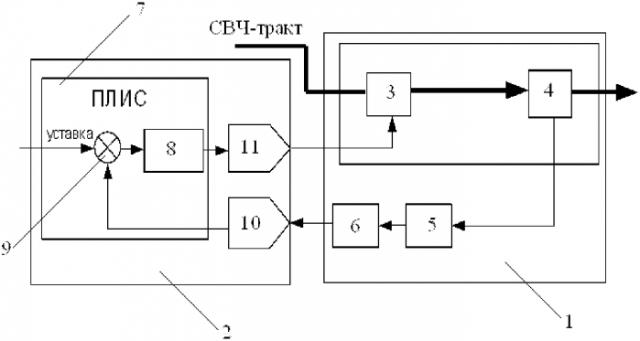

На чертеже представлена структурная система регулирования уровня с цифровым управлением.

Система состоит из аналоговой и цифровой частей 1 и 2. Аналоговая часть 1 включает блок управления уровнем 3, выход которого соединен с входом направленного ответвителя 4, выход которого соединен с входом диодного детектора 5, выход которого соединен с входом усилителя 6. Цифровая часть 2 состоит из ПЛИС 7, которая представлена как регулятор 8 и элемент рассогласования 9, АЦП 10 и ЦАП 11. Выход элемента рассогласования 9 соединен с входом регулятора 8, выход которого соединен с ЦАП 11, выход которого соединен с входом блока управления уровнем 3, а выход усилителя 6 соединен с входом АЦП 10, выход которого соединен с входом элемента рассогласования 8.

Осуществление изобретения

На вход аналоговой части 1 системы поступает СВЧ-сигнал с генератора. Затем этот сигнал с помощью блока управления уровнем 3 преобразуется в сигнал нужного уровня. С помощью направленного ответвителя 4 происходит передача в цепь обратной связи выходного сигнала высокой частоты. Далее с помощью диодного детектора 5 детектируют низкочастотную огибающую высокочастотного сигнала и передают на усилитель 6. Таким образом, на АЦП 10 поступает низкочастотный сигнал, где он сравнивается с некоторой, заданной в цифровом виде, уставкой. С выхода элемента рассогласования 9 сигнал ошибки поступает на регулятор 8, формирующий управляющий сигнал, который преобразуется из цифрового в аналоговый с помощью ЦАП 11. Вычислительным блоком в цифровой части схемы управления является ПЛИС 7, которая помимо осуществления вычислений также управляет АЦП 10 и ЦАП 11.

Так как уровень выходного сигнала, определяемый в дБм и в В, которые связаны соотношением,

,

где U1 - измеренное напряжение, а U0 - напряжение, принятое за опорное (при опорном уровне мощности в 1 мВт на номинальной нагрузке 50 Ом), то линейное изменение уставки приведет к линейному изменению уровня выходного сигнала, определяемого в В, но нелинейному, определяемому в дБм. Для обеспечения линейного изменения уровня выходного сигнала, определяемого в дБм, при линейном изменении уставки применяется первое программное преобразование, реализованное в ПЛИС 7. Чтобы получить зависимость уровня выходного сигнала, определяемого в дБм, от управляющего сигнала, определяемого в В, размыкают обратную связь. Экспериментально снимают зависимость, затем заполняют следующий массив значений. Экспериментальные измерения параметров для реализации первого программного преобразования представлены в таблице.

| Значение уставкиRef | Соответствующая уставке желаемая мощностьPжелаемая | Соответствующая уставке действительная мощностьPдействительная | Найденное реальное значение уставки, соответствующее желаемой мощностиRefпреоб |

| Ref(1) | Pжел(1) | Pдейств(1) | ... |

| Ref(2) | Pжел(2) | Pдейств(2) | ... |

| Ref(3) | Pжел(3) | Pдейств(3) | … |

Затем для каждой Pжел(k) находятся индексы (i) и (i+1), удовлетворяющие условию Pдейств(i)<Pжел(k)<Pдейств(i+1). После этого рассчитывается значение Refпреоб(k) методом линейной интерполяции по следующей формуле:

.

Таким образом, находят преобразованные значения для набора фиксированных значений уставки. Соответственно с помощью алгоритма первого программного преобразования анализируют заданное значение уставки, сравнивают его с имеющимися значениями в памяти ПЛИС, и в случае, если оно лежит между двумя значениями из памяти, методом линейной интерполяции находят нужное преобразованное значение. Увеличение числа точек повышает точность преобразования, что требует большего объема памяти для хранения массива значений. Для увеличения скорости вычислений в памяти хранятся не значения Ref и Refпреоб, а значения Ref и коэффициенты k и b, которые характеризуют прямую , которой аппроксимирован участок между Ref(i) и Ref(i+1). Второе программное преобразование выполняется аналогичным образом и служит для преобразования полученных отсчетов АЦП к той же величине, к которой преобразовывается значение уставки. Коэффициенты для преобразования рассчитывают после экспериментального получения соответствия значений АЦП и установленного значения уставки.

Функциональные возможности системы управления также включают в себя возможность программного управления выходом ЦАП - это удержание текущего управляющего сигнала, выключение управляющего сигнала за время, равное времени установки нового значения ЦАП, а также режим запоминания и восстановления управляющего сигнала.

1. Способ автоматического регулирования уровня выходного сигнала, заключающийся в сравнении оцифрованного сигнала петли обратной связи с цифровым сигналом уставки, отличающийся тем, что СВЧ-сигнал преобразуют в низкочастотный, который поступает на аналого-цифровой преобразователь (АЦП), затем оцифрованный сигнал поступает в программируемую логическую интегральную схему (ПЛИС), с помощью которой линейно изменяют уровень выходного сигнала при линейном изменении уставки, где сравнивают с уставкой, далее, по реализованному в ПЛИС алгоритму управления формируют управляющий сигнал и с помощью цифроаналогового преобразователя (ЦАП) преобразуют цифровой сигнал в аналоговый сигнал.

2. Система автоматического регулирования уровня выходного сигнала, включающая последовательно соединенные направленный ответвитель, диодный детектор и АЦП, образующие петлю обратной связи, отличающаяся тем, что система снабжена ПЛИС, при этом выход ПЛИС соединен с входом ЦАП, выход которого соединен с входом блока управления уровнем, который последовательно соединен с направленным ответвителем, диодным детектором и усилителем, выход которого соединен с входом АЦП, выход которого соединен с входом ПЛИС, представленной элементом рассогласования, выход которого соединен с регулятором, формирующим управляющий сигнал.