Устройство защиты от разрядов статического электричества выводов питания комплементарных моп (металл-окисел-полупроводник) интегральных схем на кремниевых пластинах с проводимостью n-типа

Иллюстрации

Показать всеИзобретение относится к полупроводниковой промышленности, в частности к интегральным микросхемам, и может быть использовано преимущественно для защиты от воздействия разрядов статического электричества выводов и шин питания кристаллов комплементарных МОП микросхем, изготовленных на кремниевых пластинах n-типа проводимости, в частности на пластинах КЭФ-4,5. Устройство защиты от разрядов статического электричества выводов питания комплементарных МОП (металл-окисел-полупроводник) интегральных схем на кремниевых пластинах с проводимостью n-типа содержит вывод контактной площадки (1) отрицательного питания (-Еп), подключенный к электродам внутренней схемы (10), катоду первого диода (7) и аноду второго диода (9), катод которого подключен к выводу контактной площадки (2) земли (▼) или положительного питания, который соединен с электродами внутренней схемы (10), при этом согласно изобретению устройство содержит МОП-транзистор (5), электрод подложки которого, сформированный «Р-карманом», подключен к аноду первого диода (7), затвор МОП-транзистора (5), являющийся верхней обкладкой емкости конденсатора (3) к шине земли и выводу контактной площадки (2), подключен через высокоомный резистор (8) к аноду первого диода (7), первый сток-истоковый электрод МОП-транзистора (5) через низкоомный резистор (4) подключен к выводу контактной площадки (2), второй исток-стоковый электрод МОП-транзистора (5) через низкоомный резистор (6) подключен к выводу контактной площадки (1) и электродам внутренней схемы (10). Технический результат изобретения заключается в том, чтобы исключить возникновение большой разности потенциалов (более 15 вольт) между шинами источников питания и земли и обеспечить быстрое пропускание тока (более 2 ампер) без повреждения подзатворного диэлектрика охранного шунтирующего транзистора при воздействии разряда статического электричества до 3500 вольт, при этом цепи протекания тока должны обладать минимально возможным сопротивлением. 6 з.п. ф-лы, 3 ил.

Реферат

Изобретение относится к полупроводниковой промышленности, в частности к интегральным микросхемам, и может быть использовано преимущественно для защиты от воздействия разрядов статического электричества выводов и шин питания кристаллов комплементарных МОП микросхем, изготовленных на кремниевых пластинах n-типа проводимости, в частности на пластинах КЭФ-4,5.

Основной проблемой защиты от воздействия разрядов статического электричества на шины питания МОП транзисторов, сформированные в кремниевых пластинах n-типа проводимости, в частности на пластинах КЭФ-4,5, является невозможность использования множества традиционных конструктивных решений, характерных для МОП-структур, сформированных в пластинах объемного кремния р-типа, таких как мощные n-канальные МОП-транзисторы, открывающиеся по переднему фронту разряда (так называемые «ESD-Clamp») ввиду того, что при воздействии разряда статического электричества отрицательной полярности на шины отрицательного питания в структурах на подложках n-типа проводимости в качестве «ESD-Clamp»-a приходится использовать р-канальный МОП-транзистор, не обеспечивающий эффективный слив избыточного заряда в подложку в силу инерционности основных носителей заряда «дырок».

Устройство должно обеспечивать быстрое пропускание тока (до двух ампер) разряда статического электричества без разрушения сток-истоковых областей и без пробоя подзатворного диэлектрика охранных элементов с тем, чтобы разность потенциалов между землей и шиной питания не успела превысить напряжение пробоя внутренних структурных элементов схемы (порядка 15 вольт).

Известно устройство защиты шин выводов источников питания интегральных микросхем от электростатических разрядов [1], содержащее р-МОП транзистор (так называемый «ESD-Clamp»), обеспечивающий протекание входного тока отрицательной полярности на шину земли, запирающийся по затвору достаточно сложной схемой задержки.

Однако, в связи с тем, что в момент воздействия разряда статического электричества шунтирование цепей питания осуществляется основными носителями, медленными «дырками», через р-канальный МОП-транзистор, такой способ защиты представляется малоэффективным.

Известно устройство защиты от статического электричества [2], в котором в качестве шунтирующего элемента используется n-p-n-биполярный транзистор с плавающим «n-карманом», сформированный между «многопальцевым» n-МОП-транзистором в р-подложке и глубоким донным «n-карманом», требующий применения специального оборудования для глубинной имплантации.

Известно также устройство защиты с помощью биполярного n-p-n-транзистора [3], в котором вывод земли связан с р+-базой, которая окружена р-карманом. Вывод питания связан с заглубленной n+областью, отделенной от р-кармана слаболегированной n-областью, таким образом формируется мощный объемный биполярный транзистор, шунтирующий разряд статического электричества. Но и эта конструкция требует применения специального оборудования для глубинной имплантации.

Наиболее близкими к заявленному изобретению являются устройства защиты цепей питания от статического электричества комплементарных МОП интегральных микросхем [4, 5], использующие в качестве шунтирующего элемента («ESD-Clamp»-a) n-канальный МОП-транзистор, который резко открывается по затвору под воздействием разряда статического электричества положительной полярности и запирается с достаточной временной задержкой специальной схемой управления.

Однако данные решения обладают рядом недостатков по отношению к заявленному изобретению:

- шунтирующий транзистор («ESD-Clamp») изготавливается в исходной подложке р-типа проводимости, т.е. эффективно срабатывает только при воздействии разряда положительной полярности,

- схемы управления запиранием шунтирующего транзистора по затвору достаточно громоздки, а с учетом необходимости их многократного размещения в кристалле между шинами питания и земли это приводит к неоправданному увеличению площади кристалла интегральной микросхемы.

Задача, на решение которой направлено заявленное изобретение, заключается в том, чтобы исключить возникновение большой разности потенциалов (более 15 вольт) между шинами источников питания и земли и обеспечить быстрое пропускания тока (более двух ампер) без повреждения подзатворного диэлектрика охранного шунтирующего транзистора при воздействии разряда статического электричества до 3500 вольт. При этом цепи протекания тока должны обладать минимально возможным сопротивлением.

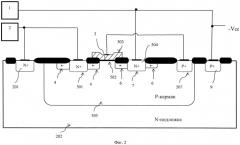

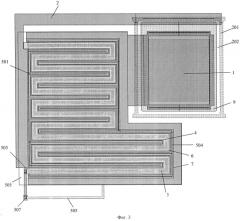

Данный технический результат достигается тем, что устройство защиты от разрядов статического электричества выводов питания комплементарных МОП (металл-окисел-полупроводник) интегральных схем на кремниевых пластинах с проводимостью n-типа содержит вывод контактной площадки (1), связанный низкоомной металлизированной шиной источника отрицательного питания (-Еп) с катодом диода (7) (Фиг. 2, 3) и анодом диода (9) (Фиг. 2, 3), площадью более 0,01 мм2, катод диода (9), сформированный кремниевой подложкой n--типа (Фиг. 3. 201, 202), подключен к выводу контактной площадки (2) земли (▼) (или положительного питания), анод диода (7), сформированный карманом Р-типа, подключен к электроду подложки n-канального МОП-транзистора (5) с плавающей подложкой (Фиг. 2, 3. 505, 506, 507) и через высокоомный резистор (8) того же кармана Р-типа, с сопротивлением более 15 кОм, к затвору n-канального МОП -транзистора (5) с плавающей подложкой (Фиг. 2, 3. 503), являющегося верхней обкладкой емкости конденсатора (3), номиналом не менее 1,5 пФ, на вывод контактной площадки (2) земли (▼) (или положительного питания). Первый сток-истоковый электрод (Фиг. 2, 3. 501) n-канального МОП-транзистора (5) с плавающей подложкой подключен через низкоомный резистор (4) к выводу контактной площадки (2) земли (▼) (или положительного питания), второй исток-стоковый электрод (Фиг. 2, 3. 504) подключен через низкоомный резистор (6) к выводу контактной площадки (1) источника отрицательного питания (-Еп). Область канала n-канального МОП-транзистора (5) с плавающей подложкой имеет ширину не менее 500 мкм, а подзатворный диэлектрик (Фиг. 2, 3. 502) над областью канала имеет толщину не более 20 нм, а над низколегированными областями сток-истоковых переходов имеет увеличенную толщину не менее 600 нм. Шины питания и земли подключены к соответствующим электродам внутренней схемы (10).

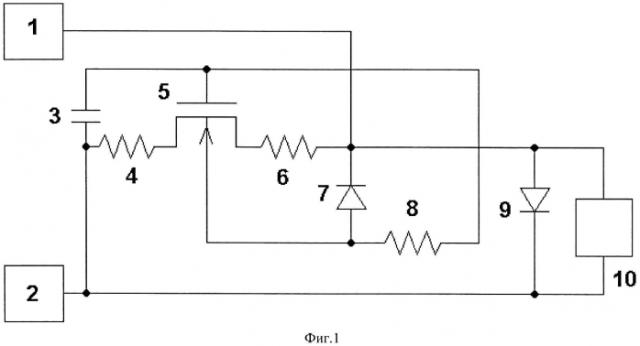

Предлагаемое изобретение поясняется чертежами, где:

- на Фиг. 1 изображена принципиальная схема устройства защиты от воздействия разрядов статического электричества выводов и шин питания кристаллов комплементарных МОП микросхем, изготовленных на кремниевых пластинах n-типа проводимости, в частности на пластинах КЭФ-4,5;

- на Фиг. 2 изображен разрез кремниевой структуры устройства защиты от воздействия разрядов статического электричества выводов и шин питания кристаллов комплементарных МОП микросхем, изготовленных на кремниевых пластинах n-типа проводимости, в частности на пластинах КЭФ-4,5;

- на Фиг. 3 изображен топологический чертеж устройства защиты от воздействия разрядов статического электричества выводов и шин питания кристаллов комплементарных МОП микросхем.

Устройство защиты от разрядов статического электричества выводов питания комплементарных МОП (металл-окисел-полупроводник) интегральных схем на кремниевых пластинах с проводимостью n-типа содержит вывод контактной площадки (1), связанный низкоомной металлизированной шиной источника отрицательного питания (-Еп) с катодом диода (7) (Фиг. 2, 3) и анодом диода (9) (Фиг. 2, 3), площадью более 0,01 мм2, катод диода (9), сформированный кремниевой подложкой n--типа (Фиг. 3. 201,202), подключен к выводу контактной площадки (2) земли (▼) (или положительного питания), анод диода (7), сформированный карманом Р-типа, подключен к электроду подложки n-канального МОП-транзистора (5) с плавающей подложкой (Фиг. 2, 3. 505, 506, 507) и через высокоомный резистор (8) того же кармана Р-типа, с сопротивлением более 15 кОм, к затвору n-канального МОП-транзистора (5) с плавающей подложкой (Фиг. 2, 3. 503), являющегося верхней обкладкой емкости конденсатора (3), номиналом не менее 1,5 пФ, на вывод контактной площадки (2) земли (▼) (или положительного питания). Первый сток-истоковый электрод (Фиг. 2, 3. 501) n-канального МОП-транзистора (5) с плавающей подложкой подключен через низкоомный резистор (4) к выводу контактной площадки (2) земли (▼) (или положительного питания), второй исток-стоковый электрод (Фиг. 2, 3. 504) подключен через низкоомный резистор (6) к выводу контактной площадки (1) источника отрицательного питания (-Еп). Область канала n-канального МОП-транзистора (5) с плавающей подложкой имеет ширину не менее 500 мкм, а подзатворный диэлектрик (Фиг. 2, 3. 502) над областью канала имеет толщину не более 20 нм, а над низколегированными областями сток-истоковых переходов имеет увеличенную толщину не менее 600 нм. Шины питания и земли подключены к соответствующим электродам внутренней схемы (10).

Устройство работает следующим образом.

При возникновении разряда статического электричества положительной полярности на выводе контактной площадки (1) обеспечивается протекание разрядного тока (до 2 ампер) на вывод контактной площадки (2) земли (▼) (или положительного питания) одновременно по прямосмещенному диоду Д (9) и через n-канального МОП транзистора (5) с плавающей подложкой, который открывается по переднему фронту разряда, т.к. его затвор заряжается через проходную емкость сток-затвор. При отрицательной полярности разряда ток протекает на шину земли через n-канального МОП-транзистора (5) с плавающей подложкой, т.к. его затвор заряжен положительно относительно истока и «Р-кармана» через проходную емкость конденсатора (3) (затвор - сток, подложка).

Литература

1. Power supply clamp circuitry for electrostatic discharge (ESD) protection // MALONEY TIMOTHY J [US]; KAN WILSON [US] // Патент на изобретение США №US6008970, дата приоритета 17.06.1998 г., кл. Н02Н 9/04, правообладатель INTEL CORP [US].

2. ESD protection circuit // CHU CHARLES Y [US]; WATT JEFFREY T [US] // Патент на изобретение США №US8217461, дата приоритета 09.07.2010 г., кл. H01L 23/62, правообладатель ALTERA CORP [US].

3. ESD protective transistor// WOLF HEINRICH [DE]; WILKENING WOLFGANG [DE]; METTLER STEPHAN [DE] // Патент на изобретение США №US6680493, дата приоритета 15.01.1999 г., кл. H01L 27/02; H01L 29/74, правообладатель FRAUNHOFER GES FORSCHUNG [DE], BOSCH GMBH ROBERT [DE].

4. Electrostatic discharge detection and clamp control circuit // MILLER WILLIAM E [US] // Патент на изобретение США №US5255146, дата приоритета 29.08.1991 г., кл. Н01L 21/822, H01L 27/04, Н02Н 9/04, правообладатель NATIONAL SEMICONDUCTOR CORP [US].

5. Active Vcc-to-Vss ESD clamp with hystersis for low supply chips // WU KE [US]; KWONG DAVID [US] // Патент на изобретение США №US6552886, дата приоритета 29.06.2000 г., кл. H01L 27/02; Н02Н 9/00, правообладатель PERICOM SEMICONDUCTOR CORP [US].

1. Устройство защиты от разрядов статического электричества выводов питания комплементарных МОП (металл-окисел-полупроводник) интегральных схем на кремниевых пластинах с проводимостью n-типа, содержащее вывод контактной площадки (1) отрицательного питания (-Еп), подключенный к электродам внутренней схемы (10), катоду первого диода (7) и аноду второго диода (9), катод которого подключен к выводу контактной площадки (2) земли (▼) или положительного питания, который соединен с электродами внутренней схемы (10), отличающееся тем, что содержит МОП-транзистор (5), электрод подложки которого, сформированный «Р-карманом», подключен к аноду первого диода (7), затвор МОП-транзистора (5), являющийся верхней обкладкой емкости конденсатора (3) к шине земли и выводу контактной площадки (2), подключен через высокоомный резистор (8) к аноду первого диода (7), первый сток-истоковый электрод МОП-транзистора (5) через низкоомный резистор (4) подключен к выводу контактной площадки (2), второй исток-стоковый электрод МОП-транзистора (5) через низкоомный резистор (6) подключен к выводу контактной площадки (1) и электродам внутренней схемы (10).

2. Устройство по п. 1, отличающееся тем, что ширина области канала МОП-транзистора (5) не менее 500 мкм.

3. Устройство по п. 2, отличающееся тем, что МОП-транзистор (5) является n-канальным с плавающей подложкой («Р-карман»).

4. Устройство по п. 1, отличающееся тем, что толщина конденсатора (3), сформированного подзатворным диэлектриком над областью канала, не более 20 нм, а над низколегированными областями сток-истоковых переходов - не менее 600 нм.

5. Устройство по п. 4, отличающееся тем, что емкость конденсатора (3) не менее 1,5 пФ.

6. Устройство по п. 1, отличающееся тем, что сопротивление высокоомного резистора (8) более 15 кОм, а сам резистор выполнен в том же «Р-кармане», что и МОП-транзистор (5).

7. Устройство по п. 1, отличающееся тем, что площадь второго диода (9) более 0,01 мм2.