Кремниевый мультиплексор

Иллюстрации

Показать всеИзобретение относится к оптоэлектронике и микроэлектронике и может быть использовано для считывания электрических сигналов в фотоприемных субмодулях для мозаичных фотоприемников, в частности в фотоприемниках на микроболометрах. Технический результат заключается в обеспечении возможности считывания не только в рамках полного кадра, но и фрагментами из полной матрицы ячеек считывания с заданными пользователем координатами и размерами; минимизации занимаемой блоком адресации площади кристалла ИС считывания фотосигналов, а также обеспечении возможности считывания фотосигналов фрагмента из полного кадра изображения с заданными координатами и размерами. Кремниевый мультиплексор состоит из вертикального и горизонтального регистров сдвига, системы строчной адресации на n-МОП-транзисторах, выходного узла, выходного усилителя и матрицы ячеек считывания, кроме того, в него введены дополнительный вертикальный регистр, дополнительный горизонтальный регистр, ключи передачи сигналов управления из вертикального регистра в дополнительный вертикальный регистр и из горизонтального регистра в дополнительный горизонтальный регистр, ОЗУ, компараторы, счетчики и дополнительные связи. 2 ил.

Реферат

Изобретение относится к оптоэлектронике и микроэлектронике и может быть использовано для считывания электрических сигналов в фотоприемных субмодулях для мозаичных фотоприемников, в частности в фотоприемниках на микроболометрах.

Известны интегральные схемы считывания фотоэлектрических сигналов (в дальнейшем именуемые «кремниевыми мультиплексорами»), относящиеся к классу интегральных схем считывания, архитектура которых основана на использовании отдельных шин считывания. Кремниевый мультиплексор, в котором при считывании фотосигналов строчные шины мультиплексируются через строчные ключи на единственную вертикальную шину, описан в работе А. Рогальского. Инфракрасные детекторы: Пер. с англ. / Под ред. А.В. Войцеховского. Новосибирск: Наука, 2003. Время накопления в таком мультиплексоре определяется длительностью импульса, подаваемого на входные транзисторы ячеек считывания мультиплексора в интервале времени между считыванием кадров инфракрасного (ИК) изображения. Время кадра равно сумме времени накопления и времени опроса кадра изображения. Однако в таком режиме частота кадров считываемых ИК изображений зависит от времени накопления, что усложняет средства предварительной обработки и управления выводом информации в автоматических системах и обычно неприемлемо для систем визуализации изображений, которые работают с постоянной кадровой частотой. При работе в широком диапазоне времен накопления фиксация кадровой частоты посредством выделения постоянного временного интервала, соответствующего максимальному времени накопления, приводит к снижению рабочих характеристик тепловизионной системы в целом за счет увеличения пассивного времени кадра в условиях, когда требуются минимальные значения времени накопления.

Известен кремниевый мультиплексор, который описан в работе Sauer D.J., Shallcross F.V., Hseuh F.L. et al. 640×480 MOS PtSi IR sensor // SPIE. 1991. 1540. P. 285. В этой интегральной схеме считывания фотосигналы с помощью строчных шин мультиплексируются через строчные буферные истоковые повторители на восемь вертикальных шин, а затем - на общий выход. В этом кремниевом мультиплексоре кроме режима, описанного в предыдущей работе, возможен режим работы, когда накопление ИК фотосигналов осуществляется в процессе опроса ячеек считывания кремниевого мультиплексора (Ткадра = константа).

Недостатком такого кремниевого мультиплексора является добавочный геометрический шум, вызванный неоднородностью характеристик строчных истоковых повторителей.

Известен также кремниевый мультиплексор, схема которого представлена в работе R.H. Nixon, S.E. Kemeny, C.O. Staller, E.R. Fossum. 256×256 CMOS Active Pixel Sensor Camera-on-a-Chip // IEEE International Solid-State Circuits Conference 1996. Этот кремниевый мультиплексор содержит запоминающие устройства на триггерах для задания полосы считывания, счетчики, декодеры, ряд буферных строчных усилителей, управляющий генератор и матрицу ячеек считывания форматом 256×256. Управляющими входами кремниевого мультиплексора являются импульс запуска "clk", команды управления режимом интегрирования, команда параллельной загрузки данных для определения времени интегрирования и параметров задания координат начала и конца считываемого фрагмента полного кадра. Выход кремниевого мультиплексора состоит из двух дифференциальных аналоговых каналов VS-OUT(сигнал) и VR-OUT(сброс). В этом кремниевом мультиплексоре считывание фотосигналов может осуществляться не только в рамках полного кадра, но и фрагментами из полной матрицы ячеек считывания 256×256 с заданными координатами и размерами. Время интегрирования устанавливается путем регулировки задержки между окончанием одного кадра и началом следующего.

Недостатком этого кремниевого мультиплексора является то, что он имеет сложную структуру и управление, состоит из большого количества транзисторов и поэтому использование этого устройства при считывании фотосигналов по вертикали в фотоприемниках, входящих в мозаичный фотоприемник, приводит к падению эффективности преобразования изображений в мозаичном фотоприемнике в целом. Предполагается, что стыковка фотоприемников с минимальной «слепой зоной» в мозаичном фотоприемнике производится по вертикали (Эффективность преобразования изображений - это отношение количества работающих фоточувствительных элементов в мозаичном фотоприемнике к сумме фоточувствительных элементов, потерянных в «слепых зонах» и работающих в мозаичном фотоприемнике).

Известен кремниевый мультиплексор, принятый за прототип, схема считывания которого приведена в работе А.И. Козлов, И.В. Марчишин, В.Н. Овсюк, В.В. Филиппова. Унифицированные кремниевые мультиплексоры 128×128 для инфракрасных фотоприемных устройств // Автометрия. 2006, том 42, №4.

Этот кремниевый мультиплексор состоит из вертикального и горизонтального регистров сдвига, системы строчной адресации на n-МОП-транзисторах, выходного узла, выходного усилителя и матрицы ячеек считывания, каждая ячейка которой содержит два ключа на n-МОП-транзисторах, затворы которых присоединены к адресным шинам, истоки ключей столбцов объединены со стоками строчных ключей, а истоки последних в каждой ячейке матрицы соединены с емкостью накопления и через входной n-МОП-транзистор с фотодетектором своей ячейки, на затворы входных n-МОП-транзисторов с внешнего источника поступает напряжение смещения Vcм, стоки ключей столбцов соединены с истоками n-МОП ключей системы строчной адресации, а стоки последних, объединяясь по четным и нечетным строкам, соединены с выходным узлом и далее с выходным усилителем, причем сканирование матрицы ячеек считывания осуществляется последовательно, строка за строкой, а при выбранной строке - перебором столбцов; выбранная строка через ключи ячейки и ключ системы строчной адресации соединена с выходным узлом, накопленный заряд с выбранной ячейки считывания поступает на общую шину считывания, формируется выходной сигнал, затем происходит перезарядка этой шины до напряжения сброса Vr.

Кремниевый мультиплексор, который принят за прототип, позволяет регулировать в широком диапазоне время накопления, в том числе и при фиксированном времени кадра, что обеспечивает увеличение динамического диапазона ИК фотоприемного устройства при высоком уровне входных токов. Кроме того, использование для коммутации ячеек матрицы считывания на общий выход только набора ключей значительно уменьшает геометрический шум за счет исключения из каналов считывания транзисторов истоковых повторителей и связанного с ними разброса параметров.

Однако этот кремниевый мультиплексор обладает существенным недостатком, а именно, считывание изображения может производиться только со всей матрицы ячеек считывания.

Техническим результатом изобретения является:

- расширение функциональных возможностей за счет обеспечения считывания не только в рамках полного кадра, но и фрагментами из полной матрицы ячеек считывания с заданными пользователем координатами и размерами;

- минимизация занимаемой блоком адресации площади кристалла ИС считывания фотосигналов;

- расширение области применения за счет возможности считывания фотосигналов фрагмента из полного кадра изображения с заданными координатами и размерами.

Технический результат изобретения достигается тем, что в кремниевый мультиплексор, состоящий из вертикального и горизонтального регистров сдвига, системы строчной адресации на n-МОП-транзисторах, выходного узла, выходного усилителя и матрицы ячеек считывания, каждая ячейка считывания которой содержит два ключа на n-МОП-транзисторах, затворы которых присоединены к адресным шинам, истоки ключей столбцов объединены со стоками строчных ключей, а истоки последних в каждой ячейке матрицы соединены с емкостью накопления и через входной n-МОП-транзистор с фотодетектором своей ячейки, на затворы входных n-МОП-транзисторов с внешнего источника поступает напряжение смещения Vcм, стоки ключей столбцов соединены с истоками n-МОП ключей системы строчной адресации, а стоки последних, объединяясь по четным и нечетным строкам, соединены с выходным узлом и далее с выходным усилителем, причем сканирование матрицы ячеек считывания осуществляют последовательно, строка за строкой, а при выбранной строке - перебором столбцов, выбранная строка через ключи ячейки и ключ системы строчной адресации соединена с выходным узлом, накопленный заряд с выбранной ячейки считывания поступает на общую шину считывания, затем происходит перезарядка шины считывания до напряжения сброса Vr, кроме того, в него введены дополнительный вертикальный и дополнительный горизонтальный регистры сдвига, ключи передачи сигналов управления с вертикального регистра на дополнительный вертикальный регистр и с горизонтального регистра на дополнительный горизонтальный регистр, четыре оперативных запоминающих устройства (ОЗУ) или набора ячеек памяти для записи адресов начала и конца считывания строк и столбцов фрагмента изображения, четыре компаратора и два счетчика, причем первое ОЗУ, в котором записан адрес первой строки считываемого фрагмента изображения, заданного пользователем, соединено с первым компаратором и вторым ОЗУ, в котором записан адрес последней строки считываемого фрагмента изображения, заданного пользователем, плюс одна строка, которое в свою очередь соединено со вторым компаратором, параллельные выходы этих компараторов соединены с первым счетчиком, счетный вход которого соединен с тактовыми входами вертикального и дополнительного вертикального регистров сдвига, а его информационный выход соединен с информационным входом вертикального регистра сдвига, выход первого компаратора соединяет через ключи управления параллельные выходы вертикального регистра сдвига с параллельными входами дополнительного вертикального регистра сдвига, выход второго компаратора соединяет через соответствующие ключи управления параллельные выходы вертикального регистра сдвига с соответствующими параллельными входами дополнительного вертикального регистра сдвига, параллельные выходы дополнительного вертикального регистра сдвига соединены с затворами адресных ключей строк матрицы кремниевого мультиплексора и с затворами n-МОП ключей системы строчной адресации, третье ОЗУ, в котором записан адрес первого столбца считываемого фрагмента изображения, заданного пользователем, соединено с третьим компаратором и четвертым ОЗУ, в котором записан адрес последнего столбца считываемого фрагмента изображения, заданного пользователем, плюс один столбец, которое в свою очередь соединено с четвертым компаратором, а параллельные выходы обоих этих компараторов соединены со вторым счетчиком, счетный вход которого соединен с тактовыми входами горизонтального и дополнительного горизонтального регистров сдвига, а его выход соединен с информационным входом горизонтального регистра сдвига, выход третьего компаратора соединяет через ключи управления параллельные выходы горизонтального регистра сдвига с параллельными входами дополнительного горизонтального регистра сдвига, выход четвертого компаратора соединяет через соответствующие ключи управления параллельные выходы горизонтального регистра сдвига с соответствующими параллельными входами дополнительного горизонтального регистра сдвига, параллельные выходы дополнительного горизонтального регистра сдвига соединены с затворами адресных ключей столбцов матрицы кремниевого мультиплексора.

Предлагаемый кремниевый мультиплексор за счет введения дополнительного вертикального регистра, дополнительного горизонтального регистра, ключей передачи сигналов управления из вертикального регистра в дополнительный вертикальный регистр и из горизонтального регистра в дополнительный горизонтальный регистр, ОЗУ, компараторов, счетчиков и дополнительных связей обеспечивает:

- считывание не только в рамках полного кадра, но и фрагментами матрицы ячеек считывания с заданными пользователем координатами и размерами,

- возможность минимизации занимаемой блоком адресации площади кристалла ИС считывания фотосигналов,

- расширение области применения благодаря возможности считывания, как полного кадра изображения, так и фрагмента из полного кадра с заданными координатами и размерами.

Сущность изобретения поясняется нижеследующим описанием и прилагаемыми фигурами.

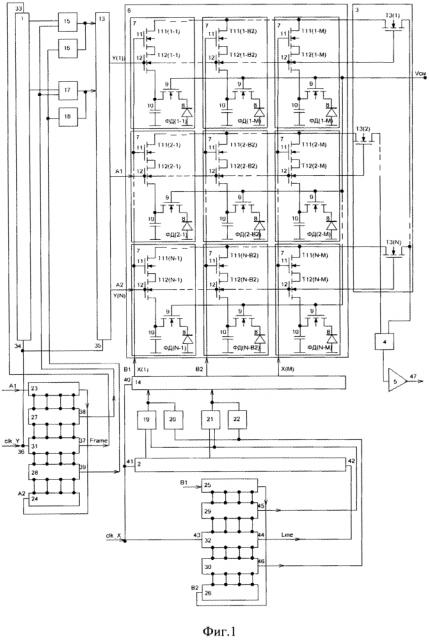

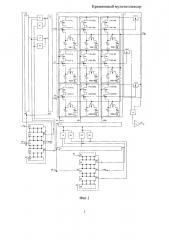

На фиг. 1 приведена функциональная схема кремниевого мультиплексора. На фиг. 2 приведен график зависимости количества МОП-транзисторов и числа управляющих шин в ячейке блока адресации от формата матрицы ячеек считывания для различных базовых схем блоков адресации кремниевых мультиплексоров, в частности на основе классических сдвиговых регистров, дешифраторов и реверсивных регистров сдвига.

На фиг. 1 приведена функциональная схема кремниевого мультиплексора, где 1 - вертикальный регистр сдвига; 2 - горизонтальный регистр сдвига; 3 - система строчной адресации на n-МОП транзисторах Т3(1) ÷ T3(N); 4 - выходной узел; 5 - выходной усилитель; 6 - матрица ячеек считывания кремниевого мультиплексора; 7 - ячейка считывания матрицы кремниевого мультиплексора; 8 - фотодетектор; 9 - входной n-МОП-транзистор; 10 - емкость накопления; 11 - ключ столбца (n-МОП-транзисторы Т11(1-1) ÷ T11(N-M)); 12 - ключ строки (n-МОП-транзисторы Т12(1-1) ÷ T12(N-M)); 13 - дополнительный вертикальный регистр сдвига; 14 - дополнительный горизонтальный регистр сдвига; 15, 16, 17, 18 - ключи передачи сигналов управления с вертикального регистра сдвига 1 на дополнительный вертикальный регистр сдвига 13; 19, 20, 21, 22 - ключи передачи сигналов управления с горизонтального регистра сдвига 2 на дополнительный горизонтальный регистр сдвига 14; 23 - ОЗУ для записи адреса (А1) начала считывания строк фрагмента изображения; 24 - ОЗУ для записи адреса (А2) конца считывания строк фрагмента изображения; 25 - ОЗУ для записи адреса (В1) начала считывания столбцов фрагмента изображения; 26 - ОЗУ для записи адреса (В2) конца считывания столбцов фрагмента изображения; 27, 28, 29, 30 - компараторы для формирования команды управления ключами 15, 16, 17, 18, 19, 20, 21 и 22; 31 - первый счетчик; 32 - второй счетчик; 33 - информационный вход вертикального регистра сдвига 1; 34 - тактовый вход вертикального регистра сдвига 1; 35 - тактовый вход дополнительного вертикального регистра сдвига 13; 36 - счетный вход первого счетчика 31; 37 - информационный выход первого счетчика 31; 38 - выход первого компаратора 27; 39 - выход второго компаратора 28; 40 - тактовый вход дополнительного горизонтального регистра сдвига 14; 41 - тактовый вход горизонтального регистра сдвига 2; 42 - информационный вход горизонтального регистра сдвига 2; 43 - счетный вход второго счетчика 32; 44 - информационный выход второго счетчика 32; 45 - выход третьего компаратора 29; 46 - выход четвертого компаратора 30; 47 - общий информационный выход кремниевого мультиплексора.

Схема считывания электрического сигнала кремниевого мультиплексора организована следующим образом (фиг. 1).

Первое ОЗУ 23, в котором из внешнего управляющего регистра сдвига записан адрес первой строки считываемого фрагмента изображения (А1), заданного пользователем, соединено с первым компаратором 27 и вторым ОЗУ 24. Во втором ОЗУ 24 также из внешнего управляющего регистра сдвига записан адрес последней строки считываемого фрагмента изображения (А2), заданного пользователем, плюс одна строка. Второе ОЗУ 24, в свою очередь, соединено со вторым компаратором 28. Параллельные выходы компараторов 27 и 28 соединены с первым счетчиком 31, счетный вход 36 которого соединен с тактовым входом 34 вертикального регистра сдвига 1 и с тактовым входом 35 дополнительного вертикального регистра сдвига 13. Информационный выход 37 первого счетчика 31 соединен с информационным входом 33 вертикального регистра сдвига 1. Выход 38 первого компаратора 27 соединяет через ключи управления 15, 17 параллельные выходы вертикального регистра сдвига 1 с соответствующими параллельными входами дополнительного вертикального регистра сдвига 13. Выход 39 второго компаратора 28 соединяет через соответствующие ключи управления 16, 18 параллельные выходы вертикального регистра сдвига 1 с соответствующими параллельными входами дополнительного вертикального регистра сдвига 13. Параллельные выходы дополнительного вертикального регистра сдвига 13 соединены с затворами адресных ключей строк 12 матрицы 6 кремниевого мультиплексора и с затворами n-МОП ключей T3(1) T3(N) системы строчной адресации 3. Третье ОЗУ 25, в котором из внешнего управляющего регистра сдвига записан адрес первого столбца считываемого фрагмента изображения (В1), заданного пользователем, соединено с третьим компаратором 29 и четвертым ОЗУ 26. В четвертом ОЗУ 26 также из внешнего управляющего регистра сдвига записан адрес последнего столбца считываемого фрагмента изображения (В2), заданного пользователем, плюс один столбец. Четвертое ОЗУ 26, в свою очередь, соединено с четвертым компаратором 30, а параллельные выходы обоих этих компараторов 29 и 30 соединены со вторым счетчиком 32. Счетный вход 43 второго счетчика 32 соединен с тактовым входом 40 дополнительного горизонтального регистра сдвига 14 и с тактовым входом 41 горизонтального регистра сдвига 2. Информационный выход 44 второго счетчика 32 соединен с информационным входом 42 горизонтального регистра сдвига 2. Выход 45 третьего компаратора 29 соединяет через ключи управления 19, 21 параллельные выходы горизонтального регистра сдвига 2 с соответствующими параллельными входами дополнительного горизонтального регистра сдвига 14. Выход 46 четвертого компаратора 30 соединяет через соответствующие ключи управления 20, 22 параллельные выходы горизонтального регистра сдвига 2 с соответствующими параллельными входами дополнительного горизонтального регистра сдвига 14. Параллельные выходы дополнительного горизонтального регистра сдвига 14 соединены с затворами адресных ключей столбцов 11 матрицы 6 кремниевого мультиплексора. Истоки ключей столбцов 11 объединены со стоками строчных ключей 12, а истоки последних в каждой ячейке считывания 7 матрицы 6 кремниевого мультиплексора соединены с емкостью накопления 10 и через входной n-МОП-транзистор 9 с фотодетектором 8 своей ячейки 7. На затворы входных n-МОП-транзисторов 9 с внешнего источника поступает напряжение смещения Vcм. Стоки ключей столбцов 11 соединены с истоками n-МОП ключей Т3(1) ÷ T3(N) системы строчной адресации 3 кремниевого мультиплексора, а стоки последних, объединяясь по четным и нечетным строкам, соединены с выходным узлом 4 кремниевого мультиплексора. Выходной узел 4 соединен далее с выходным усилителем 5, который имеет общий информационный выход 47 кремниевого мультиплексора.

Работа кремниевого мультиплексора осуществляется следующим образом (фиг. 1). Из внешнего управляющего регистра в ОЗУ 23 и 24 записываются адреса начала (А1) и конца (А2) считывания строк фрагмента изображения, т.е. в ОЗУ 23 записывается адрес первой строки фрагмента изображения, заданного пользователем для считывания по оси Y, в ОЗУ 24 записывается адрес последней строки фрагмента изображения, заданного пользователем для считывания по оси Y, плюс одна строка.

После включения первого счетчика 31 на его информационном выходе 37 сформируется сигнал Frame в тот момент, когда на всех параллельных выходах первого счетчика 31 установится комбинация из одних нулей. При нулевом состоянии первого счетчика 31 с его информационного выхода 37 на информационный вход 33 вертикального регистра сдвига 1 подается запускающий единичный сигнал Frame в виде цифровой "1" в бинарном представлении, так называемая логическая единица «1», который активирует работу вертикального регистра сдвига 1. В результате чего на выходе первой ячейки вертикального регистра сдвига 1 появится единичный цифровой сигнал (логическая единица «1»). Далее при поступлении каждого тактового импульса "clk_Y" на тактовый вход 34 вертикального регистра сдвига 1 происходит сдвиг единичного сигнала, сформированного в первой ячейке вертикального регистра сдвига 1 запускающим сигналом, от текущей ячейки к последующей ячейке. Одновременно с этим передвижением единичного сигнала по ячейкам вертикального регистра сдвига 1 первого счетчиком 31 осуществляется подсчет количества тактовых импульсов "clk_Y", поступающих на тактовый вход 34 вертикального регистра сдвига 1. Во время тактового импульса "clk_Y", при котором произойдет совпадение цифровых кодов, содержащихся в ОЗУ 23 и первом счетчике 31, компаратор 27 сформирует на своем выходе 38 единичный цифровой сигнал. Этот единичный цифровой сигнал, соответствующий адресу первой строки фрагмента изображения, заданного для считывания по оси "Y", поступая через ключи передачи сигналов управления 15 и 17, инициирует перенос бинарной информации с соответствующего выхода вертикального регистра сдвига 1 в параллельный вход дополнительного вертикального регистра сдвига 13. При этом он сформирует в соответствующей ячейке дополнительного вертикального регистра сдвига 13 единичный цифровой сигнал, который одновременно передастся и на соответствующий параллельный выход дополнительного вертикального регистра сдвига 13, образуя, тем самым, единичный цифровой сигнал адресации первой строки заданного для считывания фрагмента матрицы ячеек считывания 6. Таким образом, на матрицу ячеек считывания 6 поступает команда на начало сканирования кадра изображения по оси Y. Далее цифровой код в счетчике 31 при поступлении на его счетный вход 36 каждого нового тактового импульса "clk_Y" будет увеличиваться на одну единицу. Одновременно каждый новый тактовый импульс "clk_Y", поступающий на тактовый вход 35 дополнительного вертикального регистра сдвига 13, будет осуществлять перенос единичного цифрового сигнала, содержащегося в ячейках дополнительного вертикального регистра сдвига 13, и соответственно осуществлять последовательную построчную адресацию по оси "Y" в рамках заданного фрагмента. Так будет происходить при поступлении каждого нового тактового импульса "clk_Y" до тех пор, пока цифровой код, содержащийся в счетчике 31, не станет равным цифровому коду, записанному в ОЗУ 24 и соответствующему адресу последней строки заданного фрагмента плюс одна строка. Далее компаратор 28 сформирует на своем выходе 39 единичный цифровой сигнал, который через ключи 16 и 18 инициирует сброс всей цифровой информации, находящейся в каждой ячейке дополнительного вертикального регистра сдвига 13, в нулевое состояние, и на всех параллельных выходах дополнительного вертикального регистра сдвига 13 сформируется нулевой сигнал адресации. Таким образом, на все строки матрицы ячеек считывания 6 поступят нулевые сигналы адресации и сканирование по оси "Y" заданного фрагмента из полного кадра изображения прекратится.

В ОЗУ 25 из внешнего управляющего регистра записывается адрес первого столбца считываемого фрагмента изображения, заданного пользователем, а в ОЗУ 26 также из внешнего управляющего регистра записывается адрес последнего столбца фрагмента изображения, заданного пользователем для считывания по оси X, плюс один столбец.

После включения второго счетчика 32 на информационном выходе 44 сформируется сигнал Line в тот момент, когда на всех параллельных выходах второго счетчика 32 установится комбинация из одних нулей. При нулевом состоянии второго счетчика 32 с его информационного выхода 44 на информационный вход 42 горизонтального регистра сдвига 2 подается запускающий единичный сигнал Line в виде цифровой "1" в бинарном представлении, так называемая логическая единица «1», который активирует работу горизонтального регистра сдвига 2. В результате чего на выходе первой ячейки горизонтального регистра сдвига 2 появится единичный цифровой сигнал (логическая единица «1»). Далее при поступлении каждого импульса "clk_X" на тактовый вход 41 горизонтального регистра сдвига 2 происходит сдвиг единичного сигнала, сформированного в первой ячейке вертикального регистра сдвига 2 запускающим единичным сигналом, от текущей ячейки к последующей ячейке. Второй счетчик 32 осуществляет в это время подсчет количества тактовых импульсов "clk_X", поступающих на тактовый вход 41 горизонтального регистра сдвига 2. Во время тактового импульса "clk_X", при котором произойдет совпадение цифровых кодов, содержащихся в ОЗУ 25 и втором счетчике 32, компаратор 29 сформирует на своем выходе 45 единичный цифровой сигнал. Этот цифровой сигнал, соответствующий адресу первого столбца фрагмента изображения, заданного для считывания по оси "X", инициирует перенос бинарной информации из горизонтального регистра сдвига 2 в дополнительный горизонтальный регистр сдвига 14. При этом единичный цифровой сигнал с соответствующего выхода горизонтального регистра сдвига 2, поступая на соответствующий параллельный вход дополнительного горизонтального регистра сдвига 14 через ключи передачи сигналов управления 19, 21, сформирует в соответствующей ячейке дополнительного горизонтального регистра сдвига 14 единичный цифровой сигнал. Одновременно единичный цифровой сигнал передастся на соответствующий параллельный выход дополнительного горизонтального регистра сдвига 14, образуя, тем самым, единичный цифровой сигнал - команду «начала считывания» столбцов фрагмента матрицы ячеек считывания 6. Таким образом, на матрицу ячеек считывания 6 мультиплексора поступит сигнал адресации по оси "X", соответствующий адресу первого столбца заданного фрагмента кадра изображения. Далее цифровой код во втором счетчике 32 при поступлении на его счетный вход 43 каждого нового тактового импульса "clk_X" будет увеличиваться на одну единицу. Одновременно каждый новый тактовый импульс "clk_X", поступающий на тактовый вход 40 дополнительного горизонтального регистра сдвига 14, будет осуществлять перенос единичного цифрового сигнала, содержащегося в ячейках дополнительного горизонтального регистра сдвига 14, и соответственно осуществлять последовательную, постолбцовую адресацию по оси "X" в рамках заданного фрагмента. Это будет происходить при поступлении каждого нового тактового импульса "clk_X" до тех пор, пока цифровой код, содержащийся во втором счетчике 32, не станет равным цифровому коду, записанному в ОЗУ 26 и соответствующему адресу последнего столбца заданного фрагмента, плюс один столбец. Тогда компаратор 30 сформирует единичный цифровой сигнал на своем выходе 46, который через управляющие ключи 20 и 22 инициирует сброс всей цифровой информации, находящейся в каждой ячейке дополнительного горизонтального регистра сдвига 14, в нулевое состояние. На всех параллельных выходах дополнительного горизонтального регистра сдвига 14 сформируется нулевой сигнал адресации, т.е. на все столбцы матрицы ячеек считывания 6 поступят нулевые сигналы адресации и сканирование по оси "X" заданного фрагмента полного кадра изображения прекратится.

Сканирование матрицы ячеек считывания 6, каждая ячейка которой 7 состоит из фотодетектора 8, входного n-МОП-транзистора 9, емкости накопления 10, ключа столбцов 11 и ключа строк 12, осуществляется последовательно, строка за строкой, а при выбранной строке - перебором столбцов. С помощью входного транзистора 9, на затвор которого с внешнего источника поступает напряжение Vcм, устанавливается напряжение смещения Vcм на фотоприемнике 8. Фототок интегрируется на емкости накопления 10. Предположим, была выбрана первая строка, тогда единичный цифровой сигнал (логическая единица «1»), приложенный к общей шине первой строки, откроет все ключи 12 первой строки (n-МОП-транзисторы Т12(1-1) ÷ Т12(1-М) фиг. 1). Появление логической единицы «1» на выбранном j-м столбце откроет ключи 11 j-ого столбца (n-МОП-транзисторы T11(1-j) ÷ T11(N-j)). В результате этого фотодетектор 8 ФД(1j) оказывается соединенным с шиной считывания первой строки через открытые ключи первой строки, включая n-МОП-транзистор T12(1-j) и через открытые ключи столбца j, включая n-МОП-транзистор T11(1-j), т.е. накопленный в данной ячейке заряд сбрасывается на указанную шину. Через открытый строчный ключ Т3(1), входящий в систему строчной адресации 3 на n-МОП-транзисторах Т3(1) ÷ T3(N), с помощью которой осуществляют последовательную коммутацию ячеек считывания на общий выход, накопленный заряд выбранной ячейки поступает на общую шину считывания, затем происходит перезарядка шины до напряжения сброса Vr. Сигнал с общей шины проходит далее через выходной узел 4, участвующий в управлении временем накопления, усиливается по мощности на выходном усилителе 5 и поступает на общий выход 47 кремниевого мультиплексора. Выходной усилитель 5 «нагружается» на внешнее сопротивление или источник тока (относительно напряжения питания) и образует, таким образом, истоковый повторитель. Для детектирования сигнального заряда необходимо:

- установить с помощью входного n-МОП-транзистора 9 напряжение смещения Vcм на фотодиоде 8;

- предварительно зарядить шину считывания до напряжения сброса Vr (для этого подается с выходного узла 4 короткий импульс Фr);

- измерить потенциал заряженной шины считывания (U1);

- подать единичный цифровой сигнал (логическую единицу «1») на соответствующий столбец;

- измерить сигнальное напряжение на шине считывания (U2).

На выходе кремниевого мультиплексора 47 при использовании внешней схемы двойной коррелированной выборки, позволяющей устранить kТС - шум, фиксируется выходной сигнал Uвых=(U2)-(U1).

В рамках предложенной схемы считывания фотосигналов можно реализовать и режим "электронного затвора" (Ткадра = константа) и режим "мгновенного фотоснимка" (Ткадра = Тсчитывания кадра + Тнакопления).

Схема блока адресации (БА), использованная в кремниевом мультиплексоре - прототипе, является классической схемой КМОП-регистра сдвига, которая формирует импульсы адресации без паузы, представлена в книге С. Мурога, Системное проектирование сверхбольших интегральных схем, изд. «Мир», М., 1985, стр. 258. На каждом спадающем фронте последовательности импульсов Ф1 (одного из тактовых сигналов) происходит сдвиг на одну ячейку единичного цифрового сигнала (его высокого уровня, т.е. логической единицы «1»), поданного на информационный вход регистра сдвига. Ячейка БА с использованием классического регистра сдвига состоит из восьми МОП-транзисторов, количество МОП-транзисторов в ячейке не зависит от формата матрицы ячеек считывания (фиг. 2).

В функциональной схеме БА на основе дешифратора (ДШ), описанной в работе R.H. Nixon, S.E. Kemeny, C.O. Staller, E.R. Fossum. 256×256 CMOS Active Pixel Sensor Camera-on-a-Chip // IEEE International Solid-State Circuits Conference 1996, количество МОП-транзисторов в ячейке БА зависит от формата матрицы ячеек считывания (фиг. 2).

Больше того, схема адресации на основе ДШ требует применения буферных усилителей, так называемых "обострителей фаз", на каждом адресном выходе ДШ, т.е. необходимо буферирование каждого из адресных выходов, что приводит к использованию еще большего количества МОП-транзисторов.

В случае применения в предлагаемом техническом решении реверсивных регистров сдвига появляется возможность инверсии порядка считывания элементов кадра изображения, как в полнокадровом режиме, так и в режиме считывания фрагментов кадра. В БА на основе реверсивного сдвигового регистра (Патент РФ на изобретение №2522306 «Сдвиговый регистр», МПК G11C 19/00, опубликован 10.07.2014, Патент РФ на изобретение №2530271 «Сдвиговый регистр», МПК G11C 19/00, опубликован 10.10.2014), отсутствует зависимость количества МОП-транзисторов в ячейке БА от формата матрицы ячеек считывания, но в ячейке реверсивного регистра сдвига используется большее количество МОП-транзисторов (фиг. 2).

На графике фиг. 2 представлена зависимость количества МОП-транзисторов и числа управляющих шин в ячейке БА кремниевого мультиплексора (фиг. 1) от формата матрицы ячеек считывания по одному из направлений переноса информации (по оси Y в рассматриваемом примере). БА кремниевого мультиплексора (фиг. 1) по оси Y состоит из двух регистров сдвига (вертикального регистра сдвига 1 и дополнительного вертикального регистра сдвига 13) и переключателей между ними 15÷18. Таким образом, в ячейке БА кремниевого мультиплексора (фиг. 1) на основе классического регистра сдвига будет 18 МОП-транзисторов и 4 управляющих шины, а на основе реверсивного сдвигового регистра (Патент РФ на изобретение №2530271 «Сдвиговый регистр», МПК G11C 19/00, опубликован 10.10.2014) - минимум 22 МОП-транзистора и 6 тактовых шин.

Блоки адресации (БА) на основе регистров сдвига имеют минимальное количество управляющих шин в ячейке по сравнению со схемами дешифраторов: от 4-6 управляющих шин до 2-3 управляющих шин (при формировании инверсных управляющих сигналов непосредственно в каждой ячейке БА) для классического и реверсивного регистров сдвига соответственно.

Кремниевый мультиплексор, состоящий из вертикального и горизонтального регистров сдвига, системы строчной адресации на n-МОП-транзисторах, выходного узла, выходного усилителя и матрицы ячеек считывания, каждая ячейка считывания которой содержит два ключа на n-МОП-транзисторах, затворы которых присоединены к адресным шинам, истоки ключей столбцов объединены со стоками строчных ключей, а истоки последних в каждой ячейке матрицы соединены с емкостью накопления и через входной n-МОП-транзистор с фотодетектором своей ячейки, на затворы входных n-МОП-транзисторов с внешнего источника поступает напряжение смещения Vcм, стоки ключей столбцов соединены с истоками n-МОП ключей системы строчной адресации, а стоки последних, объединяясь по четным и нечетным строкам, соединены с выходным узлом и далее с выходным усилителем, причем сканирование матрицы ячеек считывания осуществляют последовательно, строка за строкой, а при выбранной строке - перебором столбцов, выбранная строка через ключи ячейки и ключ системы строчной адресации соединена с выходным узлом, накопленный заряд с выбранной ячейки считывания поступает на общую шину считывания, затем происходит перезарядка шины считывания до напряжения сброса Vr, отличающийся тем, что в него введены дополнительный вертикальный и дополнительный горизонтальный регистры сдвига, ключи передачи сигналов управления с вертикального регистра на дополнительный вертикальный регистр и с горизонтального регистра на дополнительный горизонтальный регистр, четыре оперативных запоминающих устройства (ОЗУ) или набора ячеек памяти для записи адресов начала и конца считывания строк и столбцов фрагмента изображения, четыре компаратора и два счетчика, причем первое ОЗУ, в котором записан адрес первой строки считываемого фрагмента изображения, заданного пользователем, соединено с первым компаратором и вторым ОЗУ, в котором записан адрес последней строки считываемого фрагмента изображения, заданного пользователем, плюс одна строка, которое в свою очередь соединено со вторым компаратором, а параллельные выходы этих компараторов соединены с первым счетчиком, счетный вход которого соединен с тактовыми входами вертикального и дополнительного вертикального регистров сдвига, а его информационный выход соединен с информационным входом вертикального регистра сдвига, выход первого компаратора соединяет через ключи управления параллельные выходы вертикального регистра сдвига с параллельными входами дополнительного вертикального регистра сдвига, выход второго компаратора соединяет через соответствующие ключи управления параллельные выходы вертикального регистра сдвига с соответствующими параллельными входами дополнительного вертикального регистра сдвига, параллельные выходы дополнительного вертикального регистра сдвига соединены с затворами адресных ключей строк матрицы ячеек считывания кремниевого мультиплексора и с затворами n-МОП ключей системы строчной адресации; третье ОЗУ, в котором записан адрес первого столбца считываемого фрагмента изображения, заданного пользователем, соединено с третьим компаратором и четвертым ОЗУ, в котором записан адрес последнего столбца считываемого фрагмента изображения, заданного пользователем, плюс один столбец, которое в свою очередь соединено с четвертым компаратором, а параллельные выходы обоих этих компараторов соединены со вторым счетчиком, счетный вход которого соединен с тактовыми входами горизонтального и дополнительного горизонтального регистров сдвига, а его информационный выход соединен с информационным входом горизонтального регистра сдвига, выход третьего компаратора соединяет через соответствую