Устройство деления модулярных чисел

Иллюстрации

Показать всеИзобретение относится к вычислительным модулярным системам и предназначено для выполнения деления чисел, представленных в системе остаточных классов (СОК). Технический результат – обеспечение возможности деления с отрицательными числами, представленными в системе остаточных классов. Устройство деления модулярных чисел содержит вход тактового импульса, вход глобального сброса, вход делимого, вход делителя, элемент ИЛИ, блок вычисления позиционных характеристик, блок уточнения аппроксимационного ряда, блок вывода частного и выход вывода частного. При этом блок вычисления позиционных характеристик содержит регистр делимого, n инверторов делимого, n регистров хранения модуля pi, где i=1,…,n, n регистров хранения коэффициента ki, n сумматоров делимого, n умножителей отрицательного делимого, n умножителей положительного делимого, сумматор значения F(A), сумматор значения F(-A), регистр хранения значения F (-А), регистр хранения значения F(A), регистр делителя, n инверторов делителя, n регистров хранения модуля pi, n регистров хранения коэффициента ki, n сумматоров делителя, n умножителей отрицательного делителя, n умножителей положительного делителя, сумматор значения F(B), сумматор значения F(-B), регистр хранения значения F(-B), регистр хранения значения F(B), элемент XOR, мультиплексор делимого, мультиплексор делителя, блок сравнения. Блок уточнения аппроксимационного ряда содержит регистр сдвига, счетчик, регистр хранения , регистр хранения уменьшаемого, мультиплексор выбора уменьшаемого, инвертор, память хранения степеней «2» в СОК, сумматор, мультиплексор выбора следующего уменьшаемого, элемент НЕ, элемент И. Блок вывода частного состоит из элемента ИЛИ, элемента задержки, удерживающего регистра, n регистров хранения остатка по модулю pi, n сумматоров по модулю pi, n демультиплексоров по модулю pi, n регистров хранения суммы по модулю pi, n инверторов, n регистров хранения модуля pi, n сумматоров, n регистров хранения обратного значения суммы по модулю n мультиплексоров выбора суммы, удерживающего регистра знака, регистра хранения суммы в СОК, регистра хранения значения «1», регистра хранения значения «-1», мультиплексора равенства абсолютных величин делимого и делителя, мультиплексора вывода частного, регистра хранения частного. 4 ил.

Реферат

Изобретение относится к вычислительным модулярным системам и предназначено для выполнения деления чисел, представленных в системе остаточных классов (СОК).

В СОК целое число представляется в виде остатков отделения на набор модулей, а арифметические операции над числами заменяются на операции над остатками. Выполнение операций происходит параллельно без межразрядных переносов, что позволяет очень быстро реализовать сложение, вычитание и умножение. Однако операция деления является трудоемкой и требует разработки новых архитектур вычисления и аппаратных реализаций.

Известна нейронная сеть основного деления модулярных чисел (патент па изобретение RU №2400813, опубликован 27.09.2010). Недостатком устройства является большой объем оборудования и невозможность работы с отрицательными числами. Известная нейронная сеть предназначена для деления модулярных чисел в случае, когда в качестве делителя используется целое положительное число, попарно простое с модулями СОК p1,p2,…,pn, либо целое положительное число, представляющее собой произведение чисел, попарно простых с pi. Для выполнения этого условия возникает необходимость нахождения приблизительного делителя путем использования обобщенной позиционной системы счисления (ОПСС). Для нахождения приблизительного делителя необходимо дополнительное оборудование и время.

Известно устройство для основного деления модулярных чисел в формате системы остаточных классов (патент на изобретение RU №2559772, опубликован 10.08.2015). Недостатком данного устройства является большой объем оборудования и необходимость перевода чисел из основной СОК во вспомогательную СОК.

Наиболее близким к данному устройству, выбранным в качестве прототипа, является устройство для основного деления модулярных чисел (патент на изобретение RU №2559771, опубликован 10.08.2015), содержащее входы делимого и делителя (обозначенные в прототипе как входные шины делимого и делителя), которые подают делимое непосредственно, а делитель через схему умножения, либо через мультиплексор на вход схемы сравнения модулярных чисел (в данном изобретении функции схемы сравнения выполняет блок вычисления позиционных характеристик), выходы которой реализуют вычислительную модель а<b, a>b или а=b, где а - делимое, b - делитель; управляющие выходы схемы сравнения а<b, а>b соединены со схемой управления, выходы которой соединены с адресными входами мультиплексора, входами управления счетчика, регистров сдвига и хранения, сумматоров частного, делителя и вычитателя, а также с одним из входов ключей, вторые входы которых соединены с выходом памяти, входы которой соединены с регистром сдвига, а выход а=b схемы сравнения соединен со входом сумматора частного, помещая в пего «единицу», а информационные выходы соединены со схемами сумматоров делимого и делителя, выходы которого соединены регистром сдвига влево, выход которого соединен со счетчиком определения высшей степени аппроксимационного ряда частного, выход счетчика соединен с адресными входами памяти, выходы которой через схему ключей и запрет подают на вход сумматора частного степень члена ряда, входящего в уточненный член ряда частного и на вход схемы умножения высшей степени ряда на делитель, выход которой через мультиплексор соединен со схемой сравнения, выходы которой соединены с сумматорами делимого и делителя; выход сумматора делителя соединен со входом регистра сдвига вправо, выход которого соединен со схемой вычитателя, на второй вход которого подключен выход сумматора делимого, выход вычитателя соединен с регистром хранения остатка при вычитании из делимого членов ряда частного, выход которого соединен через сумматор делимого с вычитателем, выход которого соединен со схемой запрета, выходы которой соединены с регистром хранения остатка при вычитании из делимого членов ряда частного и схемой сумматора частного.

Недостатком данного изобретения является ограниченные функциональные возможности, связанные с невозможностью работы с отрицательными числами.

Техническим результатом является расширение функциональных возможностей, а именно возможность выполнения деления с отрицательными числами, представленными в системе остаточных классов.

Данный технический результат достигается тем, что в устройство деления модулярных чисел, содержащее входы делимого и делителя, выход вывода частного, блок вычисления позиционных характеристик, регистр сдвига, счетчик, память хранения степеней «2» в системе остаточных классов (СОК), причем первый выход регистра сдвига соединен одновременно с первым входом счетчика и первым входом памяти хранения степеней «2» в СОК, второй вход которой соединен с первым выходом счетчика, введены входы тактового импульса и глобального сброса, элемент ИЛИ, блок уточнения аппроксимационного ряда, блок вывода частного, вход тактового импульса соединен с третьим входом блока вычисления позиционных характеристик, с первым входом блока уточнения аппроксимационного ряда и пятым входом блока вывода частного, первый выход которого соединен со вторым входом элемента ИЛИ, первый вход которого соединен со входом глобального сброса; выход элемента ИЛИ соединен с четвертым входом блока вычисления позиционных характеристик, вторым входом блока уточнения аппроксимационного ряда и четвертым входом блока вывода частного, второй выход которого является выходом вывода частного, шестой и седьмой входы блока вывода частного соединены соответственно с первым и вторым выходами блока уточнения аппроксимационного ряда, третий и четвертый входы которого соединены с пятым и четвертым выходами блока вычисления позиционных характеристик, первый, второй и третий выходы которого соединены с первым, вторым и третьим входами блока вывода частного, а первый и второй входы блока вычисления позиционных характеристик соединены с входом делимого и входом делителя соответственно, причем блок позиционных характеристик состоит из регистра делимого, регистра делителя, n инверторов делимого блока вычисления позиционных характеристик, где n - количество модулей СОК, n инверторов делителя блока вычисления позиционных характеристик, 2n регистров хранения модуля pi; где i=1,…,n, 2n регистров хранения коэффициента ki, n сумматоров делимого блока вычисления позиционных характеристик, n сумматоров делителя блока вычисления позиционных характеристик, n первых умножителей делимого, n вторых умножителей делимого, n первых умножителей делителя, n вторых умножителей делителя, сумматора значения F (А), сумматора значения F (-А), сумматора значения F (В), сумматора значения F(-B), регистра хранения значения F (А), регистра хранения значения F (-А), регистра хранения значения F (В), регистра хранения значения F (-В), элемента XOR, мультиплексора делимого, мультиплексора делителя и блока сравнения, где первый вход регистра делимого связан со входом делимого, второй и третий входы связаны со входом тактового импульса и выходом элемента ИЛИ соответственно, 1-й выход соединен со входом 1-го инвертора делимого блока вычисления позиционных характеристик и вторым входом 1-го умножителя положительного делимого, первый вход которого связан с выходом регистра хранения коэффициента k1, подключенного одновременно ко второму входу 1-го умножителя отрицательного делимого, первый вход которого соединен с выходом 1-го сумматора делимого блока вычисления позиционных характеристик, на третий вход которого постоянно подается значение логической единицы, второй вход соединен с выходом 1-го инвертора делимого блока вычисления позиционных характеристик, первый вход подключен к выходу регистра хранения модуля р1, 2-й выход регистра делимого соединен со входом 2-го инвертора делимого блока вычисления позиционных характеристик и вторым входом 2-го умножителя положительного делимого, первый вход которого связан с выходом регистра хранения коэффициента k2, подключенного одновременно ко второму входу 2-го умножителя отрицательного делимого, первый вход которого соединен с выходом 2-го сумматора делимого блока вычисления позиционных характеристик, на третий вход которого постоянно подается значение логической единицы, второй вход соединен с выходом 2-го инвертора делимого блока вычисления позиционных характеристик, первый вход подключен к выходу регистра хранения модуля р2, аналогичные связи по остальным выходам регистра делимого, наконец, n-й выход регистра делимого соединен со входом n-го инвертора делимого блока вычисления позиционных характеристик и вторым входом n-го умножителя положительного делимого, первый вход которого связан с выходом регистра хранения коэффициента kn, подключенного одновременно ко второму входу n-го умножителя отрицательного делимого, первый вход которого соединен с выходом n-го сумматора делимого блока вычисления позиционных характеристик, на третий вход которого постоянно подается значение логической единицы, второй вход соединен с выходом n-го инвертора делимого блока вычисления позиционных характеристик, первый вход подключен к выходу регистра хранения модуля pn, выход 1-го умножителя положительного делимого подключен к 1-му входу сумматора значения F (А), выход 2-го умножителя положительного делимого подключен ко 2-му входу сумматора значения F (А), и так далее, наконец, выход n-го умножителя положительного делимого подключен к n-му входу сумматора значения F (А), выход 1-го умножителя отрицательного делимого подключен к 1-му входу сумматора значения F(-A), выход 2-го умножителя отрицательного делимого подключен ко 2-му входу сумматора значения F(-A), и так далее, наконец, выход n-го умножителя отрицательного делимого подключен к n-му входу сумматора значения F (-А), первый вход регистра делителя связан со входом делителя, второй и третий входы связаны со входом тактового импульса и выходом элемента ИЛИ соответственно, 1-й выход соединен со входом 1-го инвертора делителя блока вычисления позиционных характеристик и вторым входом 1-го умножителя положительного делителя, первый вход которого связан с выходом регистра хранения коэффициента k1, подключенного одновременно ко второму входу 1-го умножителя отрицательного делителя, первый вход которого соединен с выходом 1-го сумматора делителя блока вычисления позиционных характеристик, на третий вход которого постоянно подается значение логической единицы, второй вход соединен с выходом 1-го инвертора делителя блока вычисления позиционных характеристик, первый вход подключен к выходу регистра хранения модуля 2-й выход регистра делителя соединен со входом 2-го инвертора делителя блока вычисления позиционных характеристик и вторым входом 2-го умножителя положительного делителя, первый вход которого связан с выходом регистра хранения коэффициента к2, подключенного одновременно ко второму входу 2-го умножителя отрицательного делителя, первый вход которого соединен с выходом 2-го сумматора делителя блока вычисления позиционных характеристик, па третий вход которого постоянно подается значение логической единицы, второй вход соединен с выходом 2-го инвертора делителя блока вычисления позиционных характеристик, первый вход подключен к выходу регистра хранения модуля р2, аналогичные связи по остальным выходам регистра делителя, наконец, n-й выход регистра делителя соединен со входом n-го инвертора делителя блока вычисления позиционных характеристик и вторым входом n-го умножителя положительного делителя, первый вход которого связан с выходом регистра хранения коэффициента kn, подключенного одновременно ко второму входу n-го умножителя отрицательного делителя, первый вход которого соединен с выходом n-го сумматора делителя блока вычисления позиционных характеристик, на третий вход которого постоянно подается значение логической единицы, второй вход соединен с выходом n-го инвертора делителя блока вычисления позиционных характеристик, первый вход подключен к выходу регистра хранения модуля pn, выход 1-го умножителя положительного делителя подключен к 1-му входу сумматора значения F(B), выход 2-го умножителя положительного делителя подключен ко 2-му входу сумматора значения F(B), и так далее, наконец, выход n-го умножителя положительного делителя подключен к n-му входу сумматора значения F(B), выход 1-го умножителя отрицательного делителя подключен к 1-му входу сумматора значения F (-В), выход 2-го умножителя отрицательного делителя подключен ко 2-му входу сумматора значения F (-В), и так далее, наконец, выход n-го умножителя отрицательного делителя подключен к n-му входу сумматора значения F (-В), выход которого подключен к первому входу регистра хранения значения F (-В), второй и третий входы которого связаны со входом тактового импульса и выходом элемента ИЛИ соответственно, выход соединен с первым входом мультиплексора делителя, второй вход которого соединен с выходом регистра хранения значения F(B), второй и третий входы которого связаны со входом тактового импульса и выходом элемента ИЛИ соответственно, первый вход подключен к первому выходу сумматора значения F (В), второй выход которого одновременно соединен со вторым входом элемента XOR и управляющим входом мультиплексора делителя, выход которого является четвертым выходом блока вычисления позиционных характеристик и подключен к четвертому входу блока уточнения аппроксимационного ряда, а также подключен ко второму входу блока сравнения, первый вход которого соединен с пятым выходом блока вычисления позиционных характеристик и подключен к третьему входу блока уточнения аппроксимационного ряда, и является выходом мультиплексора делимого, управляющий вход которого соединен с первым входом элемента XOR и вторым выходом сумматора значения F(A), первый выход которого соединен с первым входом регистра хранения значения F(A), второй и третий входы которого связаны со входом тактового импульса и выходом элемента ИЛИ соответственно, а выход соединен со вторым входом мультиплексора делимого, первый вход которого подключен к выходу регистра хранения значения F(-A), второй и третий входы которого связаны со входом тактового импульса и выходом элемента ИЛИ соответственно, первый вход подключен к выходу сумматора значения F(-A), выход элемента XOR является первым выходом блока вычисления позиционных характеристик и подключен к первому входу блока вывода частного, второй и третий входы которого соединены с первым и вторым выходами блока сравнения соответственно; блок уточнения аппроксимационного ряда содержит регистр сдвига, счетчик, регистр хранения , регистр хранения уменьшаемого, мультиплексор выбора уменьшаемого, инвертор блока уточнения аппроксимационного ряда, память хранения степеней «2» в СОК, сумматор блока уточнения аппроксимационного ряда, мультиплексор выбора следующего уменьшаемого, элемент НЕ, элемент И, причем первый вход регистра сдвига соединен с четвертым выходом блока вычисления позиционных характеристик, второй и третий входы связаны со входом тактового импульса и выходом элемента ИЛИ соответственно, четвертый вход соединен с первым выходом счетчика, второй и третий входы которого связаны со входом тактового импульса и выходом элемента ИЛИ соответственно, второй выход является вторым выходом блока уточнения аппроксимационного ряда и соединен с седьмым входом блока вывода частного, первый выход счетчика подключен также к управляющему входу мультиплексора выбора уменьшаемого, второй вход которого соединен с выходом регистра хранения , второй и третий входы которого связаны со входом тактового импульса и выходом элемента ИЛИ соответственно, первый вход соединен с пятым выходом блока вычисления позиционных характеристик, первый вход мультиплексора выбора уменьшаемого соединен с выходом регистра хранения уменьшаемого, второй и третий входы которого связаны со входом тактового импульса и выходом элемента ИЛИ соответственно, первый вход подключен к выходу мультиплексора выбора следующего уменьшаемого, первый вход которого соединен с выходом мультиплексора выбора уменьшаемого, который одновременно соединен с первым входом сумматор блока, уточнения аппроксимационного ряда, второй вход которого соединен с выходом инвертора блока уточнения аппроксимационного ряда, вход которого соединен со вторым выходом регистра сдвига, второй вход мультиплексора выбора следующего уменьшаемого соединен с первым выходом сумматора блока уточнения аппроксимационного ряда, второй выход которого подключен одновременно к управляющему входу мультиплексора выбора следующего уменьшаемого и входу элемента НЕ, выход которого подключен ко второму входу элемента И, первый вход которого соединен с выходом памяти хранения степеней «2» в СОК, а выход соединен с шестым входом блока вывода частного, состоящего из элемента ИЛИ блока вывода частного, элемента задержки, удерживающего регистра, n регистров хранения остатка по модулю pi, n сумматоров по модулю pi, n мультиплексоров по модулю pi, n регистров хранения суммы по модулю pi, n инверторов блока вывода частного, n регистров хранения модуля pi, n сумматоров блока вывода частного, n регистров хранения обратного значения суммы по модулю pi, n мультиплексоров выбора суммы, удерживающий регистр знака, регистр хранения суммы в СОК, регистр хранения значения «1», регистр хранения значения «-1», мультиплексор равенства абсолютных величии делимого и делителя, мультиплексор вывода частного, регистр хранения частного, при этом первый выход блока уточнения аппроксимационного ряда соединен с первым входом регистра хранения остатка по модулю p1, второй и третий входы которого связаны со входом тактового импульса и выходом элемента ИЛИ соответственно, а выход соединен с первым входом сумматора по модулю р1, выход которого соединен с информационным входом демультиплексора по модулю р1, управляющий вход которого подключен ко второму выходу блока уточнения аппроксимационного ряда, а второй выход соединен со вторым входом сумматора по модулю p1, первый выход подключен одновременно ко входу 1-го инвертора, блока вывода частного и первому входу регистра хранения суммы по модулю р1, второй и третий входы которого связаны со входом тактового импульса и выходом элемента ИЛИ соответственно, выход соединен с первым входом 1-го мультиплексора выбора суммы, второй вход которого соединен с выходом регистра хранения обратного значения суммы по модулю p1, второй и третий входы которого связаны со входом тактового импульса и выходом элемента ИЛИ соответственно, первый вход соединен с выходом 1-го сумматора блока вывода частного, на третий вход которого постоянно подается логическая единица, второй вход соединен с выходом регистра хранения модуля р1, первый вход соединен с выходом 1-го инвертора блока вывода частного, первый выход блока уточнения аппроксимационного ряда соединен с первым входом регистра хранения остатка по модулю р2, второй и третий входы которого связаны со входом тактового импульса и выходом элемента ИЛИ соответственно, а выход соединен с первым входом сумматора по модулю p2, выход которого соединен с информационным входом демультиплексора по модулю p2, управляющий вход которого подключен ко второму выходу блока уточнения аппроксимационного ряда, а второй выход соединен со вторым входом сумматора по модулю p2, первый выход подключен одновременно ко входу 2-го инвертора блока вывода частного и первому входу регистра хранения суммы по модулю р2, второй и третий входы которого связаны со входом тактового импульса и выходом элемента ИЛИ соответственно, выход соединен с первым входом 2-го мультиплексора выбора суммы, второй вход которого соединен с выходом регистра хранения обратного значения суммы по модулю p2, второй и третий входы которого связаны со входом тактового импульса и выходом элемента ИЛИ соответственно, первый вход соединен с выходом 2-го сумматора блока вывода частного, на третий вход которого постоянно подается логическая единица, второй вход соединен с выходом регистра хранения модуля р2, первый вход соединен с выходом 2-го инвертора блока вывода частного, аналогично первый выход блока уточнения аппроксимационного ряда соединен с первыми входами регистров хранения остатка по модулю pi, и так далее, наконец, первый выход блока уточнения аппроксимационного ряда соединен с первым входом регистра хранения остатка по модулю pn, второй и третий входы которого связаны со входом тактового импульса и выходом элемента ИЛИ соответственно, а выход соединен с первым входом сумматора по модулю pn, выход которого соединен с информационным входом демультиплексора по модулю pn, управляющий вход которого подключен ко второму выходу блока уточнения аппроксимационного ряда, а второй выход соединен со вторым входом сумматора по модулю pn, первый выход подключен одновременно ко входу n-го инвертора блока вывода частного и первому входу регистра хранения суммы по модулю pn, второй и третий входы которого связаны со входом тактового импульса и выходом элемента ИЛИ соответственно, выход соединен с первым входом n-го мультиплексора выбора суммы, второй вход которого соединен с выходом регистра хранения обратного значения суммы по модулю pn, второй и третий входы которого связаны со входом тактового импульса и выходом элемента ИЛИ соответственно, первый вход соединен с выходом n-го сумматора блока вывода частного, на третий вход которого постоянно подается логическая единица, второй вход соединен с выходом регистра хранения модуля pn, первый вход соединен с выходом n-го инвертора блока вывода частного, первый выход блока вычисления позиционных характеристик соединен с первым входом удерживающего регистра знака, второй и третий входы которого связаны со входом тактового импульса и выходом элемента ИЛИ соответственно, выход одновременно подключен к управляющим входам мультиплексоров выбора суммы и управляющему входу мультиплексора равенства абсолютных величин делимого и делителя, первый вход которого соединен с выходом регистра хранения значения второй вход подключен к регистру хранения значения «1», а выход к первому входу мультиплексора выбора частного, второй вход которого подключен к выходу регистра хранения суммы в СОК, n+1-й и n+2-й входы которого связаны со входом тактового импульса и выходом элемента ИЛИ соответственно, а входы с 1-го по n-й соединены с выходами мультиплексоров выбор f суммы с 1-го по n-й соответственно, управляющий вход мультиплексора вывода частного соединен с выходом удерживающего регистра, второй и третий входы которого связаны со входом тактового импульса и выходом элемента ИЛИ соответственно, первый вход соединен со вторым выходом блока сравнения, который одновременно подключен ко второму входу элемента ИЛИ блока вывода частного, первый вход которого соединен с первым выходом блока сравнения, а выход соединен со входом элемента задержки, выход которого соединен со вторым входом элемента ИЛИ, выход мультиплексора вывода частного соединен с первым входом регистра хранения частного, второй и третий входы которого связаны со входом тактового импульса и выходом элемента ИЛИ соответственно, а выход соединен с выходом вывода частного.

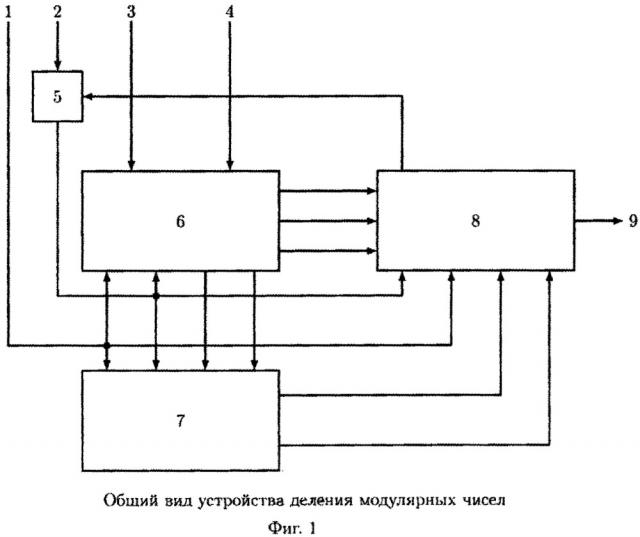

Данное устройство деления модулярных чисел поясняется фигурами 1-4. На фигуре 1 представлен общий вид устройства деления модулярных чисел, которое содержит вход тактового импульса 1, вход глобального сброса 2, вход делимого 3, вход делителя 4, элемент ИЛИ 5, блок вычисления позиционных характеристик 6, блок уточнения аппроксимационного ряда 7, блок вывода частного 8 и выход вывода частного 9.

На фигуре 2 показан блок вычисления позиционных характеристик 6, который содержит регистр делимого 10, n инверторов делимого 11.1-11.n блока вычисления позиционных характеристик, n регистров хранения модуля pi 12.1-12.n, где i=1,…, n, n регистров хранения коэффициента ki 13.1-13.n, n сумматоров делимого 14.1-14.n блока вычисления позиционных характеристик 6, n умножителей отрицательного делимого 15.1-15.n, n умножителей положительного делимого 16.1-16.n, сумматор значения F (А) 17, сумматор значения F (-А) 18, регистр хранения значения F (-А) 19, регистр хранения значения F (А) 20, регистр делителя 21, n инверторов делителя 22.1-22.n блока вычисления позиционных характеристик, n регистров хранения модуля pi 23.1-23.n, n регистров хранения коэффициента ki 24.1-24.n, n сумматоров делителя 25.1-25.n блока вычисления позиционных характеристик 6, n умножителей отрицательного делителя 26.1-26.n, n умножителей положительного делителя 27.1-27.n, сумматор значения F (В) 28, сумматор значения F{(- B) 29, регистр хранения значения F(- B) 30, регистр хранения значения F (В) 31, элемент XOR 32, мультиплексор делимого 33, мультиплексор делителя 34, блок сравнения 35.

На фигуре 3 показан блок уточнения аппроксимационного ряда 7, который содержит регистр сдвига 36, счетчик 37, регистр хранения 38, регистр хранения уменьшаемого 39, мультиплексор выбора уменьшаемого 40, инвертор 41 блока уточнения аппроксимационного ряда 7, память хранения степеней «2» в СОК 42, сумматор 43 блока уточнения аппроксимационного ряда 7, мультиплексор выбора следующего уменьшаемого 44, элемент НЕ 45, элемент И 46.

На фигуре 4 показан блок вывода частного, состоящий из элемента ИЛИ 47 блока вывода частного 8, элемента задержки 48, удерживающего регистра 49, n регистров хранения остатка по модулю pi 50.1-50.n, n сумматоров по модулю pi 51.1-51.n, n демультиплексоров по модулю pi 52.1-52.n, га регистров хранения суммы по модулю pi 53.1-53.n, n инверторов 54.1-54.n блока вывода частного 8, n регистров хранения модуля pi 55.1-55.n, n сумматоров 56.1-56.n блока вывода, частного 8, n регистров хранения обратного значения суммы по модулю pi 57.1-57.n, n мультиплексоров выбора суммы 58.1-58.n, удерживающего регистра знака 59, регистра хранения суммы в СОК 60, регистра хранения значения «1» 61, регистра хранения значения «-1» 62, мультиплексора равенства абсолютных величии делимого и делителя 63, мультиплексора вывода частного 64, регистра хранения частного 65.

Тактовый импульс, необходимый для управления работой регистров и счетчиков, со входа тактового импульса 1 поступает на третий вход блока, вычисления позиционных характеристик 6, па первый вход блока уточнения аппроксимационного ряда 7 и на пятый вход блока вывода частного 8.

Сигнал глобального сброса со входа глобального сброса 2 поступает на первый вход элемента ИЛИ 5, на второй вход которого с первого выхода блока вывода частного 8 поступает сигнал прерывания деления, который формируется при . С выхода элемента ИЛИ 5 сигнал сброса поступает на четвертый вход блока вычисления позиционных характеристик 6, на второй вход блока уточнения аппроксимационного ряда 7 и на четвертый вход блока вывода частного 8.

Значения делимого А и делителя В, представленные в СОК по модулям p1,р2,…,pn, поступают со входа делимого 3 и входа делителя 4 па первый и второй входы блока вычисления позиционных характеристик 6 соответственно.

Для корректного выполнения деления необходимо производить вычисления над абсолютными значениями, но поскольку определение знака в СОК без дополнительных действий невозможно, блок вычисления позиционных характеристик 6 находит одновременно значения F (А) и F(-A), F (В) и F(-B). В процессе вычисления и происходит определение знаков делимого А и делителя В, которые участвуют в вычислении знака частного Q, который подается с первого выхода блока вычисления позиционных характеристик 6 на первый вход блока вывода частного 8. На основе определения знаков делимого А и делителя В блок вычисления позиционных характеристик 6 выбирает необходимые значения и , которые с пятого и четвертого выходов блока вычисления позиционных характеристик 6 соответственно поступают на третий и четвертый входы блока уточнения аппроксимационного ряда 7. Также на основе значений и происходит вычисления значений неравенств и , которые со второго и третьего выходов блока вычисления позиционных характеристик 6 соответственно поступают на второй и третий входы блока вывода частного 8.

Блок уточнения аппроксимационного ряда 7 вычисляет степени «2», которые входят в представление по основанию «2» частного Q и отправляет их с первого выхода блока уточнения аппроксимационного ряда 7 на шестой вход блока вывода частного 8. На второй выход блока уточнения аппроксимационного ряда 7 подается сигнал окончания работы регистра сдвига 36, который сигнализирует о том, что все степени «2», входящие в представление частного Q, проверены. Данный сигнал поступает на седьмой вход блока вывода частного 8.

Блок вывода частного 8 суммирует степени «2», поступающие на шестой вход и выдает их на второй вход блока вывода частного 8, который является выходом вывода частного 9 и содержит значение частного Q. В случае поступления на второй вход блока вывода частного 8 сигнала на первый выход блока вывода частного 8 подается сигнал сброса, который приводит к появлению на выходе вывода частного 9 значения «0». В случае поступления на третий вход блока вывода частного 8 сигнала па первый выход блока вывода частного 8 подается сигнал сброса, который сбрасывает значения регистров и счетчиков, на выход вывода частного 9 подается значения «±1» в зависимости от значения знака частного с первого входа блока вывода частного 8.

Значение делимого А со входа делимого 3 поступаю па первый вход регистра делимого 10, на второй и третий входы которого поступают тактовые сигналы и сигнал сброса со входа тактового импульса 1 и выхода элемента ИЛИ 5 соответственно. Значения остатков по каждому модулю ai=A mod pi поступают па соответствующие n выходов регистра делимого 10, где р1, р2,…, рi,…,pn - модули СОК.

Остаток а1 по первому модулю с первого выхода регистра делимого 10 поступает одновременно на вход 1-го инвертора делимого 11.1 блока вычисления позиционных характеристик 6 и второй вход 1-го умножителя положительного делимого 16.1, инвертированное значение с выхода 1-го инвертора делимого 11.1 поступает па второй вход 1-го сумматора делимого 14.1 блока вычисления позиционных характеристик 6, па первый вход которого с выхода регистра хранения модуля p1 12.1 поступает значение модуля p1, а на третий вход постоянно подается логическая единица, что соответствует операции вычитания и получению значения -a1. Значение с выхода 1-го сумматора делимого 14.1 блока вычисления позиционных характеристик 6 поступает на первый вход 1-го умножителя отрицательного делимого 15.1. на второй вход которого поступает значение коэффициента k1 с регистра хранения коэффициента k1 13.1, которое одновременно подается и на первый вход 1-го умножителя положительного делимого 16.1.

Аналогичные операции происходят с каждым остатком ai по модулю pi. Наконец, остаток an по n-му модулю с n-го выхода регистра делимого 10 поступает одновременно на вход n-го инвертора делимого 11.n блока вычисления позиционных характеристик 6 и второй вход n-го умножителя положительного делимого 16.n, инвертированное значение с выхода n-го инвертора делимого 11.n поступает на второй вход n-го сумматора делимого 14.n блока вычисления позиционных характеристик 6, на первый вход которого с выхода регистра хранения модуля pn 12.n поступает значение модуля pn, а на третий вход постоянно подается логическая единица, что соответствует операции вычитания и получению значения - an.. Значение с выхода n-го сумматора делимого 14.n блока вычисления позиционных характеристик 6 поступает на первый вход n-го умножителя отрицательного делимого 15.n, на второй вход которого поступает значение коэффициента kn с регистра хранения коэффициента kn 13.n, которое одновременно подается и на первый вход n-го умножителя положительного делимого 16.n.

Далее значения с умножителей отрицательного делимого 15.1-15.n поступают на сумматор значения F(-A) 18, откуда данные подаются на первый вход регистра хранения значения F (-А) 19, на второй и третий входы которого поступают тактовые сигналы и сигнал сброса, откуда данные поступают на первый вход мультиплексора делимого 33; значения с умножителей положительного делимого 16.1-16.n поступают на сумматор значения F (А) 17, с первого выхода которого данные подаются на первый вход регистра хранения значения F (А) 20, на второй и третий входы которого поступают тактовые сигналы и сигнал сброса, а с выхода данные поступают на второй вход мультиплексора делимого 33; со второго выхода сумматора значения F (А) 17 значение знака поступает на управляющий вход мультиплексора делимого 33 и первый вход элемента XOR 32. В зависимости от знака F (А) мультиплексор делимого 33 подает с первого или второго входа значение на выход мультиплексора делимого 33, которое поступает на пятый выход блока вычисления позиционных характеристик 6 и на первый вход блока сравнения 35.

Значение делителя В со входа делителя 4 поступаю на первый вход регистра делителя 21, на второй и третий входы которого поступают тактовые сигналы и сигнал сброса. Значения остатков по каждому модулю bi=В mod pi поступают на соответствующие n выходов регистра делителя 21, где p1, p2, …, pn - модули СОК.

Остаток b1 по первому модулю с первого выхода регистра делителя 21 поступает одновременно на вход 1-го инвертора делителя 22.1 блока вычисления позиционных характеристик 6 и второй вход 1-го умножителя положительного делителя 27.1, инвертированное значение с выхода 1-го инвертора делителя 22.1 блока вычисления позиционных характеристик 6 поступает на второй вход 1-го сумматора делителя 25.1 блока вычисления позиционных характеристик 6, на первый вход которого с выхода регистра хранения модуля p1 23.1 поступает значение модуля p1, а на третий вход постоянно подается логическая единица, что соответствует операции вычитания и получению значения -b1. Значение с выхода 1-го сумматора делителя 25.1 блока вычисления позиционных характеристик 6 поступает на первый вход 1-го умножителя отрицательного делителя 26.1, на второй вход которого поступает значение коэффициента k1 с регистра хранения коэффициента k1 24.1, которое одновременно подается и на первый вход 1-го умножителя положительного делителя 27.1.

Аналогичные операции происходят с каждым остатком bi по модулю pi. Наконец, остаток bn по n-му модулю с n-го выхода регистра делителя 21 поступает одновременно на вход n-го инвертора делителя 22.n блока вычисления позиционных характеристик 6 и второй вход n-го умножителя положительного делителя 27.n, инвертированное значение с выхода n-го инвертора делителя 22.n блока вычисления позиционных характеристик 6 поступает на второй вход n-го сумматора делителя 25.n блока вычисления позиционных характеристик 6, на первый вход которого с выхода регистра хранения модуля pn 23.n поступает значение модуля pn, а на третий вход постоянно подается логическая единица, что соответствует операции вычитания и получению значения - bn. Значение с выхода n-го сумматора делителя 25.n блока вычисления позиционных характеристик 6 поступает на первый вход n-го умножителя отрицательного делителя 26.n, на второй вход которого поступает значение коэффициента kn с регистра хранения коэффициента kn 24.n, которое одновременно подает