Лавриненко Антон Викторович (RU)

Изобретатель Лавриненко Антон Викторович (RU) является автором следующих патентов:

Нейронная сеть для деления чисел, представленных в системе остаточных классов

Изобретение относится к вычислительным модулярным нейрокомпьютерным системам. Техническим результатом является расширение функциональных возможностей, повышение скорости деления и уменьшение объема оборудования. Нейронная сеть содержит входной слой нейронов, на входы которых поступают остатки делимого числа по системе модулей, (n-1) нейронных сетей конечного кольца для суммирования, (n-1) нейронны...

2318239

Нейронная сеть ускоренного масштабирования модулярных чисел

Изобретение относится к вычислительной технике, в частности к модулярным нейрокомпьютерным средствам, и предназначено для выполнения операции масштабирования модулярных чисел. Техническим результатом является уменьшение объема оборудования, повышение быстродействия и расширение функциональных возможностей устройства. Устройство содержит входной слой нейронов, на которые подаются остатки масштаби...

2359325

Нейронная сеть для обнаружения ошибок в симметричной системе остаточных классов

Изобретение относится к вычислительной технике и может быть использовано для построения модулярных нейрокомпьютеров, функционирующих в симметричной системе остаточных классов. Техническим результатом является уменьшение аппаратной сложности. Заявленная нейронная сеть содержит блок нейронной сети конечного кольца формирования старшего коэффициента обобщенной позиционной системы счисления, блок сд...

2374678

Нейронная сеть с пороговой (k, t) структурой для преобразования остаточного кода в двоичный позиционный код

Изобретение относится к нейронной сети с пороговой (k, t) структурой для преобразования остаточного кода в двоичный позиционный код, которая является схемой восстановления позиционного числа по сокращенной системе модулей остаточных классов независимо от того, что часть модулей искажена и они отбрасываются либо часть модулей просто игнорируется. Техническим результатом является расширение функци...

2380751

Нейронная сеть основного деления модулярных чисел

Изобретение относится к вычислительным модулярным нейрокомпьютерным системам и предназначено для выполнения основной операции деления модулярных чисел. Техническим результатом является расширение функциональных возможностей устройства за счет выполнения операции деления при произвольных значениях делимого и делителя, а также сокращение объема оборудования. Устройство содержит входные регистры дел...

2400813

Устройство для обнаружения переполнения динамического диапазона, определения ошибки и локализации неисправности вычислительного канала в эвм, функционирующих в системе остаточных классов

Изобретение относится к вычислительной технике и может быть использовано при диагностике вычислительных систем для обнаружения переполнения динамического диапазона, определения ошибки и локализации неисправного канала в ЭВМ, функционирующих в системе остаточных классов. Техническим результатом является повышение скорости определения функциональных характеристик и сокращения аппаратурных затрат....

2483346

Устройство для сравнения чисел, представленных в системе остаточных классов

Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах, функционирующих в системе остаточных классов. Техническим результатом является повышение быстродействия устройства и сокращение аппаратных затрат. Устройство содержит входные регистры, схемы определения знака, схемы сдвига полярности чисел, просмотровые таблицы (память) для хранения констант и ,...

2503992

Устройство для определения знака модулярного числа

Устройство относится к вычислительной технике и может быть использовано в вычислительных системах, функционирующих в системе остаточных классов. Техническим результатом является повышение быстродействия устройства определения знака числа и сокращения оборудования. Устройство содержит входные регистры для временного хранения разрядов исходного числа, память для хранения произведений и параллельн...

2503995

Устройство для основного деления модулярных чисел в формате системы остаточных классов

Изобретение относится к вычислительной технике и может быть использовано в арифметико-логических устройствах вычислительных систем, функционирующих в системе остаточных классов. Техническим результатом является повышение быстродействия и упрощение устройства. Устройство содержит регистры, мультиплексоры, блоки расширения, демультиплексоры, LUT-таблицу, умножители, схемы вычитания и умножения, кл...

2559772

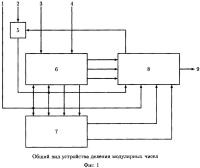

Устройство деления модулярных чисел

Изобретение относится к вычислительным модулярным системам и предназначено для выполнения деления чисел, представленных в системе остаточных классов (СОК). Технический результат – обеспечение возможности деления с отрицательными числами, представленными в системе остаточных классов. Устройство деления модулярных чисел содержит вход тактового импульса, вход глобального сброса, вход делимого, вход д...

2628179