Устройство формирования изображения, система формирования изображения и способ изготовления устройства формирования изображения

Иллюстрации

Показать всеИзобретение относится к устройству формирования изображения, системе формирования изображения и способу изготовления устройства формирования изображения. Изобретение позволяет уменьшить изменение характеристик полевого транзистора с управляющим p-n-переходом. Устройство формирования изображения включает в себя множество пикселей, каждый из которых включает в себя полевой транзистор с управляющим p-n-переходом, выполненный на полупроводниковой подложке. Полевой транзистор с управляющим p-n-переходом включает в себя область затвора и область канала. Область затвора и область канала пересекают друг друга на виде сверху. 5 н. и 15 з.п. ф-лы, 10 ил.

Реферат

Область техники, к которой относится изобретение

[0001] Настоящее изобретение относится к устройству формирования изображения, системе формирования изображения и способу изготовления устройства формирования изображения.

Предшествующий уровень техники

[0002] Предложено устройство формирования изображения, в котором используются полевые транзисторы с управляющим p-n-переходом. В патентной литературе (PTL) 1 описано устройство формирования изображения, включающее в себя множество пикселей. Каждый пиксель включает в себя полевой транзистор с управляющим p-n-переходом. В полевом транзисторе с управляющим p-n-переходом, описанном в PTL 1, область канала расположена между поверхностной областью затвора и областью скрытого затвора. Область канала соединена с областью стока на конечном участке области скрытого затвора.

[0003] В PTL 2 описан способ формирования полевого транзистора с управляющим p-n-переходом. В способе, описанном в PTL 1, поверхностная область затвора, область канала и области истока и стока полевого транзистора с управляющим p-n-переходом сформированы путем ионной имплантации с использованием различных рисунков фоторезиста в качестве масок.

Перечень цитируемой литературы

Патентная литература

[0004] PTL 1: Выложенная японская патентная заявка № 2007-165736

PTL 2: Выложенная японская патентная заявка № 2006-196789

Сущность изобретения

Техническая задача

[0005] В полевом транзисторе с управляющим p-n-переходом, описанном в PTL 1, конец на стороне стока области канала определяется конечным положением области затвора, тогда как конец на стороне истока области канала определяется положением области истока. Поэтому, если существует ошибка совмещения между маской, используемой для формирования области истока, и маской, используемой для формирования области скрытого затвора, может изменяться длина канала. Это приводит к изменению характеристик полевого транзистора с управляющим p-n-переходом.

[0006] В способе, описанном в PTL 2, если существует ошибка совмещения между маской, используемой для формирования поверхностной области затвора, и маской, используемой для формирования области канала, может изменяться ширина канала. Это приводит к изменению характеристик полевого транзистора с управляющим p-n-переходом.

[0007] Принимая во внимание описанные выше проблемы, настоящее изобретение нацелено на выполнение устройства формирования изображения, в котором достигается меньшее изменение характеристик полевого транзистора с управляющим p-n-переходом.

Решение технической задачи

[0008] Вариант осуществления согласно аспекту настоящего изобретения представляет собой способ изготовления устройства формирования изображения, которое включает в себя множество пикселей, каждый из которых включает в себя полевой транзистор с управляющим p-n-переходом, выполненный на полупроводниковой подложке. Способ включает в себя этап формирования области затвора полевого транзистора с управляющим p-n-переходом путем введения примеси в полупроводниковую подложку с использованием первой маски, которая определяет первое отверстие, и этап формирования области канала полевого транзистора с управляющим p-n-переходом путем введения примеси в полупроводниковую подложку с использованием второй маски, которая определяет второе отверстие. Второе отверстие включает в себя участок на стороне истока, соответствующий участку на стороне истока области канала, и участок на стороне стока, соответствующий участку на стороне стока области канала. Ортогональная проекция первого отверстия на плоскость, параллельную поверхности полупроводниковой подложки, пересекает ортогональную проекцию второго отверстия на плоскость. Каждая из ортогональной проекции участка на стороне истока второго отверстия на плоскость и ортогональной проекции участка на стороне стока второго отверстия на плоскость перекрывает ортогональную проекцию первой маски на плоскость.

[0009] Вариант осуществления согласно другому аспекту настоящего изобретения представляет собой способ формирования устройства формирования изображения, которое включает в себя множество пикселей, каждый из которых включает в себя полевой транзистор с управляющим p-n-переходом, выполненный на полупроводниковой подложке. Способ включает в себя этап формирования области затвора полевого транзистора с управляющим p-n-переходом на полупроводниковой подложке и этап формирования области канала полевого транзистора с управляющим p-n-переходом на полупроводниковой подложке. Ортогональная проекция первой области на плоскость, параллельную поверхности полупроводниковой подложки, пересекает ортогональную проекцию второй области на плоскость. Первая область представляет собой область, в которую вводится примесь на этапе формирования области затвора, и вторая область представляет собой область, в которую вводится примесь на этапе формирования области канала. На плоскости каждый из участка на стороне истока и участка на стороне стока ортогональной проекции второй области выступает из ортогональной проекции первой области.

[0010] Вариант осуществления согласно еще одному аспекту настоящего изобретения представляет собой устройство формирования изображения, которое включает в себя множество пикселей, каждый из которых включает в себя полевой транзистор с управляющим p-n-переходом, выполненный на полупроводниковой подложке. Полевой транзистор с управляющим p-n-переходом включает в себя область затвора и область канала. Ортогональная проекция области затвора на плоскость, параллельную поверхности полупроводниковой подложки, пересекает ортогональную проекцию области канала на плоскость. На плоскости каждый из участка на стороне истока и участка на стороне стока ортогональной проекции области канала выступает из ортогональной проекции области затвора.

[0011] Вариант осуществления согласно еще одному аспекту настоящего изобретения представляет собой устройство формирования изображения, которое включает в себя множество пикселей, каждый из которых включает в себя полевой транзистор с управляющим p-n-переходом, выполненный на полупроводниковой подложке. Полевой транзистор с управляющим p-n-переходом включает в себя поверхностную область затвора, область скрытого затвора и область канала, которые располагаются на различных глубинах. Область канала расположена на глубине между поверхностной областью затвора и областью скрытого затвора. Каждая из ортогональной проекции поверхностной области затвора на плоскость, параллельную поверхности полупроводниковой подложки, и ортогональной проекции области скрытого затвора на плоскость пересекает ортогональную проекцию области канала на плоскость.

Преимущественные эффекты изобретения

[0012] Настоящее изобретение позволяет уменьшить изменение характеристик полевого транзистора с управляющим p-n-переходом.

Краткое описание чертежей

[0013] На фиг.1 схематично показана планарная структура устройства формирования изображения.

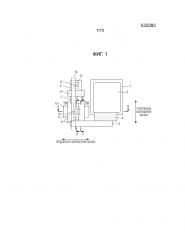

На фиг.2 схематично показана структура в поперечном сечении устройства формирования изображения.

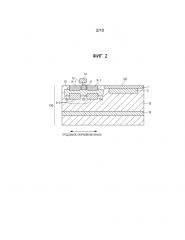

На фиг.3 схематично показана структура в поперечном сечении устройства формирования изображения.

На фиг.4 показан для пояснения способ изготовления устройства формирования изображения.

На фиг.5 схематично показаны маски, используемые для изготовления устройства изображения.

На фиг.6 схематично показана планарная структура и структуры в поперечном сечении устройств формирования изображения.

На фиг.7 схематично показана планарная структура устройства формирования изображения.

На фиг.8 схематично показана структура в поперечном сечении устройства формирования изображения.

На фиг.9 показан для пояснения способ изготовления устройства формирования изображения.

На фиг.10 показана блок-схема системы формирования изображения.

Описание вариантов осуществления

[0014] Вариант осуществления настоящего изобретения представляет собой устройство формирования изображения включающее в себя множество пикселей. Каждый пиксель включает в себя полевой транзистор с управляющим p-n-переходом (именуемый в дальнейшем JFET). JFET включает в себя область затвора, область канала, область стока и область истока, сформированные на полупроводниковой подложке. В JFET тип проводимости области затвора отличается от типа проводимости области канала, области стока и области истока. В настоящем варианте осуществления используется JFET с горизонтальным каналом, в котором направление протекания тока канала параллельно поверхности полупроводниковой подложки.

[0015] Варианты осуществления настоящего изобретения характеризуются структурой области затвора и области канала или способа их изготовления. В частности, область затвора и область канала сформированы таким образом, чтобы они пересекали друг друга на виде сверху. Размещения или формы компонентов на виде сверху, описанные в настоящем описании, относятся к размещениям или формам ортогональных проекций компонентов на плоскость, параллельную поверхности полупроводниковой подложки. То есть ортогональная проекция области затвора на плоскость, параллельную поверхности полупроводниковой подложки, и ортогональная проекция области канала на плоскость, параллельную поверхности полупроводниковой подложки, пересекают друг друга на плоскости. Поверхность полупроводниковой подложки является границей раздела между полупроводниковой областью и изолятором.

[0016] Пересечение двух областей означает, что каждая область располагается поперек другой области. Другими словами, пересечение двух областей означает, что по меньшей мере две части одной области выступают из другой области, и что по меньшей мере две части другой области выступают из одной области. Если одна область содержит другую область, то эти две области не пересекают друг друга.

[0017] В способе изготовления вариантов осуществления согласно настоящему изобретению множество масок используется для формирования области затвора и области канала. Маски имеют соответствующие отверстия, которые пересекают друг друга на виде сверху.

[0018] При этой конфигурации, несмотря на то, что между маской, используемой для формирования области затвора, и маской, используемой для формирования области канала, могут возникать ошибки совмещения, форма пересекающейся части области затвора и области канала остается почти неизменной. То есть можно уменьшить изменение длины канала и ширины канала JFET. Таким образом, можно уменьшить изменение характеристик JFET.

[0019] Варианты осуществления настоящего изобретения будут описаны ниже со ссылкой на чертежи. В вариантах осуществления, описанных ниже, область затвора является областью p-типа, тогда как область канала, область стока и область истока являются областями n-типа. Настоящее изобретение не ограничивается только вариантами осуществления, описанными ниже. Например, тип проводимости каждой полупроводниковой области может полностью меняться на противоположный. Кроме того, примеры, в которых часть конфигурации одного из следующих вариантов осуществления добавлена в другой вариант осуществления или заменена на часть конфигурации другого варианта осуществления, представляют собой также варианты осуществления настоящего изобретения.

Первый вариант осуществления

[0020] Фиг.1 схематично иллюстрирует планарную структуру устройства формирования изображения настоящего варианта осуществления. Один пиксель иллюстрирован на фиг.1. Пиксель включает в себя участок фотоэлектрического преобразования, такой как фотодиод, переходной транзистор, транзистор сброса и JFET. Устройство формирования изображения настоящего варианта осуществления включает в себя множество пикселей, один из которых проиллюстрирован на фиг.1.

[0021] Участок фотоэлектрического преобразования настоящего варианта осуществления представляет собой фотодиод. Фотодиод включает в себя полупроводниковую область 1 n-типа, сформированную на поверхности полупроводниковой подложки, и полупроводниковую область 2 р-типа, сформированную под полупроводниковой областью 1 n-типа. Полупроводниковая область 1 n-типа и полупроводниковая область 2 р-типа образуют p-n-переход. Дырки, сгенерированные падающим светом, накапливаются в полупроводниковой области 2 р-типа в виде сигнального заряда. Сигнальный заряд, накопленный в полупроводниковой области 2 р-типа, передается в область плавающей диффузии (которая в дальнейшем упоминается как FD-область 3). FD-область 3 представляет собой полупроводниковую область 2 р-типа. Электрод 4 передаточного затвора обеспечивает перенос сигнального заряда из полупроводниковой области 2 р-типа в FD-область 3.

[0022] JFET включает в себя область 9 затвора p-типа, область 10 канала n-типа и область 11 истока n-типа. В по меньшей мере части области 10 канала n-типа сформирован канал, управляемый напряжением области 9 затвора. JFET настоящего варианта осуществления включает в себя множество областей 9 затвора. Область 10 канала пересекает каждую из областей 9 затвора на виде сверху. Область 10 канала расположена поперек области 9 затвора от стороны истока до стороны стока. Часть (область 10d на фиг.1) области 10 канала образует область стока JFET. Канал JFET сформирован в пересекающейся части области 9 затвора и области 10 канала. Концентрация примесей в области 11 истока выше, чем в области 10 канала. Область 11 истока электрически соединена с выходной линией 14 через контактный штырек 12. FD-область 3 электрически соединена с областью 9 затвора. В этой конфигурации JFET выводит сигнал, соответствующий напряжению FD-области 3 в выходную линию 14.

[0023] МОП-транзистор сброса включает в себя область 5 стока p-типа, область 7 истока p-типа и электрод 8 затвора. Область 5 стока электрически соединена с разводкой 13 стока сброса через контактный штырек 6. Область 7 истока МОП-транзистора сброса электрически соединена с областью 9 затвора JFET. При этой конфигурации МОП-транзистор сброса осуществляет сброс напряжения затвора JFET. Использование МОП-транзистора в качестве транзистора сброса является простым. В качестве транзистора сброса можно использовать другие типы транзисторов, включая JFET.

[0024] JFET настоящего варианта осуществления включает в себя множество областей 9 затвора, представленных на виде сверху. Области 9 затвора размещаются с областью 11 истока, расположенной между ними на виде сверху. Другими словами, ортогональная проекция области 11 истока на плоскость, параллельную поверхности полупроводниковой подложки, располагается между ортогональными проекциями областей 9 затвора на плоскость. JFET настоящего варианта осуществления дополнительно включает в себя множество областей стока. Более конкретно, область 10 канала включает в себя множество участков 10d на стороне стока. Каждая из областей стока расположена на противоположной стороне области 11 истока по отношению к одной из областей 9 затвора. Для каждой из областей 9 затвора сформирован канал. Области 9 затвора предпочтительно размещаются параллельно друг другу на виде сверху. Области 9 затвора электрически соединены друг с другом с помощью полупроводниковой области, имеющей одинаковый тип проводимости. В настоящем варианте осуществления FD-область 3 и область 7 истока МОП-транзистора сброса электрически соединяют области 9 затвора друг с другом.

[0025] При этой конфигурации можно увеличить эффективную ширину канала JFET. То есть, так как можно повысить электродвижущую силу JFET, устройством формирования изображения можно управлять с высокой скоростью. JFET может включать в себя только одну область затвора. В частности, можно удалить одну из этих двух областей 9 затвора, иллюстрированных на фиг.1, и соответствующую область стока.

[0026] На фиг.2 показана схема, схематично иллюстрирующая структуру в поперечном сечении устройства формирования изображения настоящего варианта осуществления. Фиг.2 схематично иллюстрирует структуру в поперечном сечении, взятом вдоль линии A-B, показанной на фиг.1. Одинаковые части, которые соответствуют частям, показанным на фиг.1, обозначены одинаковыми ссылочными позициями.

[0027] Фиг.2 иллюстрирует полупроводниковую подложку 100. На полупроводниковой подложке 100 выполнена изоляционная пленка (не показана). Поверхность SR полупроводниковой подложки 100 является границей раздела между полупроводниковой подложкой 100 и изоляционной пленкой (не показана). Продольное направление канала представляет собой направление, параллельное как плоскости, показанной на фиг.2, так и поверхности SR.

[0028] Фотодиод и JFET сформированы в полупроводниковой области 15 n-типа. Ток стока JFET подается через полупроводниковую область 15 n-типа. Хотя это и не показано, участок для подачи тока стока, выполненный с возможностью подачи тока стока для полупроводниковой области 15 n-типа, сформирован за пределами пиксельной зоны или в части пиксельной зоны. Например, участок для подачи тока стока является контактным штырьком, который соединяют полупроводниковую подложку с разводкой.

[0029] Полупроводниковая область 16 n-типа, имеющая более высокую концентрацию примесей, чем полупроводниковая область 15 n-типа, расположена под полупроводниковой областью 15 n-типа. Сопротивление полупроводниковой подложки можно уменьшить с помощью полупроводниковой области 16 n-типа. При этой конфигурации можно уменьшить падение напряжения на полупроводниковой подложке, вызванное током стока, подаваемым для JFET. Таким образом, можно уменьшить шум, такой как затенение, вызванное напряжением полупроводниковой подложки, которая изменяется в зависимости от места расположения. В результате этого можно повысить качество изображения. Ток стока JFET можно также увеличить. В результате, устройством формирования изображения можно управлять с высокой скоростью.

[0030] Часть 10d области 10 канала можно опустить, и часть полупроводниковой области 15 n-типа может образовать область стока. Область стока представляет собой полупроводниковую область n-типа, которая расположена на виде сверху рядом с областью, где должен быть сформирован канал.

[0031] Область 9 затвора JFET настоящего варианта осуществления включает в себя поверхностную область 9-1 затвора и область 9-2 скрытого затвора. Как поверхностная область 9-1 затвора, так и область 9-2 скрытого затвора имеют проводимость p-типа. Поверхностная область 9-1 затвора и область 9-2 скрытого затвора расположены на различных глубинах. Область 10 канала расположена на глубине между поверхностной областью 9-1 затвора и областью 9-2 скрытого затвора. При этой конфигурации сформирован JFET с горизонтальным каналом. В JFET с горизонтальным каналом, как иллюстрировано на фиг.2, продольное направление канала параллельно поверхности полупроводниковой подложки.

[0032] Поверхностная область 9-1 затвора и область 9-2 скрытого затвора электрически соединены друг с другом. Участок соединения между поверхностной областью 9-1 затвора и областью 9-2 скрытого затвора располагается без перекрытия области 10 канала на виде сверху. При этой конфигурации каждая из областей затвора позволяет управлять каналом JFET.

[0033] Поверхностная область 9-1 затвора и область 9-2 скрытого затвора перекрывают друг на друга на виде сверху. Другими словами, ортогональная проекция поверхностной области 9-1 затвора на плоскость, параллельную поверхности полупроводниковой подложки, идентична ортогональной проекции области 9-2 скрытого затвора на плоскость. При этой конфигурации поверхностную область 9-1 затвора и область 9-2 скрытого затвора можно сформировать с одинаковой маской. Это выгодно для уменьшения изменения характеристик JFET.

[0034] Ортогональная проекция поверхностной области 9-1 затвора необязательно должна быть идентичной ортогональной проекции области 9-2 скрытого затвора. Например, поверхностную область 9-1 затвора и область 9-2 скрытого затвора можно разместить таким образом, чтобы поверхностная область 9-1 затвора пересекала область 10 канала, а область скрытого затвора содержала область 10 канала на виде сверху. В этом случае поверхностная область затвора и область скрытого затвора формируются с использованием различных масок.

[0035] Можно обойтись без одной из поверхностной области 9-1 затвора и области 9-2 скрытого затвора. В настоящем варианте осуществления каждая из областей 9 затвора, представленных на виде сверху, включает в себя поверхностную область 9-1 затвора и область 9-2 скрытого затвора. В качестве альтернативы, по меньшей мере одна из областей 9 затвора может включать в себя поверхностную область 9-1 затвора и область 9-2 скрытого затвора.

[0036] На фиг.3(a) показана схема, схематично иллюстрирующая структуру в поперечном сечении устройства формирования изображения настоящего варианта осуществления. Фиг.3(a) схематично иллюстрирует структуру в поперечном сечении, взятом вдоль линии C-D, показанной на фиг.1. Одинаковые части, которые соответствуют частям, показанным на фиг.1 и 2, обозначены одинаковыми ссылочными позициями. Поперечное направление канала представляет собой направление, параллельное как плоскости, показанной на фиг.3(a), так и поверхности SR.

[0037] Как показано на фиг.3(a), в промежутке ниже области 11 истока между областью 10 канала и полупроводниковой областью 15 n-типа отсутствуют полупроводниковые области р-типа. Однако область 10 канала и полупроводниковая область 15 n-типа электрически изолированы друг от друга. В частности, обедненный слой, сформированный между двумя областями 9-2 скрытого затвора и полупроводниковой областью 15 n-типа, показанной на фиг.2, образует потенциальный барьер между областью 10 канала и полупроводниковой областью 15 n-типа. Это предотвращает омическую проводимость между областью 10 канала и полупроводниковой областью 15 n-типа. На практике профили распределения потенциалов предпочтительно проектируются таким образом, чтобы электрическое сопротивление между областью 10 канала и полупроводниковой областью 15 n-типа JFET в направлении, перпендикулярном к поверхности SR, было по существу выше, чем электрическое сопротивление между истоком и стоком JFET в продольном направлении канала.

[0038] На фиг.3(b) показана схема, схематично иллюстрирующая структуру в поперечном сечении устройства формирования изображения настоящего варианта осуществления. Фиг.3(b) схематично иллюстрирует структуру в поперечном сечении, взятом вдоль линии E-F, показанной на фиг.1. Одинаковые части, которые соответствуют частям, показанным на фиг.1-3(a), обозначены одинаковыми ссылочными позициями. Поперечное направление канала представляет собой направление, параллельное как плоскости, показанной на фиг.3(b), так и поверхности SR.

[0039] Как упомянуто выше, поверхностная область 9-1 затвора и область 9-2 скрытого затвора электрически соединены друг с другом. В настоящем варианте осуществления полупроводниковая область, имеющая одинаковый тип проводимости, электрически соединяет поверхностную область 9-1 затвора и область 9-2 скрытого затвора. Например, на фиг.3(b) FD-область 3 и область 7 истока МОП-транзистора сброса может продолжаться глубоко в подложку до такой степени, чтобы они электрически соединяли поверхностную область 9-1 затвора и область 9-2 скрытого затвора. Хотя поверхностная область 9-1 затвора и область 9-2 скрытого затвора расположены на определенном расстоянии друг от друга на фиг.3(b), поверхностная область 9-1 затвора и область 9-2 скрытого затвора могут постоянно образовываться за счет диффузии примесей в направлении, перпендикулярном поверхности SR.

[0040] В настоящем варианте осуществления область 9 затвора и область 10 канала пересекают друг друга в планарной структуре, иллюстрированной на фиг.1. Другими словами, ортогональная проекция области 9 затвора на плоскость, параллельную поверхности полупроводниковой подложки, и ортогональная проекция области 10 канала на плоскость, параллельную поверхности полупроводниковой подложки, пересекает друг друга.

[0041] Пересечение области 9 затвора и области 10 канала означает, что каждая область располагается поперек другой области. Другими словами, по меньшей мере две части области 9 затвора выступают из области 10 канала, и по меньшей мере две части области 10 канала выступают из области 9 затвора.

[0042] Часть области 10 канала, расположенная между двумя областями 9 затвора на виде сверху, показанном на фиг.1, представляет собой участок 10s на стороне истока области 10 канала. Часть области 10 канала, расположенная на противоположной стороне области 10s на стороне истока по отношению к области 9 затвора, представляет собой участок 10d на стороне стока области 10 канала. Фиг.2 также иллюстрирует участок 10s на стороне истока и участок 10d на стороне стока. Каждый из участка 10s на стороне истока и участка 10d на стороне стока области 10 канала не перекрывает область 9 затвора. Другими словами, участок 10s на стороне истока и участок 10d на стороне стока ортогональной проекции области 10 канала выступают из ортогональной проекции области 9 затвора. Поэтому, как иллюстрировано на фиг.2, длина канала JFET ограничивается концом области 9 затвора. Как показано на фиг.3(b), ширина канала JFET ограничивается концом области 10 канала.

[0043] При этой конфигурации, несмотря на то что между маской, используемой для формирования области 9 затвора, и маской, используемой для формирования области 10 канала могут возникать ошибки совмещения, форма канала JFET остается почти неизменной. То есть можно уменьшить изменение длины канала и ширины канала JFET. Таким образом, можно уменьшить изменение характеристик JFET.

[0044] Как показано на фиг.2, электроны из области 11 истока JFET движутся в продольном направлении канала через канал, сформированный между поверхностной областью 9-1 затвора и областью 9-2 скрытого затвора, и, в конечном счете, попадают в полупроводниковую область 15 n-типа. Величина этого тока канала в основном определяется напряжением области 11 истока, напряжением области 9 затвора, напряжением полупроводниковой области 15 n-типа, которая представляет собой область стока, длиной канала и шириной канала.

[0045] В настоящем варианте осуществления длина канала и ширина канала JFET определяются двумя прямоугольниками, которые представляют собой пересекающиеся участки области 9 затвора и области 10 канала (фиг.1). Длина канала равна длине стороны прямоугольника, пересекающегося участка в продольном направлении канала. Так как ток канала протекает в обоих направлениях, ширина канала в два раза больше длины стороны прямоугольника пересекающегося участка в поперечном направлении канала.

[0046] В настоящем варианте осуществления области 9 затвора представляют собой две прямоугольные области, параллельные друг другу, и область 10 канала является также прямоугольной. Область 9 затвора и область 10 канала размещаются с большим перекрытием по отношению друг к другу. То есть область 9 затвора является слишком большой по отношению к области 10 канала в поперечном направлении канала (фиг.1), и область 10 канала является слишком большой по отношению к области 9 затвора в продольном направлении канала (фиг.1). Соответственно, несмотря на то, что между маской, используемой для формирования области 9 затвора, и маской, используемой для формирования области 10 канала, могут возникать ошибки совмещения, форма прямоугольника пересекающегося участка остается почти неизменной. Поэтому в процессе формирования JFET можно уменьшить изменение электрических характеристик JFET, вызванное ошибками совмещения.

[0047] Уменьшение изменения электрических характеристик JFET достигается независимо от форм области 9 затвора и области 10 канала. Это уменьшение изменения достигается за счет пересечения области 9 затвора и области 10 канала на виде сверху. Предпочтительно, как иллюстрировано на фиг.1, периферия области 9 затвора на виде сверху включает в себя две параллельные линии, проходящие вдоль поперечного направления канала. При этой конфигурации можно дополнительно уменьшить изменение электрических характеристик. Предпочтительно, как иллюстрировано на фиг.1, периферия области 10 канала на виде сверху включает в себя две параллельные линии, проходящие вдоль продольного направления канала. При этой конфигурации можно дополнительно уменьшить изменение электрических характеристик. Если область 9 затвора и область 10 канала имеют прямоугольную форму, то легче сформировать маски, используемые для формирования области 9 затвора и области 10 канала. Периферии области 9 затвора и области 10 канала на виде сверху могут включать в себя кривые. При этой конфигурации можно уменьшить изменение характеристик, вызываемое ошибками совмещения, возникающими в результате поворота масок.

[0048] Длина канала определяется JFET расстоянием между концом на стороне стока и концом на стороне истока. Поэтому когда участок на стороне стока и участок на стороне истока области 10 канала расположены отдельно с обеих сторон области 9 затвора на виде сверху, можно уменьшить изменение электрических характеристик. То есть, так как каждый из участка на стороне истока и участка на стороне стока ортогональной проекции области 10 канала выступает из ортогональной проекции области затвора, можно уменьшить изменение электрических характеристик, описанных выше.

[0049] Пример способа изготовления устройства формирования изображения настоящего варианта осуществления будет объяснен ниже. Фиг.4 представлена для объяснения способа изготовления устройства формирования изображения. Каждая из фиг.4(a)-4(c) схематично иллюстрирует структуру в поперечном сечении, взятом вдоль линии A-B, показанной на фиг.1. Одинаковые части, которые соответствуют частям, показанным на фиг.1-3, обозначены одинаковыми ссылочными позициями.

[0050] Этап, иллюстрированный на фиг.4(a), включает в себя формирование области 9 затвора JFET. На этом этапе используется первая маска 17, которая определяет первое отверстие 209. Первая маска 17 получается, например, путем нанесения рисунка фоторезиста с использованием способа фотолитографии.

[0051] Примеси, которые являются акцепторами, такими как бор, вводятся в полупроводниковую подложку 100 через первое отверстие 209, посредством чего в области, соответствующей первому отверстию 209 полупроводниковой подложки 100, формируется область 9 затвора. Например, область 9 затвора можно сформировать путем ионной имплантации с использованием первой маски 17. Выполняя многократно ионную имплантацию с различными энергиями ионной имплантации, поверхностная область 9-1 затвора и область 9-2 скрытого затвора формируются на различных глубинах. При использовании более высокой энергии ионной имплантации в полупроводниковой подложке 100 можно сформировать более глубокую полупроводниковую область. Выбирая предварительно определенную энергию ионной имплантации, поверхностная область 9-1 затвора и область 9-2 скрытого затвора формируются как электрически соединенные друг с другом за счет диффузии примесей в направлении, перпендикулярном поверхности SR полупроводниковой подложки 100.

[0052] Помимо ионной имплантации процесс, используемый в изготовлении полупроводников, такой как тепловая диффузия, можно использовать для введения примеси в полупроводниковую подложку 100. После формирования области 9 затвора удаляется первая маска 17.

[0053] Этап, иллюстрированный на фиг.4(b), включает в себя формирование области 10 канала JFET. На этом этапе используется вторая маска 18, которая определяет второе отверстие 210. Вторая маска 18 получается, например, путем нанесения рисунка фоторезиста с использованием способа фотолитографии.

[0054] Примеси, которые являются донорами, такими как фосфор или мышьяк, вводятся в полупроводниковую подложку 100 через второе отверстие 210, посредством чего в области, соответствующей второму отверстию 210 полупроводниковой подложки 100, формируется область 10 канала. Например, область 10 канала можно сформировать путем ионной имплантации с использованием второй маски 18. В этом случае, путем регулировки энергии ионной имплантации на глубине между поверхностной областью 9-1 затвора и областью 9-2 скрытого затвора можно сформировать область 10 канала. После формирования области 10 канала удаляется вторая маска 18.

[0055] Хотя это и не показано на фиг.4, полупроводниковую область 2 р-типа, которая электрически соединяет множество областей 9 затвора друг с другом, можно сформировать с использованием третьей маски 19, которая определяет третьи отверстия 203 и 207. Третья маска 19 получается, например, путем нанесения рисунка фоторезиста с использованием способа фотолитографии.

[0056] В настоящем варианте осуществления FD-область 3 и область 7 истока МОП-транзистора сброса формируются с использованием третьей маски 19. Эти области электрически соединяют множество областей 9 затвора друг с другом. После формирования полупроводниковой области р-типа, которая электрически соединяет области 9 затвора друг с другом, удаляется третья маска 19.

[0057] Этап, иллюстрированный на фиг.4(c), включает в себя формирование области 11 истока, которая электрически подсоединена к участку на стороне истока области 10 канала. На этом этапе используется маска 20, которая определяет отверстие 211. Маска 20 является жесткой маской. То есть маска 20 включает в себя изоляционную пленку, изготовленную из неорганического материала, такого как пленка оксида кремния, пленка нитрида кремния или пленка оксинитрида кремния.

[0058] Примеси, которые являются донорами, такими как фосфор или мышьяк, вводятся в полупроводниковую подложку 100 через отверстие 211, посредством чего в области, соответствующей отверстию 211 полупроводниковой подложки 100, формируется область 11 истока.

[0059] Когда жесткая маска используется в качестве маски 20, как описано выше, маску можно использовать в качестве межслойной изоляционной пленки. В частности, после формирования области 11 истока маска 20 не удаляется, и контактный штырек 12, электрически соединенный с областью 11 истока, размещается в отверстии 211. Затем на маске 20 формируется выходная линия 14, подсоединенная к контактному штырьку 12.

[0060] Далее будут объяснены планарные структуры первой - третьих масок 17-19 и их взаимные позиционные соотношения. На фиг.5(a) и 5(b) показаны схемы, схематично иллюстрирующие первую - третьи маски 17-19, используемые на этапах, иллюстрированных на фиг.4. Одинаковые части, которые соответствуют частям, показанным на фиг.4, обозначены одинаковыми ссылочными позициями.

[0061] Каждая фиг.5(a) и 5(b) иллюстрирует первое отверстие 209, второе отверстие 210 и третьи отверстия 203 и 207. Фиг.5(b) иллюстрирует каждую часть второго отверстия 210. В настоящем варианте осуществления первое отверстие 209, второе отверстие 210 и третьи отверстия 203 и 207 имеют, каждое по отдельности, прямоугольную форму. Первая маска 17, которая определяет первое отверстие 209, находится за пределами отверстия 209. Вторая маска 18, которая определяет второе отверстие 210, находится за пределами второго отверстия 210. Третья маска 19, которая определяет третьи отверстия 203 и 207, находится за пределами третьих отверстий 203 и 207.

[0062] Для простоты объяснения первое - третьи отверстия 209, 210, 203 и 207 перекрывают друг на друга на фиг.5(a) и 5(b). Таким образом, фиг.5(a) и 5(b) иллюстрируют выравнивание между множеством масок. На практике маска удаляется после формирования предварительно определенной полупроводниковой области на каждом этапе. Это означает, что одновременно не должны присутствовать две или более масок.

[0063] Первое отверстие 209 и второе отверстие 210 пересекают друг друга на виде сверху. Другими словами, ортогональная проекция первого отверстия 209 на плоскость, параллельную поверхности полупроводниковой подложки 100, пересекает ортогональную проекцию второго отверстия 210 на плоскость.

[0064] Как показано на фиг.5(b), второе отверстие 210 включает в себя участок 210s на стороне истока, соответствующий участку на стороне истока области 10 канала, и участок 210d на стороне стока, соответствующий участку на стороне стока области 10 канала. На фиг.5(b), часть второго отверстия 210 между двумя первыми отверстиями 209 представляет собой участок 210s на стороне истока второго отверстия 210. К тому же на фиг.5(b) часть слева от первого отверстия 209L на лев