Функциональный преобразователь число-импульсного кода в двоичный код

Иллюстрации

Показать всеРеферат

тз : . ° },* . " : 1н

0n " " Е

ИЗОБРЕТЕН ИЯ

474001

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЙИЛЬСТВУ (61) Зависимое от авт. свидетельства— (22) Заявлено 16.11.72 (21) 1847407/18-24 с присоединением заявки М— (32) Приоритет—

Опубликовано 14.06.75. Бюллетень Хе 22

Дата опубликования описания 12.01.76 (51) }Ч.Кл. G OGf 5/00

Государственный номитет

Совета Министров СССР

IIII делам изобретений и отнрытии (53) УДК 681.325. .63 (088.8) (72) Авторы изобретения

В. А. Добрыдень, А. А. Рыжков, В. И. Куроедов, В, А. Батицкий и В. А. Березка

Харьковский ордена Трудового Красного Знамени государственный университет им. A. М. Горького (71) Заявитель (54) ФУНКЦИОНАЛЬНЬ1Й ПPЕОБРАЗОВАТЕЛb ЧИСЛОИМПУЛЬСНОГО КОДА В ДВОИЧНЬ114 КОД

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в составе автоматизированных систем управления.

Известны функциональные преобразователи число-импульсного кода в двоичный код, представляющие собой последовательное соединение линейного преобразователя число-импульсного кода и функционального преобразователя двоичного кода. Такие устройства громоздки и имеют недостаточное быстродействие.

С целью устранения этих недостатков в предложенном устройстве импульсная входная шина соединена с входами первого ключа и элемента запрета, управляющие входы которых соединены со знаковой входной шиной, выходы — с входами двух триггеров, единичный выход первого триггера соединен с входами элементов равнозначности и первого и второго счетчиков. Единичный выход второго триггера соединен со вторым входом первого элеме1гта равнозначности, выход когорого соединен с входом второго ключа. Импульсная входная шина соединена также с входом цепочки последовательно соединенных элементов задержки, выход первого из них соединен с входом второго ключа, выход которого соединен с входами ключей первой группы. Выход второго элемента цепочки соединен со счетным входом первого счетчика и через ключ второй группы — со счетным входом третьего счетчика, Выход 1-го элемента цепочки (= 3, 4, ..., ц + 1) соединен через к,.поч второй группы со счетным входом (1 — 1)-го разряда третьего счетчика, Разрядовые выходы первого счетчика соединены через коммутатор с входамп элементов «И», выходы которых через ключи первой группы и элемент «ИЛИ» соединены с входом второго счетчика, выходы которого через дешифратор соединены с входамн второго коммутатора, первый выход которого соединен с вторым входом второго элеме}гта рав}1означности, а

l5 оста Ibllblo и Выходов — — с Входами клlочей второй группы.

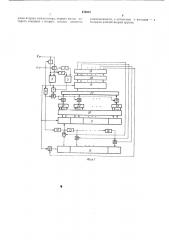

Г(а фнг. 1 приведена блок-схема устройства; на фнг. 2 — иллюстрирующий ее работу график.

Импульс`ая шина а соединена с рабочими входами ключа 1 и логического элемента запрета 2, управляющие входы которых соеди1:ены со знаковой шиной и. Выход ключа 1 соединен с сдиничпым входом триггера 3 и

25 через элемент 4 задержки импульсов — с единичным входом триггера 5. Выход элемента запрета 2 соединен с нулевым входом триггера 3 и чсрез эле;, ент 6 задержки, идентичньш элемент 4 — с пулевым входом триггера 5.

Единичный выход триггера 3 соединен с пер47400 ными входами логических элементов равнозначности 7 и 8, а также с управляющими входами реверсивных счетчиков 9 и 10. Единичный выход триггера 5 соединен со вторым входом элемента равнозначности 7.

Импульсная шина а соединена также со вхoдoм цепочки последовательно соединенных элементов 11, 12, ..., 14 задержки импульсов, число которых равно n + 1 (где ив число разрядов счетчика 15). Выход первого элемента цепочки соединен с рабочим входом ключа 16, управляемого выходом элемента равнозначности 7; выход второго элемента цепочки соединен со счетным входом счстчиli à 9 и через ключ 17 — со счетным входом первого (младшего) разряда счетчика 15. Выход i-го элемента цепочки (i = 2, 3, и + 1, т, с. элементов 13, ..., 14) соединен через отдельный ключ (соответственно ключи 18 и

19) со счетным входом (i — 1) -го разряда счетчика 15. Разрядовые выходы счетчика 9 через коммутатор 20 соединены со входами /г логических элементов «И» 21 — 23 (число /8 связано с числом участков аппроксимации воспроизводимой функции, выход каждого из которых через отдельный ключ (ключи 24—

26 — первая группа ключей) и через логический элемент «ИЛИ» 27, имеющий /г входов, соединен со счетным входом счетчика 10.

Коммутатор 20 позволяет соединять любой из

nz входов каждого из элементов «И» 21 — 23 с любым выходом счетчика 9, т. е. каждый из них может быть настроен на срабатывание (возбуждение) при любом наперед заданном состоянии счетчика 9.

Разрядовые выходы счетчика 10 соединены со входами дешифратора 28 потенциального типа, а его выходы — со входами коммутатора 20. Этот коммутатор, имеющий (и + 1) выход, позволяет соединять каждый из его выходов с любым подмножеством его входов.

Один из выходов коммутатора 29 соединен со вторым входом элемента равнозначности 8, а каждый из остальных п выходов — с управляющим входом одного из ключей второй группы (ключи 17 — 19).

Время задержки элементов 4 и 6 несколько меньше минимального интервала между входными импульсами, по превосходит время нсрсходных процессов в схеме. Времена за,ержки элементов 11 — 14 существенно меньше и выбраны так, чтобы к моменту появления импульса на выходе очередного элемента цепочки процессы в остальных элементах схемы (кроме элементов 4 и 6) были окончены.

Схема работает следующим образом.

Пусть воспроизводимая функция имеет внд, показанный на фиг. 2, ". е. 0 < V.: V", 0(W < W ", где V — входная величина устройства, W — выходная величина устройства, и пусть она аппроксимирована кусочнолинейной функцией с (k + 1) участками. Абсциссы и ординаты узлов аппроксимации обозначаются соответственно через V и W;, =

1,2,...,k,приэтом V8 = О, V = Г .

1

Функция F является по определению дискретной, однако при больших значениях числа разрядов счетчика 9 ni целесообразно говорить о линейной аппроксимации / в следующем смысле: Ill t-м участке аппроксимации (Г; i, V; ) едшьичпос приращение величины V (один в одной импульс) вызывает приращение W на величину 8,, s,.= (W,.-- W; i), (V; — 1 — >).

При этом величина s, может рассматриваться как крутизна t-го участка аппроксимации.

Если величина s,. оказывается дробной, представим ее в виде (s,) +

Поскольку функция F дискретна, скачок ее (см. фиг. 2) означает фактически наличие участка аппроксимации минимальной длины (V8 = 1 8 + 1), при этом $8 = 1 8 — 1 7).

Схема устройства реализует описанную аппроксимацию. Импульс, поступающий на шину а, проходит либо через ключ 1 — если величина V уменьшается (единичный потенциал ца шине o), либо через элемент запрета 2— при возрастании величины V (нулевой потенциал на шине б).

Соответственно триггер 3 устанавливается в единичное или нулевое состояние, переводя реверсивные счетчики 9 и 10 в нужный режим.

После окончания переходных процессов в схеме (спустя время задержки элемента 4 или

6) триггер 5 устанавливается в то же состояние, что и триггер 3. При этом ключ 16 в момент поступления на него импульса через элемент 11 будет открыт только в том случае, когда «знак» предыдущего импульса совпадает со «знаком» поступившего, так как в противном случае триггеры 3 и 5 в этот моменг находятся в различных состояниях, и следовательно, сигнал на выходе элемента равнозначности 7 отсутствует. В течение всего времени переходных процессов в схеме (время «обработки» одного входного импульса) единичный выход триггера 3 индицирует «знак» поступившего на шину а импульса.

Пусть величина з; записана в двоичной форме с числом и разрядов после запятой: о o (число ио разрядов перед за пой равно числу разрядов выходного кода), Каждому символу

o.z в двоичной записи S; соответствует специальный разряд счетчика 15, причем знаку ио к " — — старший, а знаку сР— младший.

Для реализации описанной аппроксимации

474001

Зо

65 достаточно каждый входной импульс подавать на счетные входы тех разрядов счетчика 15, которым соответствуют сдиницы в двоичной записи величины S;

B момент появления входного импульса ня выходе элемента 12 под высоким потенциалом находится единственная шина дешифратора 28, соответствуlolIIBII номеру участка аппроксимации, с крутизной которого должен быть обработан этот импульс счетчиком 15.

Пусть, например, i-и ключ второй группы (ключ i-го разряда счетчика 15) дол;кен быть открыт при воспроизведении первого, третьего и шестого участков аппроксимации (т. е. в записи SI, S и S6 величина а = 1), Тогда управляющий вход этого ключа должен быть с помощью коммутатора 29 соединен с выходными шинами дешифратора 28, соответствующими первому, третьему и шестому участкам аппроксимации. Аналогичное соединение управляющих входов всех ключей второй группы обеспечивает автоматическую установку нужной крутизны на каждом участке.

Знак крутизны задается следующим образом.

С помощью коммутатора 29 соединяют второй вход элемента равнозначности 8 с выходами дешифратора 28, соответствующими участками аппроксимации с положительной крутизной. При этом счетчик 15 просуммирует входной импульс только в том случае, когда: величина V уменьшается и S,. (О; величина V растет и S; ) О, что и обеспечивает правильное воспроизведение функции (в остальных случаях импульс будет вычтен, а при

= О режим счетчика несуществен, так как ключи всех разрядов закрыты) .

Номер текущего участка, на который попадает поступившип импульс, определяется в схеме следующим образом.

Перед началом работы счетчики 9 и 10 и триггер 5 устанавливаются в нулевое состояние, а счетчик 15 — — в состояние Г (О). В момент поступления входного импульса содержимое счетчика 9 представляет величину V.

Каждый из элементов «И» 21 — 23 (Ilx число равно числу узлов аппроксимации, в которых крутизна участков меняет знак) настроен с помощью коммутатора 20 на срабатывание при достижении счетчиком 9 состояний, соответствующих величинам 1 г (г =- 1, 2,..., /г-— 1). Пусть, например, VI ) О. Шина дешифратора 28, возбужденная при нулевом состоянии счетчика 10, является индикатором первого участка аппроксимацип. Пусть величина V растет от пуля. 1<,огда будет достигнуто значение VI возбуждается выход элемента

«И» 21, и ключ 24 открывается (остальные ключи первой группы при этом закрыты). Если V продолжает расти, очередной входной импульс проходит через открытые ключи 16 и

24, через элемент «ИЛИ» 27 и попадает на счетный вход счетчика 10, находящегося при этом в режиме суммирования. В результате возбуждается другая шина дешифратора 28, соответствующая второму участку аппроксимации. При этом открываются те к<почи второй группы, которые обеспечивают рсализацию крутизны Sg) и устанавливается нужный режим счетчика 15, а спустя необходимое для этого время импульс с выходя элсмснтя 12 начинает посл сдовятс, н НО llo тмпять и я poop 0;I I I счетчика 15.

Если по достпжснпп вслпчшн1й 1 зн;шенин

1 (оня начнет умсш.шяться, очередной llìпульс опрокинет триггер 3 в единичное состояние, благодаря чему в момент поступления этого импульса íà вход ключа 16 Oн закрывается, т. е. содержимое счетчика 10 не изменится, что и требуется, тяк как величина V при этом остается в пределах первого участка аппроксимации, Прп прохождении точки VI в случае уменьшения 1 — со второго участка на первый — схема работает аналогично, но счетчик 10 находится в режиме вычитания.

Таким образом, состояние счетчика 10 всегда однозначно соответствует номеру участка, с

I

Предмет изобретения

Функциональный преобразователь числоимпульсного кода в двоичный код, содержащий счетчики импульсов, логические элементы, ключи, триггеры, коммутаторы, дешифратор и элементы задержки, от.гигагошнггся тем, что, с целью упрощения и повышения быстродействия устройства. импульсная входная шина соединена с входямп нсрвого ключа и элемента запрета, управляющие входы которых соединены со знаковой входной шиной, выходы — с входамп двух триггеров, сдгшичный выход первого триггера соединен с входамп элементов равнозначности и первого и второго счетчиков, а единичный выход второго триггера соединен с вторым входом первого элемента равнозначности, выход которого соединен с Входом BTopol o кл (очя; импульсная Входи я)1 шина соединена (яг<н<е с входом цепочки lloследовательно соединенных элементов задержки, выход первого из нпх соединен с входом второго ключа, выход которого сосдпнсн с входамн ключсй первой группы, выход Blоporo элемента цепочки сосдпнсн со счспп»м входом первого счет шка и чсрсз ключ втopol! г1гуппы — co счстным Входом третьего счс1 чика; выход (.-го элемента цепочки (i = 3, - ., ..., и + 1) соединен через ключ второй группы со счетным входом (i — 1) -го разряда третьего счстчика: разрядовые выходы первого счетчика соединены через коммутатор с входами элементов «И», выходы которых через ключи первой группы и элемент «ИЛИ» соединены с входом второго счетчика, выходы которого через дешифратор соединены с вхо474001 дами второго коммутатора, первый выход которого соединен с вторым входом элемента равнозначности, а остальные и выходов — с входами ключей второй группы.

474001

И 5

9(б

4а1

W1Ï

Wg

Wg

W) г

О

Ча V,,Чг

Ч7 Ч Чщ Ч

Уб Ч11

Ч Ч Чб

Фиг. 2

Составитель В. Добрыдень

Техред М. Семенов

Корректор Н. Лебедева

Редактор Е. Семанова

Подписное

МОТ, Загорский филиал

Заказ 5998 Изд, ¹ 1511 Тираж 679

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий, Москва, 7К-85, Раушская наб., д. 4/5