Ячейка памяти

Иллюстрации

Показать всеРеферат

(1ц 546935

О0ИСАНИЕ

ИЗОБРЕТЕН И Я

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (6l) Дополнительное к авт. свид-ву (22) Заявлено 01.02.74 (21) 1991919/24 с присоединением заявки Х (23) Приоритет

Опубликовано 15.02.77. Бюллетень М 6 (51) М. Кл.2 С 11С 11/40

Государственный комитет

Совета Министров СССР

t53) УДК 681.327.66 (088.8) ло делам изобретений и открытий

Дата опубликования описания 17.03.77 (72) Авторы изооретения (71) Заявитель

Н. А. Аваев и Ю. Е. Наумов

Московский ордена Ленина авиационный институт им. Серго Орджоникидзе (54) ЯЧЕЙКА ПАМЯТИ

Изобретение относится к микроэлектронике.

Известны интегральные ячейки памяти, содержащие два транзистора с перекрестными связями, базы которых соединены с коллекторами р-п-р-транзисторов, эмиттеры которых подключены к шине выборки. Этп ячейки характеризуются сложностью управления, необходимостью электрической изоляции одной от другой ячейки различных строк накопителя, а 10 также необходимостью изменения напряжения на адресных шинах при выборке, что приводит к появлению импульсных помех и требует повышения напряжения источника питания схемы памяти. Наиболее близким к изоб- 15 ретению техническим решением является ячейка памяти, содержащая первый п-р-п-транзистор и второй многоколлекторный п-р-п-транзистор с перекрестными связями, третий и четвертый п-р-п-транзисторы, кол- 2О лекторы которых соединены соответственно с коллектором первого и-р-п-транзистора и первым коллектором второго п-р-и-транзистора, пятый n-p-n-транзистор, база которого соединена со вторым коллектором второго п-р-и- 25 транзистора, а коллектор — с разрядной шиной, шестой и седьмой п-р-п-транзисторы, коллекторы которых соединены соответственно с базами третьего и четвертого п-р-п-транзисторов, причем база седьмого п-р-п-транзистора 3О соединена со второй разрядной шиной, восьмой многоколлекторный р-п-р-транзистор, коллекторы которого подключены соответственно к базам первого, второго, шестого и седьмого п-р-п-транзисторов, а эмиттер — к шине питания, шину нулевого потенциала и шину выборки. Эта ячейка является сложной, так как она имеет трп разрядных шины, второй многоколлекторный р-п-р-транзистор, а также дополнительные и+ области для разделения п-р-п-транзисторов.

Целью изобретения является упрощение ячейки. В описываемой ячейке достигается тем, что она содержит девятый многоколлекторный п-р-п-транзистор, база которого подключена к шине выборки, а коллекторы — соответственно к базам третьего, четвертого и пятого п-р-п-транзисторов, дополнительный коллектор четвертого п-р-п-транзистора, соединенный с базой пятого п-р-п-транзистора, причем база шестого п-р-п-транзистора соединена с коллектором пятого п-р-п-транзистора, четыре дополнительных коллектора восьмого р-п-р-транзистора, соединенные соответственно с базами третьего, четвертого, пятого и девятого п-р-п-транзисторов.

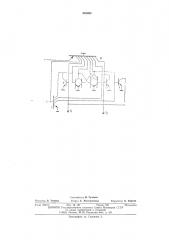

На чертеже показана электрическая схема описываемой ячейки.

Она содержит транзисторы 1 и 2, образующие бистабильный элемент, транзисторы 3 и

546935

4, коллекторы которых соединены с коллекторами транзисторов 1 и 2, входные транзисторы 5 и 6, на базе которых с разрядных шин

Уь У2 подаются сигналы записи, транзистор

7, служащий для вывода информации при считывании, р-n-p-транзистор 8, управляющий режимом работы (выборка или хранение) и п-р-и-транзистор 9, задающий ток питания в базы всех п-р-п-транзисторов.

В режиме хранения на базу транзистора 8 подается сигнал «логической единицы» (ток в шине Х равен «0»), транзистор 9 — включен, а транзисторы 3, 4 и 7 — закрыты. Сигналы с шин У1 и Yq не могут пройти на базы транзисторов 1 и 2, и триггер на этих транзисторах хранит информацшо. В свою очередь сигнал с выхода триггера не может пройти на шину Уь так как транзистор 7 закрыт.

В режиме выборки на базу транзистора 8 через шину Х подается сигнал «логического нуля», запирающий этот транзистор.

В режиме записи на разрядных шинах в противофазе устанавливается нужная информация, которая и записывается в триггер.

Например, если,на шине Yi — сигнал «0», а на шине Y2 — сигнал «1», то транзистор 5— выключен, а транзистор 3 включается, и на левом плече триггера (коллектор транзистора

1) устанавливается «0».

В режиме считывания на шине У устанавливается сигнал «логической» единицы (ток в шине равен «0»), а шина У подключается ко входу усилителя считывания. Сигнал на шине определяется состоянием триггера. Если транзистор 1 включен, то на шине У1 появляется сигнал «логического нуля» (напряжение, близкое к«0», поддерживаемое открытым транзистором 7). Если транзистор 1 выключен, то сигнал на шине У1 соответствует «логической единице» (ток в шине равен «0»).

Описываемая ячейка, в отличие от известных, содержит две, а не три разрядных шины, что упрощает создание межсоединений и уменьшает площадь накопителя. Кроме того, в ней нет необходимости во втором многокол15

)(30

40 лекторном р-п-р-транзисторе II разделительных п областях, требующих для своего создания дополнительной технологической операции. Этим достигается положительный эффект — упрощение ячейки н накопителя.

Формула изобретения

Ячейка памяти, содержащая первый п-р-птранзистор и второй многоколлекторный п-р-и-транзистор с перекрестными связями, третий и четвертый n- p-n-транзисторы, коллекторы которых соединены соответственно с коллектором первого п-р-и-транзистора и первым коллектором второго п-р ï-транзистора, пятый п-р-п-транзистор, база которого соединена со вторым коллектором второго п-р-птранзистора, а коллектор — с разрядной шиной, шестой и седьмой n-p-n-транзисторы, коллекторы которых соединены соответственно с базами третьего и четвертого п-р-п-транзисторов, причем база седьмого и-р-и-транзистора соединена со второй разрядной шиной, восьмой многоколлекторный р-п-р òðàíçèñòîð, коллекторы которого подключены соответственно к базам первого, второго, шестого и седьмого п-р-п-транзисторов, а эмиттер — к шине питания, шину нулевого потенциала и шину выборки, отличающаяся тем, что, с целью упрощения ячейки памяти, она содержит девятый многоколлекторный п-р-птранзистор, база которого подключена к шине выборки, а коллекторы — соответственно к базам третьего, четвертого и пятого и-р-птранзисторов, дополнительный коллектор четвертого п-р-п-транзистора, соединенный с базой пятого п-р-п-транзистора, причем база шестого п-р-п-транзистора соединена с коллектором пятого п-р-п-транзистора, четыре допо:.н«тельных коллектора восьмого р-и-ртра«з«стора, соединенные соответственно с оазами третьего, четвертого, пятого и девятого п-р-п-транзисторов.

546935 г

Составитель В. Туляков

Текред Е. Жаворонкова

Корректор О. Тюрина

Редактор Л. Тюрина

Типография, пр. Сапунова, 2

Заказ 330715 Изд. № 187 Тираж 769 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5