Устройство для контроля интегральных схем

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Йаюз Советских

Социалистических,IlI553230

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 26.09.75 (21) 2174675 25 (51) М. Кл. - G 01R 31/26

G 06I. 15 46 с присоединением заявки №

Государственный комитет

Совета Министров СССР по делам изобретений и открытий (23) Приоритет

Опубликовано 15.05.77. Бюллетень ¹ 18

Дата опубликования описания 21.06.77 (53) УДК 621.382.3 (088.8) (72) Автор изобретения

В. В. Терпигорьев (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ИНТЕГРАЛЬНЫХ СХЕМ

Изобретение относится к области измерения параметров интегральных схем.

Известны устройства для контроля интегральных схем, построенные на базе цифровой техники и содержащие программные источники напряжения, коммутаторы, аналогоцифровые преобразователи, логические схемы и индикаторы (1, 2) . Такие устройства универсальны, однако имеют высокую стоимость и сложны в эксплуатации.

Известно устройство для измерения параметров интегральных схем, содер кащее коммутатор, соединенный с блоком первичных преобразователей и аналого-цифровым преобразователем, блок управления, задатчик граничных значений, счетчик импульсов, регистры групп, логические схемы и индикаторы (3).

Однако это устройство имеет низкую скорость контроля (4 — 5 операций в секунду), что снихкает точность измерений.

Для повышения скорости контроля с одновременным увеличением его точности в предлагаемое устройство введены схема однозначности и коммутатор граничных значений, вход которого соединен с аналого-цифровым преобразователем, а выход — с задатчиком граничных значений, подключенным к логическим схемам, вторые входы которых соединены с выходами аналого-цифрового преобразователя, а выходы — со cxci>IQA совпадения, подключенной последовательно к счетчику импульсов, регистру групп, cxcxlc неоднозначности и индикаторам.

Кроме того, каждая 7огп11сская схсМ3 со5 держит два IIHBcI7TOp3, 1 аkli7biil пз IloTopbix сосдпнсп с первым э7exiei<7oxl 11 — ИГ, второй вход которого соединен с выходом пнвертора противоположного h2kl3 72, 3 Выход — co вторым э7ciieHToxi И вЂ” IIE, второй вход которого

10 соеу»»сН с выходом предыдущего элемента

11- — HE в порядке уменыпсния разрядов групп классификации, а выход элемента И вЂ” 1 IЕ старшей группы соединен со схемой совпадения.

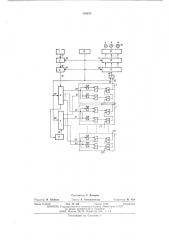

15 На чертеже показана схема описываемого устройства, содержащего испытываемую интегральную схему 1, подключенную к блоку первичных преобразователей 2, коммутатор параметров 3, аналого-цифровой преобразова20 тель 4, задатчпк граничных значений О, коммутатор I p2HHiIHbix значений 6, логических схем обработки 7, где Л вЂ” число двоичных разрядов преобразователя 4, состоящих из двух инверторов 8, двух первых 9 и двух вто25 рых 10 двувходовых элеxicHToB 11 — HE, двувходовую схему совпадения 11, счетчик импульсов 12, регистр групп классификации 13, CX 2 1 i O.7kIO3H3HH icT1l 14, IIHHHHB TO)> 1 о H n,7OIi управления 16. Выходы 17 после,1уемой инте30 гральной схемы через блок первичных преоб558230 разоватслей 2 соединс!!ы с входом 18 коммутатора параметров 3, 11ыход котор(,го 19 соединен с аналого-цпфровыAI прсоорà",îâàтслсм

4. Д 13 О и 1 «Ы С 13 Ы Х 0 Д Ь1 I I p C O O p 2 2 0! 3 ll T C, 1 S! 4 н 0:l кл!Очены к Вход2м 20 10ГИ 1сск1!х схем Об(32ботки 7, а однопме«пыс Выхо;ill 32. тч«ка гранич«ых значс«ий 5 — — к .3ходам 2! эт«х схем. Логические схемы ооработкп 7 «клю !сны последовательно в порядке 130зрастап!я Вссов двоич«ых разрядов так«х! обраaoì, что выход 22 (n — 1)-Й схемы подключен к Входу

23 и-й схемы, причем Л вЂ” стари!«Й ..!!3оп:!н!.1« разряд. Выход 22 лог«1сской схс;1ы обработки 7 связан с первым Входом схемы сов«а lcния 1 1, ВыхОд котopoff подклlочсп I(c !сг«0. 1 входу 24 счетчика импульса 12. Выхо:if c»ciчика импульсов 12 через регистр групп классификации и схему однозначности 14 связа:!ы с индикатором групп 15. Выходы О,!Ока у»(3213ления 16 подключены к входу 25 бло а первичных преобразователей 2, к входу 26 коммутатОра парамстрОВ 3, к зан, ск2101цс 1 13. ;0ду 27 аналого-цифрового прсобразoi«a i c;i» 4, к входу 28 задатчика гра«пчны((зпа Ic«II« 5, к импульсному входу 29 схемы равно-.«à:«îсТН 1 1 1! 1(сбросовым Входам 30 li 31 с !с 1 !Икa импульсов 12 If регистра групп классификации 13. Выход коммутатора гра«пч«ых з«ачсIlHH 6 подкл!о !Сн к В .Од; 32 задатiili: 2 ничных значений 5.

Устройство работает слс j)ющим образом.

Выход 17 исследуемой интегральной схемы 1 подключен к блоку первпч«ых преобразователей 2, где формируется инфорх!ацпя оо измеряемых параметрах, которая поступает на вход 18 коммутатора параметров 3. Блок управления 16 по выходу 26 формирует управ1яющий сиГ«ал «а н(10ГРамм1iый ком!! "1 2!ÎP

3 для поочередного подключс«пя ко«тролпруемых параметров на вход 19 преобразователя аналог-код 4. Величина контролируемого параметра П в цпфроьом коде и" ñòóïàåò «а входы 20 логических схем обработки ячеек 7, а величина граничного значения à — Ifa Входы 21. Если на в: оде 20 ячейки старшего разряда присутствует нулевой сигнал, а па входе 21 — единич«ый, то на выходе первого элемента И вЂ” HE 9 появптся нулевой сг!Гнал, а «2 выходе первого элемента И -IIE 10, т. е. «а входе 22 схемы совпадения 11, появится единичный, что соответствует результату сравнения П(Г. Если па вход 20 этой ячей и подан единичный сигнал, а на вход 21 — пулевой, то на выходе первого элемента 9 поя!3«тся единичный, а на Выходе второго элс;ic 11а 9— нулевой сигнал. На вход первого элемента 10 с выхода второго элемс«та 10 поступит единичный сигнал, и на входе 22 схемы совпадения 11 появится нулевой сигнал неза!3«сп lo от состояния входов 20 и 21 ячеек младших разрядов, что соответствует рсзул тату сравнения П)Г. Если Ila входы 20 и 21 ячейки старшего разряда поданы од«оимснныс спг«алы, то на выходах обоих элементов 9 и-псутствуют единичные сигналы и состоя«ис дру)

1.,1

15 0

ЗО

-!0

53

QO

If# элементов 10 не о:1рсделено. В этом слу ас резгл!> 1 ат ср !1!3«с«1! я будет О«рсдс;1!!тьс!1 (30«1!ям« 13ходных с«Г!ia;ioi3 соссд«сЙ млад«!clf iiiei:.i(li. Е=c,111 iia н!!!не 20 этОЙ я !Сйк3! присутствует нулевой сигнал, а на шине 21 сдп«п шый, то»a выходе первого элемента 10 этой ячейки появ1«гся сднничнь!й сигнал, который Воздействует «а элементы 10 ячейки старшего разряда таким образом, что «а 13ходе 22

«ояв«тся сди«ичный сигнал (П(Г). При про1«13011010 ê«û.: уровня; сигналов на входах ячсики (!! — 1) -го разряда нулевой сигнал с вы (0.(а элсмс«та 10 предопределит пулевой уровш!ь «а входе 22 схемы совпадения 11 (lI) I ). В случае равенства входных сигналов Л-ой и (Л вЂ” 1)-ой ячейки результат сравнен«!! Оудст определяться уровнями, записанными «а входах последующей младшей ячейкиит.д.

После окончания переходного процесса в блоке первичных преобразователей 2, в котором сформирована с. åìa измерения первого

»apa;»lc1pa, от блока управления 16 по выходу 27 запускается аналого-цифровой преобра3013атель 4, который своим импульсом «êîíåö измерения» запускает коммутатор граничных значений 6. 1(-Тому времени по коман.!е с блоки управлс«ия 16, поступившей на вход 28 задатчика граничных значений 5, в последнем подготовлена к опросу группа шин граничных значений данного параметра, причем грани шые значения набраны в убывающем порядке, и по входу 29 подготовлена к пропускангцо импульсов схема совпадения 11. Коммутатор граничных значений 6 поочередно подкгпочает эти шины к входам 21 логических схем обработки 7. Если значение измеренного параметра находится между m-ым и (m+1)-м граничным значением, то на счет«ый вход 24 счетчика импульсов 12 поступят импульсы и перебросится в сди«ичное состоя«ие m;ая вы од«ая шина счетчика 12. Результ2т классифик2ции по пе(ЗВОму параметру 32 похцгнается в регистре групп классификации

13 и через схему однозначности 14 поступает на индг!катор, включая лампу т-ой группы, Далее управляющее устройство 16 по выходу

25 формирует в блоке первичных преобразователей 2 схему измерения второго параметра, по выходу 30 сбрасывает счетчик импульсов 12 в исходнос состояние, по входу 26 подключает измеритель к входу преобразователя

«аналог вЂ к» 4, по Входам 29 и 28 подготавливает схему совпадения 11 и группу шин грани 1«iix значений, соответствующих второму параметру, в задатчике граничных значе.«Ий и после окончания переходного процесса по Выходу 27 запускает преобразователь 4. По око«ча;!ии процесса счета вступает в работу коммутатор граничных значений 6, и на вход счстч:!ка поступает I импульсов, Для исключеп я загора«пя одноврсмен«о двух или нескольк1!х лампочек индикатора групп 15 в устройство В!3сдсца схема однозначности 14, коi op!»i зarf;;cii!acт загорание предыдущей лам558230 почки при включенной последующей. Таким образом, если исследуемая интегральная схема по одному параметру удовлетворяет группе т, а по другому — группе l, причем l— худшая группа, то на индикаторе загорается лампочка группы l. Дальнейшая работа классификатора аналогична вышеописанному.

Логические схемы обработки 7 идентичны и при использовании вместо элементов И вЂ” НЕ элементов ИЛИ вЂ” НЕ работоспособны при любом коде преобразователя аналог-код.

Формула изобретения

1. Устройство для контроля интегральных схем, содержащее коммутатор, соединенный с блоком первичных преобразователей и аналого-цифровым преобразователем, блок управления, задатчик граничных значений, счетчик импульсов, регистры групп, логические схемы и индикаторы, отличающееся тем, что, с целью повышения точности и скорости измерений, в него введены схема однозначности и коммутатор граничных значений, вход которого соединен с аналого-цифровь1м преобразователем, а выход — с задатчиком граничных значений, подключенным к логическим схемам, вторые входы которых соединены с вы. одами аналого-цифрового преобразоватсля, а выходы — со схемой совпадения, подключенной последовательно к счетчику импульсов, регистру групп, схеме неоднозначности и

5 индикаторам.

2. Устройство по и. 1, отличающееся тем, что каждая логическая схема содержит два инвертора, каждый пз которых соединен с первым элементом И вЂ” НЕ, второй вход кото10 рого соединен с выходом инвертора противоположного канала, а выход — со вторым элементом И вЂ” НЕ, второй вход которого соединен с выходом предыдущего элемента И вЂ” НЕ в порядке уменьшения разрядов групп клас15 сификации, а выход элемента И вЂ” HE старшей группы соединен со с. емой совпадения.

Источники информации, принятые во внимание при экспертизе:

2О 1. Авторское свидетельство СССР _#_o 393748, М. Кл. 06 15/46, 1973.

2. Авторское свидетельство СССР Хо 390530, М. Кл. 06 15/46, 1973.

3. «Автоматический контроль радпоэлек25 тронного и электротехнического оборудования», Энергия, М., 1972, стр. 229 †2 (прототип).

55823() Составитель Т. Дозоров

Текред А. Камышникова

Корректор Н. Аук

Редактор И. Шейкин

Типография, пр. Сапунова, 2

Заказ 1154/13 Изд. № 426 Тираж 1106 Подписное

ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий

1 13035, Москва, Ж-35, Раушская наб., д. 4 5