Интегральная ячейка памяти

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

Сова Соеекнии

Сеармйнстюнкжна

Ф кйубйин ((l) 56626 8

М @МОРСКОМУ СЭИДЙ1ВЛЬСУВУ (В4) Лополнйтельное к авт. свил-ву-(И) Заявлено 27.12.73(2!) 1э822эоб24 е прнеоеамнением заявки _#_e— (23) Прноритет(43) Опублнноваио 25. 07. 77 Бюллетень ¹ 27 (5!) м, кл

С 11 С I 1140 аВ9ЭЭФВтаэваФ кемщфю

4Маата Ваяи1а» 6661 в авен вмбрвтееа и Фщнтю (53) УЙК681. 327.66 (088. 8) (4® Дата опубликования описания 271о.77 (72) Ааторм ваобретенив

H.A. âàåâ, В.П.Демин, В.Н.Дулин и IO.E.Íàóìoâ (Щ Заменитель

Московский ордена Ленина авиационный институт им. Серго Орджоникидзе (54) ИНТЕГРАЛЬНАЯ ЯЧЕЙКА flANIITH

Изобретение относится к микроэлек ронике.

Известны интегральнЫе ячейки памяти, годержашие два -р-и- транзистора с перекрестными связями, базы которых соединены с двумя коллекторами р-н-р- транзистора, эмиттер которого подключен к шине выборки fl),f2).

Однако сложность управления, необходимость электрической изоляции друг от друга ячеек различных строк накопителя, а также необходимость в.менения напряжения на адресных шинах при выборке приводит к появлению импульсных йомех и требует повнаения напряжения источника питания схемы памяти °

Наиболее близким к изобретению техническим, решением является интегральная ячейка памяти, содержащая два й-р-и- транзистора с перекрестными связями, третий и четвертыя и р.и транзисторы, коллекторы которых соединены соответственно с коллектором первого и первым коллектором второгФп-р-й-транзисторов, второй коллентор которого соединен с базоя пятого п--р-п-транзистора, а коллектор пятогос первой разрядной шиноя У, шестой и-p-i: — транзистор, коллектор которого соединен с базой третьегоп-р-l1— транзистора; базы первого н второго и-р-п - транзисторов соединены соответственно с первым и вторым коллекЭ торами первогор-и-р -транзистора, змитгер которого подключен к шине питания, базы третьего, четвертого и пятого и-р-п - транзисторов, соответственнок первому, второму, и третьему коллекторам второгор.п-р- транзистора, эыиттер которого подключен к шине выборки К, эмиттеры всехп-рии баэыр-и-ргранзисторов подключены к шине нулевого потенциала(3) ° Однако большая потребляемая мощность ячейки обусловлена тем, что в режиме выборки ток питания должен быть одинаков для scex ячеек.

Цель изобретения - снижение потребляемой мощности ячейки.

Достигается это тем, что ячейка содержит диоды Шоттки, аноды которых подключены к базам шестого и четвертогоя р.п- транзисторов соответствеH но, катоды - к первоЯ н второЯ разрядным шинам У,н У соответгтвенно, а sòîðîé р-гг- p - транзистор годержнт четвертыЯ, плтый и ше -той допол566268 нительные коллекторы, подключенные соответственно к базам первого, второго и шестогои-р-и - транзисторов.

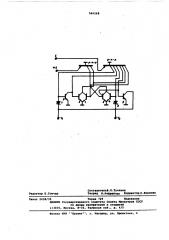

На чертеже дана электрическая схема ячейки.

Ячейка работает следующим обра зом. Ток питания в транзисторы 1 и 2, образующие триггер, задается от внешнего источника с помощью первого 1( двухколлектг ного р-и-p — транзистора,. эммитер которого, подключен к шине питания B. Транзисторы:,1 и 2 полностью изолированы от разрядных шин

Y Y и триггер хранит информацию.

В режиме хранения ток в шине выборки

Х равен О, поэтому транзисторы 3 - 6 закрыты.

В Режиме выборки во второй р-И-ртранзистор по Х шине задается большой ток, благодаря чему возрастает ток питания в цепи баз всех tt-р-И- транзисторов всех ячеек одного слова, в то время как в других словах транзисторы 3-6 по-прежнему выключены а в транзисторы 1 и 2 поступает тот же 26 малый ток, что и в режиме хранения.

В режиме записи на обоих шинах Y Y устанавливается либо сигнал логического Ä 0 (напряжение, близкое к О), либо сигнал логической l (ток к 30 шине равен О) . Этот сигнал записывается в триггер и появляется на коллекторе первого и-р-и- транзистора.В режиме считывания на шине У> устанавливается уровень логического "О, а шина Y подключается к входу усили-! теля считывания. Сигнал на шине У1 определяется состоянием триггера.

Если первый«р«-.. xðàíýèñòîð включен, то на шине tпtОdtяtвsлzя«еeтeсcяa,сигнал логического "О ".(напряжений,. близкое,к О); если первый и-р- Й. - транзистор выключен, то сигнал, на шине соответствует логической "1" †:(ток в шине равен О) .

Напряжение прямого смещения диодов Шоттки 7, B должно быть ниже нап-. ряжения отпирания и-р.и - транзисторов., Диоды Шоттки выполняют роль электри-, ческой развязки ячеек разных слов друг от друга, входы которых объединены разрядными шинами. Благодаря этому при выборке большой ток питания, необходимый для получения высокого быстродействия, можно задать только в ячейки одной выбранной строки. Мощность потребляемая всеми ос- @ тальными ячейками накопителя, остается пренебрежимо малой. В.накопителе, построенном на ячейках прототипа 3 все ячейки в режиме выборки потребляют одинаковую мощность ° . Следовательно, применение предлагаемой ячейки памяти позволяет при сохранении того же быстрЬдействия снизить мощность, потребляемую накопителем в режиме выборки в N раз, где М число слов накопителя. Благодаря этому достигается полезный эффект.

Формула изобретения

Интегральная ячейка памяти, содер жащая дваи-р-и-транзистора с перекрестными связями, третий и четвертый и-р-и транзисторы, коллекторы которых соединены соответственно с кол" лектором первого и первым коллектором второго и-p-n -транзистора, второй коллектор которого соединен с базой пятого и-р-и — транзистора, а коллектор пятого — с первой разрядной шиной У, шестой и-р-и - транзистор; коллектор которого соединен с базой третьего tt-р-и — транзистора, .базы первого И второго.и-р-rt- транзисторов соединены соответственно с первым и вторым коллектором первого (з-и-p - транзистора, эмиттер которого подключен к шине пйтания,:базы третьего, четвертого и пятого pt-p-t7 - транзисторов - соответственно к первому, второму и. третьему коллекторам второго р-и -р -. транзистора, эмиттер которого подключен к шине выборки Х, эмиттеры всех и-р-и и базы р-и-р - транзисторов подключены к шине нулевого потенциала, отличающаяся тем, что, с целью снижения потребляемой мощности ячейки, она содержит диоды Шоттки; аноды которых подключены к базам шестого и четвертого и-р-и — транзисторов соответственно,, катоды — к первой и второй разрядным шинам Yt«У соответственно, а второй р-и-p — транзистор содержит четвертый, пятый и шестой дополнительные коллекторы, подключенные соответственно к базам первого, второго и шестого и-р-и - транзисторов.

Источники информации, принятые во внимание при экспертизе:

1. Журнал Efecf robics, 1972, 46, В 4 Р.BЗ.

2. Журнал ЗЕЕЕ j of 9aPid state Circuits"

1973, V - -8, 9 5, Р.332.

3. Патент Франции В 2138905, М., Кл. Н 01С,,19/00 от 22.05.71.

566268

Соетавнтелъ|.Л.Туляков

Твмрад Н.Андрввчук Хорректор С.Ямалова

Редактор Е.Гончар

Филиал ППП Патент, г. Уагород, ул. Проектная, 4

Заказ 2438/35 Тирам 739 . Подгэеноа

tlHKHtlH Государственного комнтета Совета йнннетров СССР по дэнам нэобратюннв н Открытнй

) l3035 Носква, Ж-35, Рауюская наб., д. 4/5