Устройство для мажоритарного декодирования

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (») 607 349

i

l е (61) Дополнительное к авт. свид-ву (22) Заявлено 24.11.75 (21) 2192942/18-2 с присоединением заявки № (23) Приоритет (43) Опубликовано 15.05. 78, Бюллетень %1 (45) Дата опубликования описанияф6.05. Щ (51) М. Кл.

Н 04 L 1/10 б- 06 Р 11/08

Государственный комитет

Совета Министров СССР оо делам нзооретений и открытий (53) УДК 681.326.7 (088,8) (72) Авторы изобретения

В. И. Верховцев и Е. А. Шурмухин (71) Заявитель (54) УСТРОЙСТВО ДЛЯ МАЖОРИТАРНОГО ДЕКОДИРОВАНИЯ

Устройство предназначено для использования в вычислительной технике и в радиотехнических системах.

Известно устройство для мажоритарного декодирования циклических кодов, содержащее ю регистр сдвига, сумматоры по модулю два, мажоритарные элементы (1) .

Наиболее близким техническим решением к изобретению является устройство для мажоритарного декодирования, содержащее регистр сдвига, вход которого является входом уст- 0 роиства, а разрядные выходы соединены с первой группой входов блока сумматоров по модулю два, при этом выходы блока сум маторов по модулю два соединены с первой группой входов блока мажоритарных элементов, выходы которого являются выходами устройст- l5 ва (2) .

Недостатком известных устройств является большой объем оборудования, обусловленный большим числом сумматоров по модулю два.

Целью изобретения является упрощение уст2о ройства, Это достигается тем, что устройство содержит блок управления, группу элементов Й и группу элементов ИЛИ, причем разрядные выходы регистра сдвига соединены с первыми 25

2 входами соответствующих элементов И группы, вторые входы которых соединены с первой группой выходов блока управления, выходы группы элементов И через группу элементов ИЛИ соединены с второй группой входов блока сумматоров по модулю два, вторая группа выходов блока управления соединена с второй группой входов блока мажоритарных элементов.

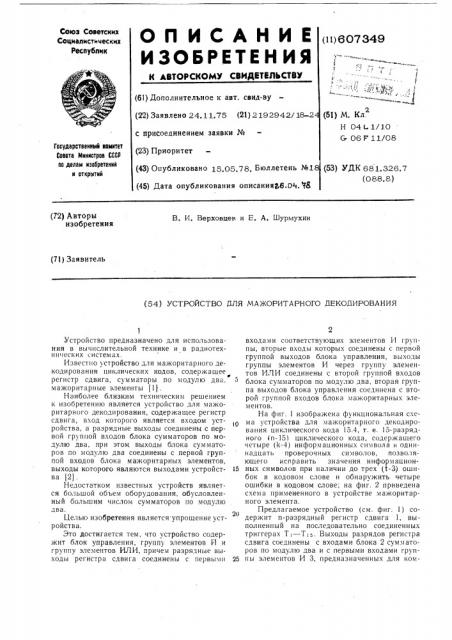

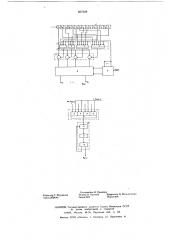

На фиг. 1 изображена функциональная схема устройства для мажоритарного декодирования циклического кода 15.4, т. е. 15-разрядного (и-151 циклического кода, содержащего четыре (k-4) информационных симвопа и одиннадцать проверочных символов, позволяющего исправить значения информационных символов при наличии до трех (t-3) ошибок в кодовом слове и обнаружить четыре ошибки в кодовом слове; на фиг. 2 приведена схема примененного в устройстве мажоритарного элемента.

Предлагаемое устройство (см. фиг. 1) содержит и-разрядный регистр сдвига 1, выполненный на последовательно соединенных триггерах Ti — Т15. Выходы разрядов регистра сдвига соединены с входами блока 2 сумматоров по модулю два и с первыми входами группы элементов И 3, предназначенных для ком607349 мутации выходов регистра сдвига к входам блока сумматоров. Выходы группы элементов И через группу элементов ИЛИ 4соединены с входами блока 2 сумматоров. Вторые входы группы элементов И соединены с входами блока управления 5, формирующего циклически повторяющиеся серии командных импульсов.

Выходы блока сумматоров соединены с первой группой входов блока 6 мажоритарных элементов, вторая группа входов которого соединена с блоком управления, 0

Рассмотрим работу устройства для мажоритарного декодирования:на примере декодирования кода 15.4, который позволяет исправить три и обнаружить четыре ошибки. Для кода 15.4 имеем следующие правила кодирова15 ния: а5 — àI+a

35 — 32+ а

37 =35+34

3Iq=aIo+aII 20

aI5=aII+3It

В соответствии с правилами кодирования имеем следующую систему проверочных соотношений для символа а .

3 I =- 3 I

aI =-32+35 а1= 3 +3>

3 I = 3 I 2+31 а = 35 + 311 а1= ав+BIQ 30

a, — à +àI а I =- 3 + a I5

Аналогичная система может быть составлена относительно любого из символов.

Циклические свойства кода гарантируют, что каждая проверка для символа может з быть получена из проверки относительно сим. вола а1 путем ее циклического сдвига.

Указанные системы уравнений определяют связи входов сумматоров с выходами регистра сдвига.

На вход регистра сдвига 1, состоящего из последовательно соединенных триггеров Т I — Тд5, поступает последовательный код информации.

Кодовое слово записывается в регистр за 15 тактов сдвига. В процессе записи информации 45 в регистр сумматорами по модулю дза блока 2 производится вычисление проверочных соотношений для символов кода, Подключение выходов регистра сдвига к входам блока 2 сумматоров производится непосредствено и че50 . рез группу элементов И 3 и группу элементов ИЛИ 4 логическими ключами путем стробирования сигналов регистра сдвига импульсами с блока управления 5.

С выходов блока сумматоров. сигналы результатов контрольных проверок поступают на вход блока 6 мажоритарных элементов, которые принимают решение о значении а, символа. Мажоритарный элемент (см. фиг. 2) содержит узел 7 оценки результатов контрольных проверок на элементах И 8 и ИЛИ 9 двоичный счетчик 10 на триггерах 11, !2 и !3, На узлах оценки результатов контрольных проверок (результатов вычисления проверочных соотношений) сигналы с выходов блока 2 сумматоров опрашиваются ком анди ым и им пульсами блока управления 5. На выходе узлов оценки 7 имеем импульсный сигнал, количестве импульсов в котором определяется числом «!» по результатам контрольных проверок. С выхода узлов оценки импульсный сигнал подается на вход двоичного счетчика 10. Для упрощения анализа счетчик охвачен цепью обратной связи, запрещающей счет, когда он установится в состояние + l, где m — число проверочных соотношений для примененного кода (в нашем примере m =-8). Значение символа а; определяется состоянием последнего (13) триггера счетчика. Декодированная информация появляется на выходе устройства сразу после записи ее во входнои регистр сдвига, Предлагаемое устройство для мажоритарного декодирования проще известного за счет уменьшения числа сумматоров по модулю два.

Формула изобретения

Устройство для мажоритарного декодирования, содержащее регистр сдвига, вход которого является входом устройства, а разрядные выходы соединены с первой группой входов блока сумматоров по модулю два, при этом выходы блока сумматоров по модулю два соединены с первой группой входов блока мажоритарных элементов, выходы которого являются выходами устройства, отличающееся тем, что, с целью упрощения устройства, оно содержит блок управления, группу элементов И и группу элементов ИЛИ, причем разрядные выходы регистра сдвига соединены с первыми входами соответствующих элементов И группы, вторые. входы которых соединены с первой гру ппой выходов блока управления, выходы группы элементов И через группу элементов ИЛИ соединены с второй группой входов блока сумматоров по модулю два, вторая группа выходов блока управления соединена с второй группой входов блока мажоритарных элементов.

Источники информации, принятые во внимание при экспертизе:

1. Патент США № 3222644, кл. 340 †-172.5, 1965.

2. Колесник В. Д., Мирончиков Е. Т. Декодирование циклических кодов, М., «Связь», 1968, с. 110 — 114..

Г>07349 г длогд ф

Редактор Т. 1Орчикова

Заказ 2624 44

ЦНИИПИ Государственного комитета Сонета Министров СССР по делан изобретений и открытий

I 13035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал Г1ПП «Патент», г. Ужгород, ул. Проектная, 4 (1

Je

Составитель В. Крылова

Техред О. Луговая Корректор Д. Мельниченко

Тираж 805 Подписное