Запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Реслублик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

<1658600 (61) ???????????????????????????? ?? ??????. ????????-????????” (22) ???????????????? 10.11.74 (21) 2073898>

Опубликовано 25.04.79. Бюллетень № 15

Дата опубликования описания 05.05.79 (51) М, Кл, G 11 С 11/40

Государственный комитет

СССР по делам изобретений и открытий (53) УДК 681.327..66 (088.8) В. А. Березкин, Е. Б. Володин,Ю.М. Полубояринов и В. В. Ракитин (72) Авторы изобретения

1 (2 (71) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЛСТВО

Изобретение относится к области вычислительной техники и может использоваться при построении интегральных запоминающих устройств для электронных вычислительных машин (ЭВМ) и устройств цифровой автоматики.

Известны полупроводниковые запоминающие устройства (ЗУ) динамического типа, построенные на элементах со взаимосвязанными и-р-и и р-п-р транзисторами (1). Основным недостатком этих устройств является разрушение информации при считывании. 1в

Наиболее близким техническим решением является запоминающее устройство, содержащее матричный накопитель, каждая ячейка которого содержит п-р-и и р-п-р транзисторы, база и-р-и транзистора соединена с

15 коллектором р-и-р транзистора, коллектор и-р-и транзистора соединен с базой р-п-р транзистора и разрядным формирователем и адресный формирователь (2).

Недостатком такого ЗУ является то, что считывание в нем происходит с разрешением 20 информации, а это приводит к удлинению цикла обращения, поскольку при каждом считывании из матрицы необходимо вновь записывать считанную информацию, а это, в свою очередь, усложняет схемы управления

ЗУ. Разрушение информации, хранимой в виде зарядов на барьерных емкостях р-п переходов элемента, обусловлено тем, что при считывании адресный формирователь подает импульс только на п-эмиттер прибора, а другой эмиттерный р-и переход остается закрытым. В результате ток считывания протекает только через п-р,п транзистор элемента и вызывает изменение заряда на его коллекторной емкости.

Целью изобретения является повышение быстродействия устройства за счет неразрушающего считывания информации.

Поставленная цель достигается тем, чтс разнополярные выходы адресного формирователя подключены к эмиттерам и-р-п и р-п-р транзисторов соответственно, а также тем, что адресный формирователь содержит многоэмиттерный транзистор, база которого подключена к первому резистору и базе первого транзистора, коллектор многоэмиттерного транзистора через диод подключен к базе второго транзистора, эмиттер которого подключен к шине нулевого потенциа658600 становлении информации, что сокращает цикл обращения и упрощает схемы управления.

Для записи новой информации одновременно с адресными импульсами подается импульс на разрядную шину. При положительной его полярности блокируется открывание транзистора 4, а значит и включение элемента, на коллекторной емкости транзис4$

3 ла и через второй резистор к эмиттеру первого транзистора, коллектор второго транзистора соединен с третьим резистором.

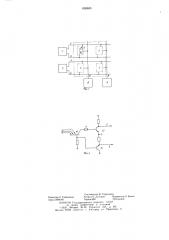

На фиг. 1 представлена схема запоминающего устройства; на фиг. 2 — конкретный вариант выполнения адресного формирователя.

Предлагаемое запоминающее устройство динамического типа включает в себя матрицу 1 накопителя, каждый элемент 2 которой состоит из взаимосвязанных и-р-п 3 и р-п-р 4 транзисторов, образующих четырехслойный 16 п-р-п-р прибор, который подключен и-эмиттером и р-эмиттером через адресные шины 5 и 6 к адресному формирователю 7, а и-базой через разрядную шину 8 к разрядному формирователю 9. Адресный формирователь

7 содержит многоэмиттерный транзистор 10, соединенный через дополнительный диод 11 с выходным транзистором 12, коллектор которого подсоединен к первой адресной шине 5. Вторая адресная шина 6 через выходной транзистор 13 подсоединена к базе мно- р гоэмиттерного транзистора 10.

В отсутствии обращения шины 5 и 8 находятся под одинаковым положительным потенциалом (2в), а шина 6 — под нулевым.

Информация в элементе хранится в виде зарядов на барьерных емкостях р-и переходов составляющего транзистора 4, причем состоянию 1 соответствуют разряженные емкости, а в состоянии О на емкостях присутствуют запирающие напряжения (порядка од- ga ного вольта). При считывании на адресные шины выбранного элемента подаются разнополярные импульсы так, что разность потенциалов между ними достаточна для включения элемента за счет эффекта du/dt (порядка 2В) . Если элемент находился в состоянии

1, то он включается, и в разрядной шине 8 протекает ток считывания 1, а после окончания считывания емкости остаются разряженными. Если элемент находился в состоянии О, то запирающие потенциалы на емкостях не позволяют ему включиться и после окончания считывания емкости остаются заряженными. Таким образом, состояние элемента при считывании не изменяется и после операции считывания нет необходимости в востора 3 накопится заряд, который сохранится после окончания импульсов, т. е. произойдет запись О.

При отрицательной полярности импульса на разрядной шине независимо от состояния элемента начнется инжекция неосновных носителей переходом р-эмиттер-п-база, что приведет к разряду емкостей транзистора

3, т. е. произойдет запись 1.

Использование адресного формирователя, выполненного парафазным, обеспечивает неразрушающее считывание информации в ЗУ динамического типа на ячейках со взаимосвязанными п — р — и и р — и — р транзисторами.

В результате этого повышается быстродействие устройства и упрощаются схемы управления, что расширяет область применения таких ЗУ и повышает степень интеграции при твердотельном исполнении.

Формула изобретения

1. Запоминающее устройство, содержащее матричный накопитель, каждая ячейка которого содержит и-р-и и р-п-р транзисторы, база и-р-и транзистора соединена с коллектором р-п-р транзистора, коллектор и-р-и транзистора соединен с базой р-и-р транзистора и разрядным формирователем и адресный формирователь, отличающееся тем, что, с целью повышения быстродействия устройства за счет неразрушающего считывания информации, разнополярные выходы адресного формирователя подключены к эмиттерам п-р-и и р-и-р транзисторов соответственно.

2. Запоминающее устройство по п. I отличающееся тем, что адресный формирователь содержит многоэмиттерный транзистор, база которого подключена к первому резистору и базе первого транзистора, коллектор многоэмиттерного транзистора через диод подключен к базе второго транзистора, эмиттер которого подключен к шине нулевого потенциала и через второй резистор к эмиттеру первого транзистора, коллектор второго транзистора соединен с третьим резистором.

Источники информации, принятые во внимание при экспертизе

1. Патент США № 3715732, кл. 340 — 173, 1973.

2. Патент Франции № 2.11Б 162 кл. G 11 С 11/00, 1972.

658600 юг. 1

Составитель В. Гордонова

Редактор Э. Губницкая Техред О. Луговая Корректор О. Билак

Заказ 2064/46 Тираж 680 Подписное

AH ИИ ПИ Государственного комитета СССР по делам изобретений и о-крыгий

I! 3035, Москва, Ж35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4