Регулятор источника реактивной мощности

Иллюстрации

Показать всеРеферат

Союз Советскик

Ощиалистическик

Республик (61) Дополиительиое к авт. саид-ву— (22) Заявлено 040377 (21) 2457643/27-07

1 с присоедииеиием заявки 89—

Н 02 Э 3/18

Государственный комнтет

СССР по делам нвобретеннй н отйрытнй (23) Приоритет ($$) Д)(621. 316,,921 (088.8) Опубликоваио 0506.79. Бюллетень Ио 21

Дата опубликоваиия описания 050679

- (72) Авторыизобретеиия

B,È.Êóýüêèí и Г.И.Сафарова (71) Заявитель (54 ) РЕГУЛЯТОР ИСТОЧНИКА РЕАКТИВНОЙ МОЩНОСТИ

Изобретение относится к области промышленной электроники и может быть использовано в тиристорных компенсатор ах р еакти вной мощности, кот орые обеспечивают поддержание на заранее заданном уровне коэффициента мощности в питающей сети.

Известны устройства регулирования коэффициента мощности, состоящие из фазочувствительного двухполупериодного выпрямителя, источника эталонного сигнала и компаратора, предназначенные для автоматического регулирования реактивной мощности. Однако эти устройства обладают низким быстродействием 11).

Наиболее близким по технической сущности является устройство регулирования коэффициента мощности генератора, состоящее из датчика фазы, формирователя Фазового рассогласования, задатчика фазового рассогласования, Формирователя заданного фазового рассогласования, блока подачи усиленного сигнала на автоматический регулятор напряжения (ApH) генератора.

Сигнал фазового рассогласования между током и напряжением, соответст-. вующий действительному коэффициенту мощности, вырабатывается Формировате- 30 лем фазового рассогласования, выполненным на полупроводниковых элементах; на его вхсщ поступают прямоугольные импульсы, соответствующие отрицательному полупериоду входных синусоидальных сигналов. После блока усиления сигнал Фазового рассогласования поступает на нагрузочиое сопротивление и емкость интегратора, одновременно на нагрузочное сопротивление поступает сигнал от задатчика Фазового рассогласовани я. Выходной импульс формирователя заданного фазового рассогласования поступает на выходной усилитель (2) .

Недостатком этого устройстВа является невозможность обеспечения заданного характера коэффициента мощности, потребляемой из питающей сети вне зависимости от коэффициента мощности нагрузки. Кроме того, устройство также обладает недостаточным быстродействием.

Целью изобретения является увеличение быстродействия регулятора и обеспечение задания коэффициента мощности, потребляемой из питающей сети.

Поставленная цель достигается тем, что в регулятор источника реактивной мощности, содержащий датчик фазы с бббб08 чувствительными элементами тока и напряжения, формирователь фазового рассогласования, включенный на выходе датчика фазы, эадатчик фазового рассогласования, формирователь заданного фазового рассогласования, интегратор и включенный на его выход 5 силовой регулирующий блок, дополнительно введен переключатель,а в датчик фазы введены две цепи, формирования синхроимпульсов, связанные соответственно с чувствительным элементом фазы тока и чувствительным элементом фазы напряжения и подключенные к двум соответствующим входам формирователя заданного фазового рассогласования непосредственно,а к 15 третьему " через переключатель и задатчик фазового рассогласования, причем к четвертому входу формирователя заданного фазового рассогласования подключен выход формироват ля фазового рассогласования, а выход формирователя заданного фазового рассогласования подключен к входу интегратора.

Кроме того, в регуляторе источника реактивной мощности формирова- 25 таль заданного фазового рассогласования содержит четыре схемы совпадения, два триггера и нять инверторов, причем один иэ входов триггеров через первую и вторую схему совпаде- 30 ния соответственно подключен к выходай датчика фазы, вторые входы первой и второй схем совпадения, второй вход первого триггера и вход первого инвертора соединены с выходом форми- 35 рователя фазового рассогласования,выход первого инвертора через первый вход третьей схемы совпадения соединен с вторым входом второго триггера, выход первого триггера через второй 4р инвертор, четвертую схему совпадения и третий инвертор соединен с входом интегратора, выход второго триггера через четвертый и пятый инверторы подключен к входу интегратора, а вторые входы третьей и четвертой схем совпадения соединены с выходом задатчика фазового рассогласования.

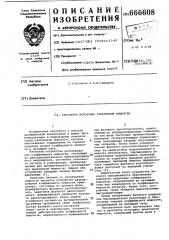

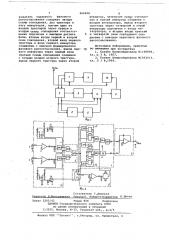

На фиг.l представлена блок-схема устройства1 на фиг.2 - один из возможных вариантов принципиальной схемы устройства.

Регулятор содержит трансформаторы тока и напряжения 1, связанные с питающей сетью, к которым подсоединен датчик фазы 2. Выход датчика 2 подклю55 чен к формирователю Фазового рассогласования 3, соединенному с одним иэ входов формирователя заданного фазового рассогласования 4. Два других входа последнего соединены с датчи- 6р ком фазы 2, а четвертый посредством переключателя 5, имеющего два положения 6 и 7, с эадатчиком фазового рассогласования 8. К выходу формирователя заданного фазового рассогла- 65 сования 4 подключен интегратор 9, выход которого подсоединен к силовому регулирующему блоку 10. Силовая часть блока 10 подключена к сети, от которой питается нагрузка 11.. Датчик Фазы 2 для повышения точности выполнен на двух операционных уси- лителях, соединенных с цепями формирования синхроимпульсов, состоящими из дифференцирующих цепочек, подключенных к базам соответствующих транзисторов 12,13, и инверторами 14, 15, выходы которых подключены к формирователю фазового рассогласования, 3, состоящему из схем совпадения 16, l7 и схемы совпадения 18, обеспечиваю их логическую функцию сигнала рассогласования, Выход формирователя истинного фазового рассогласования

3 подсоединен к формирователю заданного фазового рассогласования 4.

Последний содержит две параллельные ветви, каждая иэ которых включается в работу в зависимости от положения вектора, тока относительно вектора напряжения. Каждая ветвь состоит из схем запуска триггеров, выполненных на элементах 19 и 20 соответственно, входы которых подсоединены к цепям формирования аинхроимпуль сов и выходу формиров.ателя фаэового рассогласования 3, а выходы— к триггерам 21, 22.

В случае, когда вектор тока отстает от вектора напряжения, работает ветвь, содержащая триггер

2l, выход которого через инвертор

23 подсоединен к схеме совпадения

24, выполненной на элементе ИЛИ-НЕ, один из входов которой соединен с выходом эадатчика фазового рассогла,сования 8, а выход данного сумматора через инвертор 25 подключен ко входу интегратора 9.

В случае, когда вектор тока опережает вектор напряжения работает ветвь, содержащая триггер 22, вход которого подсоединен к выходу схемы совпадения 26. На другой вход схемы совпадения 26 через инвертор 27 поступает сигнал с выхода Формирователя Фазового согласования 3, соответствующий истинному Фазовому рассогласованию. Выход триггера 22 через инвертор 28 соединен с инвертором 29, на выходе которого формируется импульс отрицательной полярности, соответствующий величине заданного фазового рассогласования.

Импульс с выхода последнего поступает на вход интегратора 9, который соединен с силовым регулирующим устройством 1 О.

Схема регулятора источника реактив ° ной мощности работает следующим образом (рассматривается режим стабилизации индуктивного характера нагрузки - переключатель 5 в положении 6) . Ha входы датчика Фазы 2 от трансформаторов тока и напряже6666

60 ния 1 поступают . синусоидальные сигналы напряжения 0„„„ и тока 5„,„,1, Преобразуемые операционными усилителями в прямоугольные импульсы, соответствующие входным синусоидальным сигналам по частоте и фазе, через элементы 14 и 15, осуществляющие их инвертирование, сигналы поступают на вход формирователя фазового рассогласования 3, где происходит выделение сигнала фазового рассогласования между током и напряжением 10 дважды за период. Схемы совпадения, 16 и 17 формируют импульсы, длительность которых соответствует величине фазового рассогласования при переходе входного тока и напряжения 15 через нуль из положительного значения в отрицательное и наоборот. При этом осуществляется следующая логическая операция:

N =02; N =U3 где

N — сигнал фазового рассогласования;

5 — вектор тока;

Π— вектор напряжения. 25

Полученные сигналы суммируются схемой совпадения 18, которая осуществляет выделение сигнала рассогласования дважды за период. Данный сигнал, длительность которого соот- щ ветствует истинному фазовому рассогласованию, поступает. на вход формирователя заданного фазового рассогласования 4.

При совпадении на элементе 19

35 передних фронтов, поступающих на его вход синхроимпульсов, соответствующих моментам перехода через ноль тока и напряжения, и импульсов, соответствующих истинному фазовому рассогласованию, Hà его выходе формируется импульс запуска триггера 21, С выхода триггера 21 сигнал истинного фазового рассогласования через инвертор 23 поступает на один из входов схемы совпадения 24. На второй ее вход поступает импульс с выхода задатчика величины фазового рассогласо вания 8, сформированный в момент прихода синхроимпульсов датчика 50 фазы 2. Выделенный сигнал заданного фазового рассогласования с выхода схемы совпадения 24 через инвертор 25 поступает на вход интегратора 9.Полученное на его выходе напряжение, пропорциональное по величине и знаку заданному фазовому рассогласованию, поступает на силовой регулирующий блок 10, изменяя угол управления его таким образом, чтобы обеспечивать заданное положение вектора тока относительно вектора напряжения. В случае изменения характера нагрузки с индуктивного на емкостный в схеме происходят аналогичные процессы, 08 . 6 но совпадение соответствующих передних фронтов импульсов происходит на схеме з any ñêà 20, з ат ем работает триггер 22, суммирование происходит на элементе 26 и через инвертор 28, импульс длитель-. ность которого соответствует величине заданного фазового рассогласования, поступает на инвертор

29, на выходе которого формируется импульс отрицательной полярности, поступающий на вход интегратора 9 ° Выходное напряжение поступает на силовой регулирующий блок 10, изменяя его угол так, чтобы вектор тока отставал от вектора напряжения, то есть компенсируя емкостную реакцию нагрузки на сеть до индуктивной.

В случае необходимости обеспечения опережения вектором тока вектора. напряжения (реакция емкостного характера) переключатель 5 ставится в положение 7; схема при этом работает аналогичным образом.

Устройство использовано в системе управления и автоматического регулирования статического фильтрокомпенсирующего устройства в качестве регулятора коэффициента мощности, что дало возможность обеспечивать необходимую стабилизацию коэффициента мощности от 0,5 до 0,95 с точностью до 0,5 электрических градусов.

Формула изобретения

1. Регулятор источника реактивной мощности, содержащий датчик фазы с чувствительными элементами тока и напряжения, формирователь фазового рассогласования, включенный на выходе датчика фазы, задачик фазового рассогласования, формирователь . заданного фазового рассогласования, интегратор и включенный на его выход силовой регулирующий блок, о т л и— ч а ю шийся тем, что, с целью увеличения быстродействия и обеспечения задания коэффициента мощности, потребляемой из питающей сети, в него дополнительно введен переключатель, а в датчик фазы введены две цепи формирования синхроимпульсов, связанные соответственно с чувствительным элементом фазы тока и чувствительньм элементом фазы напряжения и подключенные к двум соответствующим. входам формирователя заданного фазового рассогласования непосредственно, а к третьему — через переключатель и задатчик фазового рассогласования, причем к четвертому входу формирователя заданного фазового рассогласования подключен выход формирователя фазового рассогласования, а выход формирователя заданного фазового рассогласования подключен к входу интегратора.

2. Регулятор источника реактивной мощности по п.1, о т л и ч а ю шийся тем,. что,форжСель

Фиг.1

Составитель Г.Дамская

Редакто .Меп ишвили Тех е Н. Баб рка Ко екто

Заказ 3203/42 Тираж 856 Подписное ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП Патент, г.ужгород, ул. Проектная-, 4 роват ель заданного фазового рассогласования содержит четыре схемы совпадения, два триггера и пять инверторов, причем один из. входов триггеров через первую и вторую схему совпадения соответственно подключен к выходам датчика фазы, вторые входы первой и второй схем совпадения, второй вход первого триггера и вход первого инвертора соединены с выходом формирователя фазового рассогласования, выход первого инвертора через первый вход третьей схемы совпадения соединен с вторым входом второго триггера, выход первого триггера через второй

66608 8 инв ертор, четв ертую схему с ов падения и третий инвертор соединен с входом интегратора, выход второго триггера через четвертый и пятый инверторы подключен к входу ин-. тегратора, а вторые входы третьей

5 и четвертой схем совпадения соединены с выходом задатчика Фазового рассогласования.

Источники информации, принятые во внимание при экспертизе

1. Патент Великобритании 91168899, кл, G 3 R, 1967.

2. Патент Великобритании 91062614 кл. G 3 R,1964.