Ячейка однородной вычислительной среды

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

И ЗОБРЕТЕ Н,ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1 " 691846

Сотов Советских

Сощналмстнческих

Респубиин (61) Дополнительное к авт. свид-ву (51)M. 1(л.

G 06 F 7/00 (22) Заявлено 03,0б.77 (21) 2492567/18-24 с присоединением заявки И

Государственный комитет

СССР во делам изобретений н открытий (23) Приоритет—

Опубликовано 15.10.79, Вюллетень РЙ 38 (53) Д (681.327 (088.8) Дата опубликования описания 15.10.79 — 1

М. П. Бо ачев, В. П. Волчков, В. И. Гевр ркян,.Ю,,Н.СулищИ1т;

И. С. Потемкин,,Н. К.Иванова, 10. В, Осокий; В: В;"дьбйковскРй, Г. Ф. Страутманис, Л. А. Вольперт, В. h .-.fóëó3écùé,-.А,. И, Талднцев и И. А. Михайлов,;„-,...,...,," 1

::.Ъ" (72) Авторы изобретения (71) Заявитель (54) ЯЧЕЙКА ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙ СРЩЫ

Изобретение относится к области вычисли. тельной техники и предназначено для использо вания в качестве ячейки однородных вычислительных сред (ОВС).

Известна ячейка однородной вычислительной среды с переменной структурой настройки, со держащая схемы И, выбора направлений передачи возбуждения, регистра сдвига; устройство хранения информации, логический элемент, схемы совпадения и схемы "Логическая равнозначность", входы которых подключены соответственно к части входов и выходов устройства хранения информации, выходы схем "Логическая равнозначность" подключены ко входам схемы совпадения, подсоединенной своим выходом ко входу триггера активности, выход которого подключен к управляющему входу ло,гического элемента, управляющий вход схемы совпадения подключен к источнику управляющих сигналов 11).

Недостатком такой ячейки является небольшой набор реализованных функций, что приводит к значительным затратам оборудования,,необходимого для настройки ОВС на решение

f задач, Наиболее близким техническим решением к данному изобретению является ячейка одно; родной вычислительной среды, содержащая .

5 арифметико-логический элемент, регистр команд, дешифратор, входы которого подключены к первой группе выходов регистра команд, элемент задержки, два коммутатора входов и

10 четыре коммутатора выходов, причем настроечные входы регистра команд соединены с настроечными входами ячейки, настроечный вход регистра команд соединен с настроечным выходом ячейки, первый управляющий выход

15 регистра команд соединен с первым входом первого элемента задержки, второй вход кото рого подключен к выходу арифметико-логического элемента, управляющий вход которого соединен с выходом дешифратора, а первый и второй информационный входы, подключены к вйходам первого и второго коммутаторов входов, соецинешых своими входами с четырьмя информационными входами ячейки, управляю-, щие входы коммутаторов входов соединены

69184 со вторым управляющим выходом регистра ко: манд, выход первого элемента задержки соединен с первыми входами коммутаторов выходов, выходы которых подключены к выходам ячейки t21. Кроме того, ячейка содержит блок координатной выборки ячейки, входы которого подключены к горизонтальной и вертикальнЪй координатным шинам выборки ячейки.

Недостатками этой ячейки являются сложность из-за значительного набора функций, малая надежность, обусловленная сложностью схемы, и Малая производительность.

Целью изобретения .является повышение быстродействия ячейки ОВС.

Это достигается тем, что в предлагаемую ячейку введены третий коммутатор входа, два элемента задержки, причем входы третьего коммутатора входа соединены с информационными входами ячейки, выход третьего коммутатора входа соединен с входом второго элемента задержки, управляющий вход которого подключен к третьему управляющему выходу регистра команд, а выход соединен со вторыми входами коммутаторов выходов и с входом третьего элемента задержки, выход которого соединен с третьими входами коммутаторов выходов, управляющие входы которых соединены со вторыми и четвертыми управляющими выходами регистра команд, входы адресов управления вторым элементом задержки которого соединены с выходами адресов хранения констант.

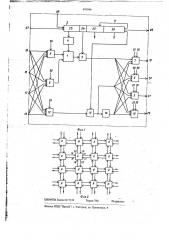

На фиг. 1 представлена предлагаемая ячейка ОВС; на фиг. 2 — фрагмент вычислительной среды с ячейкой, где показаны арифметико-логический элемент 1, элемент задержки

2, регистр команд 3, дешифратор 4, два коммутатора входов 5, 6, четыре коммутатора выходов 7 — 10, цепь закольцовки 11 части ре-

4О гистра команд 3, цепь транзита, включающая третий коммутатор входа 12, два элемента задержки 13, 14Э информационные входы ячейки 15 — 18, выходы ячейки 19 — 22, первая rpynпа выходов регистра команд 23, первый управляющии выход регистра команд 24, управ45 ляющие выходы регистра команд 25 и 26, настроечные входы ячейки 27, 28, настроечный выход ячейки 29.

Устройство работает следующим образом.

Перед началом решения задачи производится запись команды в регистр команд 3, Код команды вводится через настроечный вход ячейки 27 последовательно разряд за разрядом в регистр команд 3 по сигналу разрешения ввода программы, подаваемому на на55 строечный вход 28.

Настроечный выход ячейки 29. обеспечивает возможность последовательного соединения

6 4 регистров команд 3 в ОВС. По окончании си нала, разрешающего ввод программы, код команды запоминается в регистре команд 3, в результате чего с этого момента времени ячей ка переходит в режим выполнения операций.

Дешифратор 4 (схемы И), вход которого соединен с регистром команд 3, а выход — с арифметико-логическим элементом 1, настраивает его на выполнение операции согласно коду операций в первой группе выходов регистра команд 23.

При наличии логической "Г на первом управляющем выходе регистра команд включается элемент задержки 2.

При наличии логического "0" информация с выхода арифметико-логического элемента 1, минуя элемент задержки 2, поступает через коммутаторы выходов 7, 8, 9, 10 на выходы ячейки 19, 20, 21, 22.

Через управляющие выходы регистра команд 25, 26 осуществляется набор направлений приема и выдачи информации ячейкой по операционной цепи (арифметико-логический элемент 1, элемент задержки 2) и цепи транзита, обеспечивая таким образом их независимое один от другого управление и работу.

Цепь транзита, работая автономно от операционной сети, осуществляет передачу информации через элементы задержки 13, 14, с входов ячейки 15, 16, 17, 18 на ее выходы 19, 20, 21, 22.

Таким образом, в этом режиме работы ячейка может выполнять функции с задержкой выдачи информации или без задержки ее и независимо передавать информацию с задержкой на один разряд или на два разряда в цепи -транзистора.

При выполнении ячейкой ОВС операции "генератор констант" сигнал с дешифратора 4 включает цепь закольцовки 11 (схема И вЂ” ИЛИ) и отключает операционную цепь ячейки ОВС и коммутаторы входов 5, 6, 12. Константа с выхода команд 3 по цепи закольцовки 11 циркулирует в разрядах регистра команд 3 и одновременно, последовательно через равные интервалы времени, определяемые длиной слова константы, поступает через элемент задержкй.13 и цепь транзита на выходы ячейки 19, 20, 21, 22.

Для определения эффективности предлагаемой ячейки ОВС были изготовлены контрольные программы последовательного умножения восьмиразрядных слов.

Для предлагаемого варианта ячейки программа умножения занимает 32 ячейки среды (прямоугольник 8 х 4).

Для варианта ячейки — прототипа программа умножения занимает 64 ячейки среды (пря691846

15 моугольник 16 х 4), т.е. количество ячеек расходуется в два раза больше.

Предлагаемый вариант ячейки позволяет .повысить производительность в четыре раза за счет одновременного выполнения четырех независимых операций (транзита, логического сло. жения, сдвига на один разряд наряду с опера циями, выполняемыми арифметико-логическим элементом), а следовательно, существенно повысить эффективность использования среды за счет сокращения числа ячеек, используемых для решения задач.

Формула изобретения

Ячейка однородной вычислительной среды, содержащая арифметико-логический элемент, регистр команд, дешифратор, входы которого подключены к первой группе выходов регистра. команд, элемент задержки, два коммутатора входов и четыре коммутатора выходов, при чем настроечные входы регистра команд соединены с настроечными входами ячейки, настроечный выход регистра команд соединен с на25 строечным выходом ячейки, первый управляющий выход регистра команд соединен с первым входом первого элемента задержки, второй вход которого подключен к выходу арифметико-логического элемента, управляющий вход которого

30 соединен с выходом дешифратора, а первый и второй информационные входы подключены к выходам первого и второго коммутаторов !

6 входов, соединенных своими входами с четырьмя информационными входами ячейки, управляющие входы коммутаторов входов соединены со вторым управляющим выходом регистра команд, выход первого элемента задержки соединен с первыми входами коммутаторов выходов, выходы которых подключены к выходамячейки, отличающаяся тем, что; с целью повышения быстродействия ячейки, в нее введены третий коммутатор входа, 1 два элемента задержки, причем входы третьего коммутатора входа соединены с информа ционными входами ячейки, выход третьего коммутатора входа соединен с входом второго элемента задержки, управляющий вход которого подключен к третьему управляющему вы- ходу регистра команд, .а выход соединен со вторыми входами коммутаторов выхода и с входом третьего элемента задержки, выход которого соединен с третьими входами коммутаторов выходов, управляющие входы которых соединены со вторым и четвертым управляющими выходами регистра команд, входы адресов управления. вторым элементом задержки которого соединены с выходами адресов хранения констант.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетелЬство СССР N 314203, кл. G 06 F 7/00, 1973.

2. Автоматика и вычислительная техника, No 3, 1975, с. 10-17.