Устройство для возведения в квадрат п-разрядных двоичных чисел

Иллюстрации

Показать всеРеферат

Союз Советскик

Социалистических

Республик (ii;699521

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6 l ) Дополнительное к авт. свид-ву (5))M. Кл.

G 06 F 7/38 (22) Заявлено 30.03.78 (21) 2596629/18-24 с присоединением заявки ЖГасударственный вафатет

СССР па делан нзабретеней и атнрытнй (23)Приоритет(53) УДК 681.325 (088.8) Опубликовано 25.11.79 Бюллетень F43

Дата опубликования описания 28.11.79

Я. М. Вайнштейн, В. И. Волошин, В. Ф. Евдокимов, И. Ф. Зубенко, В. В. Месяц и Ю. А. Плющ (72) Авторы изобретения

Институт электродинамики AH Украинской ССР (7!) Заявитель (54) УСТРОЙСТВО ДЛЯ ВОЗВЕДЕНИЯ В КВАДРАТ Д -РАЗРЯДНЫХ ДВОИЧНЫХ ЧИСЕЛ

Изобретение относится к цифровой вычислительной технике, предназначено для возведения в квадрат Я -разрядных двоичных чисел и может быть использовано в информационно-измерительных системах в качестве решающего блока

5 ! для оперативной обработки информации.

Известны устройства, позволяющие получать на их выходах значение кода, равное квадрату входной величины, пред.10 ставляющих собой совокупность логичес ких схем, количество и связи между которыми определяют аппаратурные затраты и быстродействие всей схемы в целом fl) .

Из известных устройств наиболее близким к изобретению по своей технической сущности является устройство для возведения в квадрат т - разрядных двоичных чисел, содержащее одноразрядные сумматоры, последовательно соединенные межразрядными связями переноса, входы которых соединены с выходами элементов И, а выходы - с ) -ыми,(g > 1

2 и-2) выходами устройства, (27 -1)-ый и 2 тт-ый выходы устройства подключены соответственно к шине информационного нуля и к g-ому входу устройства (21.

Недостатком данного устройства являются большие аппаратурные затраты.

Е1ель изобретения — упрощение устрой ства.

Это достигается тем, что в устройстве для возведения в квадрат т -разрядных двоичных чисел, содержащем одноразряд ные сумматоры, последовательно соединенные межразрядными связями переноса, входы которых соединены с выходами элементов И, а выходы - c 1-ыми (1 =1... 2 tl-2) выходами устройства, (2 tt-1)-ый и 2тт-ый выходы устройства подключены соответственно к шине информационного нуля и к тъому входу устройства, т-ый вход (j l... тт- 1) устройcTBG соединен непосредственно с входом одноразрядного сумматора, выход суммы которого соединен с j =21 выходом устройства, g-ый вход устройства (с=2,3...

3 6, 39 ... yi} соединен с первыми входами (0-) )-ого элементов И, вторые вхоцы которых подключены к g -ому { к=1,2... Я -1 ) входу устройства.

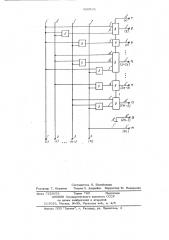

На чертеже представлена функциональ—

HEIR схема прецл»гаемого устройства цля случая возведения в квадрат четырехразрядных чисел (tl =4) .

Устройство содержит входы 1-4, элементы И 5, одноразрядные сумматоры 6, выходы 7-14.

Устройство работает следующим образом.

На вход 1. поступает значение старшего разряда возводимого в квадрат числа, а значение старшего разряда результата снимается с выхода 7. На вход 4 поступает значен ие младше го разряда возводимого в квадрат числа, а значение младшего разряда результата снимается с вы20 хода 14,, Например, при поступлении на входы 1-4 устройства четырехразрядного кода Х=10 11 на выходы 7-14 по, окончанию перехоцных процессов в схеме

25 установится значение Korts У-"01111001, соответствующее квадрату исходного значения входного кода Х (состояния элементов схемы (CM. на чертеже).

Количество элементов И при четырехЗо разрядном представлении информации равно шести. При реализации известного устройства потребовалось бы девять элемен- тов И-НЕ и шесть элементов HE.

При tl -разрядном представлении инфор35 мации для реализации схемы известного: устройства необходимо л2+- д ь Х элементов И-HE и 2е -2 элементов HE. Предложенная сХема устройства реализуется

2 с использованием элементов И.

521

Г»КИМ Ot>Pi OIOM, - IICIIOJILOOIIIIПИЕ IIPertlIO» жеппой сх мы устройства позволяет cv щоственио уменьшить инпар»турные затр»ты, что, в свою очередь, позволяет повысить нацежность работы и уменьшить 10 требляемую мощность устройства в целом, Формула изобретения

Устройство для возведения в квадрат

tl-разрядных двоичных чисел, содержащее одноразрядные сумматоры, последовательно соединенные межразряцными связями переноса, входы которых соединены с выходами элементов И, а выходыс -ми (j l... 2 -2) выходами устройстваа, (2 И -1 ) -ый и 2 и -ый выходы устройства подключены соответственно к шине информационного нуля и к ) -юму входу устройства, о т л и ч а ю щ е е— с я тем, что, с целью упрощения, 1-ый вход .(1 =1... и-1) устройства соединен непосредственно с входом одноразрядного сумматора, выход суммы которого соединен с j =-..2(, выходом устройства, -ый вход устройства (3 =2,3... tl) соединен с первыми входами (-1)-ого элементов И, вторые входы которых подключены к g-oMy (к=1,2... -1) входу устройства.

Источники информаций, принятые во внимание при экспертизе

1. Прангишвили И, В. и др. Микроэлектроника и однородные структуры для построения логических и вычислительных устройств.. М., "Наука", 1967, с. 180.

2. Авторское свидетельство СССР по заявке Ко 2475297/24 от 31.10.77 (прототип) .

Составитель Н. Шелобанова

Редактор Т. Клюкина ТехредО. Андрейко Корректор Ю. Макаренко

Заказ 7229/53 Тираж 780 Подписное

LIHHHHH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-З5, Раушская наб., д. 4/5

Филиал ППП "Патент, r. Ужгород, ул. Проектная, 4.