Устройство для решения систем алгебраических уравнений

Иллюстрации

Показать всеРеферат

О П И C А Н И Е (»)7144{)5

ИЗОБРЕТЕНИЯ

Союз Советсник

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву

{22) Заявлено 07.06.77 (21) 2492857/18 24 с присоединением заявки,% (23) Приоритет — (51) М. Кл.

G 06 F 15/32

65еуйерстееннЫ камнтет

СССР ав ленам нзебретеннй н етнрытнй (5З) ЛK 681.325 (088.8) Опубликовано 05,02.80. Бюллетень J% 5

Дата опубликования описания 15.02,80

Г. Е. Пухов, В. Ф. Евдокимов, Ю, А. Плющ, И. Ф. Зубенко, Н. П. Тимошенко и А. П. Стеканов (72) Авторы изобретения

Институт электродинамики АН Украинской CCP и Опытно-конструкторское технологи 5еское бюро института металлофиэики АН Украиксксй ССР (7 I ) Заявители

P (54) УСТРОЙСТВО ДЛЯ РЕШЕНИЯ СИСТЕМ

АЛГЕБРАИЧЕ5 КИХ УРАВНЕНИЙ

Изобретение относится к области вычисли)тельной техники и может быть .применено в системах автоматического регулирования, управляющее воздействие в которых определяется путем решения систем линейных алгебраических уравнений.

Известно устройство для решения алгебраических уравнений (1), содержащее блоки ввода и вывода, управляющие входы которых подключены к выходу блока управления, комбинационные цифровые сумматоры по числу, 50 неизвестных, первые входы которых соединены с выходами блока ввода, матрицу комбинационных множительных блоков по числу коэффициентов уравнений, первые входы которых нод15 ключены к соответствующим выходам блока ввода, выходы комбинационных множИтельных блоков каждой строки матрицы подключены к второму входу соответствующего комбинационного цифрового сумматора, блок генераторов случайных сигналов, блок ограничителей уровня сигналов и блок вентилей.

Наиболее близким техническим решением к изобретению является устройство для решения ) 2 систем алгебраических уравнений, содержащее блок многоразрядных сумматоров и матрицу умкожеккя, выход которого подключен к одному входу блока многоразрядных сумь5аторов (2J.

Недостатком известного устройства является невысокая точность и узкий класс решаемых задач из-эа возникновения генерации в устройстве вследствии зациклива51ия решения, вызванное несоответствием кодов входа и выхода рассматриваемого устройства в разомкнутом состоянии, что не позволяет находить решение поставленной задачи как некоторое установившееся состояние в устройстве при замыкании обратной связи.

Рассмотрим простейший пример, подтверждающий то, что схема известного устройства не установится в устойчивое состояние, соответствующее решению поставленной задачи, при замыкании обратной связи.

Рассматривать будем на примере решения ка известком устройстве уравнения первого порядка при представлении информации пятью разрядами в симметричной троичной системе счис3 знаком 1 — - обозначено

714405 пения (I, О, 1), где значение "- 1".

Задано уравнение первого порядка, представленное в виде, удобном для решения его на известном устройстве: х =Ьх+ 1, (4 ) где Х вЂ” искомое неизвестное, b — постоянный коэффициент, f — постоянйая величина, соответствующая правой части заданного уравнения.

В соответствии с заданным уравнением (1) матрица умножения осуществляет умножение искомого неизвестного Х на постоянный коэф,фициент Ь, выход матрицы умножения соединен с входом многоразрядного сумматора, на второй вход которого подается значение правой части т, а выход многоразрядного сумматора соединен с входом матрицы умножения, образуя при этом обратную связь в устройстве и по истечении времени переходного процесса в устройстве на выходах многоразрядного сумматора должно установиться значение кода, соответствующее решению заданного уравнения (1).

Рассмотрим поведение устройства при разомкнутой обратной связи, в точке, близкой к значению решенйя исходного уравнения (1). при следующих значениях коэффициента b и правой части f:

Ь = 0,01010) f = 0,11111.

При этом будем обозначать: х, — Значение кода на выходах многоразрядного сумматора, осуществляющего суммирование значений Ьх и f, x> — значение кода, поступающего на вход матрицы умножения, осуществляющего умноженйе на постоянный коэффициент b.

Пусть х = 0,11001, тогда х = bx + f = O,01010 0,11001+ О,ШII =

= 0,110TI, Подадим полученное на выходах многоразрядного сумматора значение кода 0,11011 на вход матрицы умножения и определим новое значение кода на выходах многоразрядного сумматора:

xi = bx„+ f = 0,01010 0,11011 + 0,11111

= 0,11001.

Таким образом, получим, что значение кода 45

0,11001, поданное на вход матрицы умножения, вызывает йа выходах многоразрядного сумматора значение кода 0,11011, которое, в свою очередь, будучи поданным на вход матрицы умножения вызовет на выходах многоразрядно- о го сумматора первоначальное значение кода

0,11001. Отсюда следует, что в известном устройстве устанавливается несоответствие кодов входа и выхода схемы при разомкнутой обратной связи и при замыкании обратной связи решение зацикливается и схема генерирует, что не позволяет найти установившееся значение кода соответствующее регпению заданного уравнения при рассмотренных исходных данных.

Принципиально в такого рода схемах зацикливание решения может вызываться и более длинной цепочкой несоответствия кодов, когда вектор неизвестных х, (при решении систем алгебраических уравнений) вызывает на выходах многоразрядных сумматоров значение вектора х и т. д., хц вызывает на сумматоров вектор x„, а х„ в свою очередь, вызывает вектор х1 и йроцесс повторяется, Цель изобретения — повышение точности— достигается тем, что в известное устройство для решения систем алгебраических уравнений дополнительно введены (n-1) канал, каждый из которых содержит блок многоразрядных сумматоров и матрицу умножения, выход которой подключен к одному входу блока многоразрядных сумматоров, другой вход блока многоразрядных сумматоров всех каналов является входом устройства, выход блока многоразрядных сумматоров предыдущего канала подключен ко входу матрицы умножения последующего канала, выход блока многоразрядных сумматоров последнего канала соединен со входом матрицы умножения первого канала, выходы блоков многоразрядных сумматоров всех каналов являются выходами устройства.

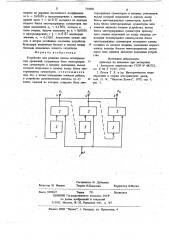

На чертеже. представлена блок-схема устройства для решения систем алгебраических уравнений.

Устройство содержит вход 1 устройства, блок.

2 многоразрядных сумматоров, матрицу 3 умножения, выходы 4 устройства.

Работу устройства проиллюстрируем на примере, рассмотренном выйе.

В соответствии с исходными данными рассматриваемого примера матрицы 3 умножения состоят из; одного комбинационного умножителя, осуществляющего умножение машинной переменной х; на постоянный коэффициент Ь =

= 0,01010 и длина цепочки несоответствия кодов равна 2, т. е. n = 2. В этом, случае схема устройства будет содержать два блока многоразрядных сумматоров и две матрицы умножения, каждая из которых состоит из одного комбийационного умножителя.

При заданных исходных данных устройство может находиться в одном из двух устойчивых состояний:

x = 0,11001; х2 = 0,11011, или

x,= 0,1 IOTI; х = 0,11001 компоненты каждого из которых являются при приближенными значениями искомой переменной для рассмотренных ранее значений коэффициентов Ь и правой части f.

Действительно, значение переменной х, = O,l l00l, поступающее с выходом первого блока многоразрядных сумматоров, будучи умУ

714405 . 6 горазрядных сумматоров и матрицу умножения, выход которой подключен к. одному входу блока многоразрядных сумматоров, другой вход блока многоразрядных сумматоров всех каналов является входом устройства, выход блока многоразрядных сумматоров предыдущего канала подключен ко входу матрицы умножения последующего канала, выход блока многоразрядных сумматоров последнего канала соединен со входом матрицы умножения первого канала, выходы блоков многоразрядных сумматоров всех каналов являются выходами устройства. хл

Составитель И. Дубинина

Техред Н.Ковалева Корректор И.Муска

Редактор М. Минаев

Заказ 9290/47 . Тираж 751 Подписное

ЦНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 ножено на значение постоянного коэффициен та b = 0,01010 и просуммировано с значением правой части f = 0,11111 вызывает на выходах второго блока многоразрядных сумматоров зна-. чение переменной х, = 0,11011, которое a свою очередь, будучи умножено íà b = 0р01010 и просуммировано с f = 0,11111 подтвердит значение x> =- 0,11001. Аналогично можно описать и второе устойчивое состояние устройства. Благодаря введенным блокам и связям между 10 блоками повысилась точность устройства.

Формула изобретения

Устройство для решения систем алгебраических уравнений, содержащее блок многоразрядных сумматоров и матрицу умножения, выход которой подключен к одному входу блока многоразрядных сумматоров, о т л и ч а ю щ е е с я тем, что, с целью повышения точности работы, в устройство дополнительно введены (n — 1) 20 канал, каждый из которых содержит блок мноИсточники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР N 482752, кл. 6 06 F 15/32, 1974.

2. Пухов Г. Е. и др. Математическое моде- лирование и теория электрических цепей, вып. 11. К., "Наукова Думка", 1973, стр. 3, рис. 5.