Интегратор

Иллюстрации

Показать всеРеферат

у " с)дщ

".и .," 1 р у „,",1

„„728135

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

Союз Советских

Социалистических

Республик

4

// - — - г (б1) Дополнительное к авт. свид-ву (22) Заявлено 021078 (21) 2668797/18-24 (51) м. кл. с присоединением заявки №

6 06 С 7/18

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет

Опубликовано 150480. Бюллетень ¹ 14 (53) УДК 681 ° 335 (088. 8) Дата опубликования описания 150480

Е.И.Дорохов, В.В.Шеваль, С.А,Исаков, Н.A,Èâàíoâ, Н.В.Зайцев и E.Ï.Ìèðoíoâ (72) Авторы изобретен и я (71) Заявитель (54) инткгмтор

Изобретение отн .:сится к области автоматического управления и вычислительной техники и может найти применение в различных информацион-, ных системах.

Известен интегратор, содержащий интегрирующие блоки, сумматор, блок управления, пороговое устройство, ключи, управляющие входы которых подключены к выходу блока упрАвления, интегрирующий усилитель, в цепь обратной связи которого по- следовательно с конденсатором включен ключ, дифференциальный усилитель, выход которого через ключ 15 соединен с входом первого интегрирующего блока, выходом подключенного к одному входу сумматора, другой вход которого подключен к пороговому устройству, высодом соединенному 20 с входом блока управления, при этом выходы блока управлейия подключены к входу интегрирующего усилителя и к управляющему входу второго интегрирующего блока, другой вход которого соединен с источником входного сигнала (1).

Известный интегратор сложен и имеет недостаточную точность интегрирования, 30

Известен интегратор, содержащий интегрирующие усилители, первые входы которых соединены с источником входного сигнала, а выходы через переключатель, управляющий вход которого соединен с выходом датчика временных интервалов, подключены к выходу интегратора, ключи, управляющие входы которых подключены к датчику временных интервалов, и блок сравнения, входы которого подключены к выходам ин— тегрирующих усилителей, а выходы через ключи - к вторым входам интегрирующих усилителей (2).Этот интегратор имеет недостаточную точность интегрирования.

Наиболее близким по техническои сущности к предложенному является интегрирующее устройство, содержащее интегратор с обнулением, подключенный к первому входу сумматора, запоминающий блок и генератор тактовых импульсов, причем выход сумматора подключен к входу запоминающего блока, выход которого соединен с вторым входом сумматора, а управляющий вход запоминающего блока соединен с генератором тактовых импульсов, соединенным через

728135 4

/ и р Ув,„((n-1) . Т), а зто конечная сумма входного воздействия. При достаточно малых Т и t ."Еивх (" UT7 = Г u,„(íd-I С

5 где С вЂ” постоянная интегрирования.

Нетрудно видеть, что для,„<)=АМпи1 и

1 О (. T) . через время

1 !

О -т .)(,где К 0,1,2,3,..., равен

2> нулю, следовательно, С зависит только от момента синхронизации. тактовых импульсов f с входным сигналом

U „ (t) . Поэтому, если синхронизировать тактовый импульс с экстремальным значением U i(t) то С тождественно равно нулю. Кроме того, данный интегратор принципиально

20 возможно выполнить без применения

УПТ, что также повышает точность интегрирования.

Лабораторные испытания показали высокую точность интегрирования (0,004%) и практически полное отсут25 ствие дрейфа выходного сигнала . Вы- сокая точность интегрирования объясняется тем, что интеграл заменен в данном устройстве конечной суммой.

3то позволяет избежать применения

3Q дрейфующих УПТ, повысить чувствительность интегратора. Связь входного сигнала с генератором тактовых

, импульсов позволяет еще более снизить дрейфы выходного сигнала.

35 Формула изобретения

=. е элемент задержки с входом сброса интегратора с обнуланием (3). Однако использование линейного интегратора не позволяет обеспечить необходимой точности интегрирования во всех . режимах работы.

Целью изобретения является повышение точности интегрирования.

Это достигается тем, что, в интегратор, содержащий первый запоминаюций блок, выход которого подключен к первому входу первого сумматОРа, второй запоминающий блок

I подключенный к выходу первого сумматора, генератор тактовых импульсов, вход которого подключен . к вхоцу интегратора и к входу первого запоминающего блока, и ключи, введены третий запоминающий блок, второй сумматор, два элемента И и триггер, причем вход третьего запоминаюцего бло ка подключен к выходу первого сумматора, выходы второго и третьего запоминающих блоков через первый и второй ключи соответственно соединены с вхо-дами второго сумматора, выход которого является выходом интегратора и подклю чен к второму входу первого сумма: тора, выход генератора тактовых импульсов подключен к управляющему входу первого запоминающего блока, к первым входам первого и второго

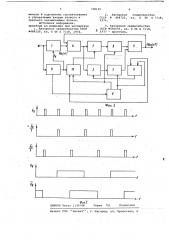

-элементов И и к входу триггера, выходы которого соединены с вторыми входами элементов И с управляющими входамй ключей, выходы первого и второго элементов И подключены соответствено к управляющим входам второго и третьего запоминающих блоков ., На фиг.1 представлена структурная блок-схема интегратора; на фиг.2 даны временные диаграммы работы интегратора.

Интегратор содержит запоминающие блоки 1-3, сумматоры 4 и 5, ключи б и 7, генератор 8 тактовых импульсов, триггер 9 и элементь1 И

10 и 11.

Интегратор работает следующим образом.

Входное воздействие U „ (t) квантуется по времени на запоминающем блоке 1, Затем сигнал U „(nt) эа -поминаетсй попеременно, в соответствии с разрешающими импульсами элементов И 10 и 11 на запоминающих блоках 2 и 3. Запоминающие блоки 2 и 3, а также ключи б и 7 работают в соответствии с диаграммами фиг.2. Таким образом, в момент запоминания на один и".; запоминающих блоков приходит просуммированный сигнал U „(n T) + < (— " т)

Следовательно, запомийающие блоки

2 и 3 попеременно помнят задержанную на два периода квантования сумсрр амплитуд входного воздействия.

На сумматоре 5 происходит повременное сложение этих сумм, в результате чего выходной сигнал имеет вид

Интегратор, содержаций первый запоминающий блок, выход которого подключен к первому входу первого сумматора, второй запоминающий блок, подключенный к выходу первого сумматора, генератор тактовых импульсов, вход которого подключен к входу интегратора и к входу первого запоминающего блока и ключи, 45 отличающий с я тем, что, с целью повышения точности интегрирования, в него введены третий эапоминаюций блок, второй сумматор, два элемента И и триггер, причем

$p вход третьего запоминающего блока подключен к выходу первого сумматора, выходы второго и третьего запоминающих блоков через первый и второй ключи соответственно соединены с входами второго сумматора, выход которого является выходом интегратора и подключен к второму входу первого сумматора, выход генератора тактовых импульсов подключен к управляющему входу первого

60 запоминаюцего блока, к первым входам первого и второго элементов И и к входу триггера, выходы которого соединены с вторыми входами элементов И и с управляющими входами клю65 чей, выходы первого и второго эле728135

Т) o gy

2 фиг.2

ЦНИИПИ Заказ 1139/48 Тираж 751 Подписное

Филиал ППП Патент,, г. Ужгород, ул. Проектная, 4 ментов И подключены соответственно к управляющим входам второго и третьего запоминающих блоков.

Источники информации, принятые во внимание при экспертизе

1 . Авторское свидетельство СССР

9489120, кл G 06 G 7/18, 1974.

2. Авторское свидетельство

СССР Р 498725, кл, G 06 G 7/18, 1974.

3. Авторское свидетельство

СССР 9556655, кл. G 06 G 7/18,,1977 — прототип.