Интегратор с управляемым ограничением выходного сигнала

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

<,, 744631 (6) ) Дополнительное к авт. свид-ву—

{22) Заявлено 180478 (21) 2606608/18-24 с присоединением заявки № (23) Приоритет—

G G 7/18 осударственный комитет

СССР по делам изобретений и открытий

Опубликовано 3006.80. Бюллетень ¹ 24

Дата опубликования описания 300680 (53) УД(681.335 (088. 8) (72) Авторы изобретения

В.A.Ñàìñoíoâ и P.H.×åpíûøåí

Ордена Ленина институт Проблем управления (71) За явитель (54) ИНТЕГРАТОР С УПРАВЛЯЕМЫМ ОГРАНИЧЕНИЕМ

ВЫХОДНОГО СИГНАЛА

Изобретение относится к автоматике и вычислительной технике.

Известны интеграторы с управляеьым ограничением выходного сигнала, в состав которых входят основной операционный усилитель, входной резистор, интегрирующий конденсатор и управляемая нелинейная цепь обратной связи. Для управления режимом )() работы интеграторы содержат ключи..

В одном из этих интеграторов параллельно интегрирующему конденсатору включен диод с дополнительным смещением, которое создано резистив- ным делителем, включенным между выходом интегратора и источником .опорного напряжения (1).

Такое включение ограничивающего диода не только не обеспечивает высокую точность ограничения, но ухудшает точностные характеристики интегратора в линейном режиме.Это ухудшение вызвано наличием тока утечки у закрытых диодов, 25

Известен также интегратор, в кото рый введены два вспомогательйых усилителя (один для реализации ограничения максимальной величины, второйминимазтьной) . Выходы вспомогательных ЗО неинвертирующих усилителей связанй с суммирующим входом основного операционного усилителя (ОУ) через диодные цепи. На вход вспомогательного усилителя подается разность выходного напряжения интегратора и напряжения ограничения. При превышении величины выходного сигнала уровня ограничения, вспомогательный усилитель обеспечивает дополнительный ток на суммирующем входе основного ОУ, который по величине равен входному току интегратора, но противоположной по направлению. При выполнении этого условия прекращается заряд конденсатора интегратора (2).

Недостатком этого типа интеграторов является наличие значительной динамической ошибки, возникающей при переходе схемы из линейного режима (режим интегрирования) в режим ограничения и наличие дополнительной статической ошибки, обусловленной конечностью коэффйциента усиления вспомогательного усилителя.

Наиболее близким техническим решением к предлагаемому является интегратор с управляемым уровнем ограничения выходного сигнала, со744631 держащий ОУ, интегрирующий конденсатор, включенный между выходом Оу, являющимся выходом интегратора, и суммирующим входом операционного усилителя, соединенным через цепочку иэ последовательйо соединенных раэмыкающего ключа и входного масштабного резистора с источником входного сигнала, H цепь сравнения, выполненную на двух последовательно соединенных резисторах и включенную между источником сигнала ограничения и выходом интегратора, вспомогательные усилители и диоды (3).

В линейном режиме, т.е. когда величина выходного сигнала меньше абсолютной величины уровня ограничения, напряжения на выходах вспомогательных усилителей близки к О, Это необходимо, чтобы .снизить ошибку,: обусловленную наличием тока утечки диода, соединяющего выход вспомога- тельного усилителя с суммирующим входом. При незначительном превышении выходного уровня интегратора величины сигнала ограничения на входе соответствующего вспомогательного уси лителя изменяется знак входного сигнала. Это приводит к увеличению выходного напряжения вспомогательного усилителя. Автоматически устанавливается такая величина напряжения, чтобы ток через диод равнялся по . величине входному току. При этом не будет причины для дальнейшего увелийения напряжения на выходе интегратора. Превышение выходного уровня, при котором устройство переходит в режим ограничения, определяется ве.личиной коэффициента усиления,вспомогательного усилителя, Недостатком интегратора с упранляемым уровнем ограничения является сравнительно большая статическая и динамическая ошибка в режиме ограничения, а также сложность системы.

Цель изобретения — повышение точности н режиме ограничения.

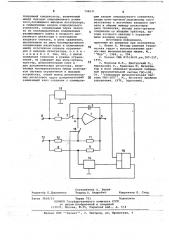

Цель достигается тем, что интегратор с управляемым ограничением содержит дна нуль-органа, триггер, дополнительный ключ и дна дополнительных резистора, включенных последовательно между источником сигнала ограничения и выходом устройства, общий выход дополнительных резисторов через дополнительный замыкающий ключ соединен с суммирующим входом ОУ, входы нульорганов подключены соответственно к источнику входного сигнала и общему выводу реэисторон цепи сравнения, выходы нуль-органов соединены со-входами триггера, выходы которого связаны с управляющими входами ключей, На чертеже предстанлена структурная схема интегратора с управляемым ограничением выходного сигнала.

ИнтегРатор содержит ОУ 1, интегрирующий конденсатор 2, который вклю65

Интегратор с управляемым ограничением выходного сигнала, содержащий операционный усилитель, интечен между ныходом 3 ОУ 1, служащим выходом устройства, и суммирующим входом 4 ОУ 1, входной масштабный резистор 5, один выход которого подключен к источнику 6 входного сигнала а другой — через размыкающий ключ 7 связан с суммирующим входом 4 ОУ, цепь сравнения, состоящую из резисторов 8 и 9, два последовательно соединенных дополнительных резистора 10 и 11, включенных между источниками 12 сигнала ограничения и выходом 3, замыкающий ключ

l3, который включен между суммирующим входом 4 ОУ 1 и общим выводом резисторов 10 и 11, два нуль-органа, первый 14 из которых подключен к об@ему выводу резисторов 8 и 9, а второй 15 — к источнику 6 входного сигнала и триггер 16, входы которого подключены соответственно к выходам

20 нуль -органов 14 и 15, а выходы соединены соответственно с управляющими входами ключей 7 и 13.

Интегратор работает следующим образом.

Когда величина выходного напряже— ния на входе достигает величины уроння ограничения, срабатывает нульорган 14. В результате этого перебрасывается триггер 16 и происходит переключение ключей 7 и 13. Входной резистор 5 отключается от суммирующего входа 4 ОУ 1 и устройство переходит н режим инерционного звена с входным сигналом, равным уровню ограничения, и напряжением на конденсаторе 2, равным также уровню ограничения. Поэтому в системе не происходит никаких переходных процессов.

Для того, чтобы изменился знак

40 производной выходного напряжения интегратора, т.е . для того чтобы интегратор вышел из области ограничения, необходимо чтобы изменился знак входного тока, Изменение знака входного тока и определяет нуль-орган

15. При переключении этого нуль-органа перебрасынается триггер 16 и схема переходит в режим интегратора.

Таким образом, предлагаемое устройстно полностью реализуется на стандартных элементах (операционные. усилители, компараторы, триггеры), не требует введение дополнительных цепей коррекции амплитудно-частотных характеристик усилителей, содержит меньшее число радиокомпонентов по сравнению с известным, но при этом обеспечивает более высокую статическую и динамическую точность в режиме ограничения.

Формула изобретения

744631

Составитель С. Белан

Техред О. Андрейко

Корректор Н. Стец

Редактор Е.Дорошенко

Заказ 3818/15 Тираж 751 Подписное

БНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 5/4

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4 грирующий конденсатор, включенный между выходом операционного усили-.. теля,являющимся выходом интегратора, и суммирующим входом операционного усилителя, соединенным через чепочку из последовательно соединенных размыкающего ключа и входного масштабного резистора с источником входного сигнала, и цепь сравнения, выполненную на двух последовательно соединенных резисторах и включенную между источником сигнала ограничения и выходом интегратора, о т л ич а ю шийся тем, что, с целью повышения точности в режиме ограни-; чения, он содержит два нуль-органа триггер, дополнительный ключ и .два дополнительных резистора, включенных последовательно между источником сигнала ограничения и выходом устройства, общий вывод дополнительных резисторов через дополнительный 20 замыкающий ключ соединен с суммирующим входом операционного усилителя, входы нулЬ-органов подключены соответственно к источнику входного сигнала и общему выводу резисторов цепи сравнения, выходы нуль-органов соединены со входайи триггера, вы ходы которого связанй с управляющими входами ключей .

Источники информации, принятые во внимание при экспертизе

1. Левин Л. Методы решения технических задач с использованием аналоговых вычислительных машин ° М., Мир, 1966, с. 204.

2. Патент CUJA 93514635,кл.307-237, 1975.

3, Морозов В.П., Джигурский О., Марьянович С., Крашовац М. Интегратор и блок слежения-хранения гибридной вычислительной систем ГВС-100

° е

Ф

Сб ° Гибридная вычислительная система ГВС-100 . М., Институт проблем управления, 1976, (прототип) .