Множительно-делительное устройство

Иллюстрации

Показать всеРеферат

О П И С А И . изо БГеткййЯ.

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. сеид-ву (22) Заявлено 13. 09. 78 (2 t) 2665824/18-24 с присоединением заявим И9 (23) Приоритет—

Опубликовано 15.09.80. Бюллетень НВ 34

Дата опубликования описания 170980 (51)м К 3

9 06 Q 7/16

Государственный комитет

СССР по делам изобретений и открытий (5З) УДК 681 ° 335 (088.8) (72) Авторы изобретения

В. С. Твереэовский и С. С. Голощапов (71) Заявитель (54 ) МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО

Изобретение относится к аналоговой вычислительной технике и может быть использовано в аналоговых, аналого-цифровых устройствах и измерителях.

Известно множительно-делительное устройство j 1), которое содержит три ключевых элемента, управляемых коммутатором, и два ключевых элемента, управляемых тактовым генератором, дифференциальный усилитель, четыре фиксатора уровня, управляемый элемент, преобразователь на" пряжение-ток, измерительный блок, источники опорного и входных сигналов, переключатель режима "умножение-деление".

К недостаткам этого устройства следует отнести его низкую точность ,при делении слабых сигналов (вели- 20 чина которых составляет доли миливольт), которые существенно отличаются (в десятки раэ) один от другого.

К недостаткам э|. ого устройства мож но отнести его низкую точность при использовании его в качестве делительного устройства (один из сомножителей является постоянной величиной) для деления сигналов низкого уровня, существенно отличающихся между собой

Наиболее близким по технической сущности к предложенному является множительно-делительное устройство 21, содержащее реверсивный счетчик, подключенный входами через входной вентиль к генератору тактовых импульсов, выходом к первому входу циф-,,роаналогового преобразователя, выход которого подключен к первому входу компаратора, второй вход которого соединен с первой входной клеммой устройства, а выход - с управляющим входом входного вентиля, в его состав. также входят схема И, двухпозициоиный ключ, выходной ключ, запоминающий блок и генератор синхронизации, выход которого соединен с управляемыми входами двухпоэиционного и выходного ключей и схемы И, второй вход цифроаналогового преобразователя подключен через двухпоэиционный ключ ко второй и третьей входным клеммам устройства, а внход через выходной ключ к запоминающему блоку, выход которого соединен с выходной клеммой устройства, а генератор тактовых импульсов соединен через схему И с входным вентилем.

763915 по величине. На выходе устройства будет вырабатываться сигнал

Ug

Второе слагаемое в правой части представляет собой погрешность устройства, обусловленную нелинейностью характеристики делителя при делении сигналов низкого уровня, существенно отличающихся по величине один от другого.

Целью изобретения является повышение точности устройства, при делении малых сигналов, существенно отличающихся один от другого по величине.

Эта цель достигается за счет того, что множительно-делительное устройство, содержащее блок управления, выход которого подключен ко входу первого запоминающего регистра, вы» ход запоминающего регистра подключен ко входу первого усилителя с регулируемым коэфФициентом усиления, выход которого соединен со входом блока сравнения, дополнительно содержит усилитель уровня, второй усилитель с регулируемым коэффициентом усиления, коммутирующий элемент, второй запоминающий регистр, коммутатор входных сигналов и коммутатор опорных сигналов, причем выход коммутатора входных сигналов подключен ко входу усилителя уровня, выход которого подключен ко входу второго усилителя с регулируемым коэффициентом усиления, к управляющему входу которого подключен выход коммутирующего элемента, вход коммутирующего элемента подключен к выходу второго запоминающего регистра, выход второго усилителя с регулируемым коэффициентом усиления подключен ко входу первого усилителя с регулируемым коэффициентом усиления, выход которого является выходом устройства,.выход коммутатора опорных сигналов подключен ко входу блока сравнения, выходы блока управления .подключены к управляющим входам коммутатора опорных сигналов, коммутатора входных сигналов, блока сравнения, коммутирующего элемента и второго запоминающего регистра.

30

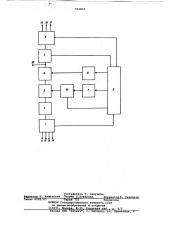

На чертеже представлена схема предлагаемого устройства.

Устройство содержит коммутатор входных сигналов 1, усилитель уровня 2, первый и второй усилители с регулируемыми коэффициентами усиления 3, 4, блок сравнения 5, коммутатор опорных сигналов 6, первый и второй запоминающие регистры 7,8, 60 блок управления 9, коммутирующий эле.мент 10, клеммы входных сигналов 11, 12, клеммы калиброванных сигналов

13, 14, клеммы опорных сигналов 15, 16, 17, клемму выходного сигнала 18.

Усилители с регулируемыми коэффициентами усиления 3 и 4 могут представлять собой усилитель постоянного тока (УПТ) с сопротивлением в цепи отрицательной обратной связи и управляемой цифровой проводимостью на входе. Коэффициент усиления такого усилителя зависит от кода, посту1чающего на входы ключей цифровой управляемой проводимости.

Усилитель 3 отличается от усилителя 4 тем, что в нем параллельно цифровой управляемой проводимости включена неуправляемая проводимость и коэффициент усиления этого усилителя, при отключении управляемой проводимости с помощью коммутирующего элемента 10, определяется этой неуправляемой проводимостью.

Коммутирующий элемент представляет собой набор ключей, которые коммутируют выходной код регистра 7 на вход управляемой проводимости усилителя 3.

Устройство работает следующим образом.

В исходном состоянии на выходах коммутаторов 1 и 6 сигналы отсутствуют, запоминающие регистры 7 и 8 сброшены в нулевое состояние, на выходах усилителей 2,3 и 4 сигналы также отсутствуют.

Рассмотрим работу устройства, при делении двух сигналов, которые имеют низкий уровень и существенно отличаются один от другого

Операция деления осуществляется в четыре этапа. На первом этапе коммутатор 1 подключает на вход усилителя уровня 2 калиброванный сигнал

U«, на коммутирующий элемент 10 с блока управления 9 подается запрещающий потенциал. Усилители 2 и 3 имеют коэффициенты усиления K è К соответственно. Чо команде, поступающей с блока управления 9, регистр

8 своими выходными сигналами изменяет коэффициент усиления усилителя

4 таким образом, чтобы сигнал на его выходе был равен опорному сигналу

0о-, подключенному коммутатором 6 ко входу блока сравнения 5 с клеммы

15. Этот момент фиксирует блок сравнения, который вырабатывает импульс напряжения, поступающий на блок управления. В этом случае будет справедливо равенство

"а К1 К "Ъ Uv» (t) где К - коэффициент.усиления усилителя 4. Код, соответствующий коэффициенту усиления К> запоминается в регистре 8.

На втором этапе работы коммутатор 1 подключает ко входу усилителя

2 калиброванный сигнал U, с клеммы

12. Так как величина Ц тсущественно отличается от U<,, то коэффициент усиления усилителя уровня 2 будет отличаться от К, на величину b,K .

763915

По команде, поступающей от блока управления 9 на регистр 7, последний, изменяя свое состояние, управляет .усилителем 3 таким образом, чтобы сигнал на клемме 18 был равен опорному напряжению U подключенному к блоку 5 с клеммы 16 коммутатором 6, при этом блок управления вырабатывает разрешающий потенциал, поступающий на коммутирующий элемент 10, и код регистра 7 поступает на упса равляющий вход усилителя 3.

В этот момент будет справедливо равенство

"кй " д" )(" +д )к -0 (5

Код, соответствующий коэффициенту усиления К +ЬК, хранится в регистре 7.

На третьем этапе по команде, поступающей с блока управления 9, коммутатор 1,. подключает сигнал U рав- 20 ный делителю, ко входу усилителя 2 с клеммы 13, а коммутатор 6 коммутирует опорный сигнал U с клеммы 17 на вход блока сравнения 5. Блок управления запрещает поступление кода, храни- 25 мого в регистре 7 через коммутирующий элемент 10, на управляющий вход усилителя 3. Усилители 2 и 3 будут иметь коэффициенты усиления К„ и К соответственно. ЗО

Входной сигнал О,, усиленный усилителями 2 и 3, поступает на нход усилителя 4. По команде от блока управления регистр 8 изменяет свое состояние, который, в свою очередь, изменяет коэффициент усиления усилителя 4 до наступления равенства

U> К„ К1(К aK ) = u,, (3)

Код, соответствующий коэффициенту усиления К+дКЪ хранится в регистре 8.

Иа четвертом этапе по команде, пос- 40 тупающей с блока управления, коммутатор 1 подключает ко входу усилителя

2 сигнал U<(делимое) с клеммы 14.

Так как U по величине близкое к

Ок, то коэффициент УсилениЯ Усили- . 45 теля 2 будет равен К +дК„ . По сигналу с блока управлейия, поступающему на коммутирующий элемент 10, регистр 7 устанавливает коэффициент

Усиления усилителя, Равный К1+дК, 5а сформированным на втором этапе работы.

На клемме выходного сигнала получим напряжение

0 „=0,(к,дк,ик,.дк,)(к дк, I"2

Уравнение (4) можно переписать с учетом (1), (2) и (3) 2 Оо<о» <е

Ьык (о1 Ок1 (52

В уравнении (5) величина 60 <о» Оа» Ок, =со з1, О1 )К поскольку члены, входящие в выражение — постоянные величины. Из ныражения (5) видно, что результат деления двух сигналов низкого уровня, которые значительно отличаются по величине один от другого, не зависит от нелинейности коэффициента усиления усилителя 2.

Предлагаемое устройство можно использовать для определения коэффициента перекрытия нерхрезких варикапон, у которых этот параметр может равняться нескольким десяткам единиц, а уровни сигналон, которые используются при определении коэффициента, ранны единицам и десяткам микровольт.

Кроме того, подавая на входы 1117,переменные величины, устройство мо>кно испольэовать для вычисления выражения согласно формуле (5) ° формула изобретения

Множительно-делительное устройство, содер>кащее блок управления, выход которого подключен ко входу первого запоминающего регистра, выход запоминающего регистра подключен ко входу первого усилителя с регулируемым коэффициентом усиления, выход которого соединен со входом блока сравнения, о т л v ч а ю щ е е с я тем, что, с целью повышения точности оно дополнительно содержит усилитель уровня, второй усилитель с регулируемым коэффициентом усиления, коммутирующий элемент, второй запоминающий регистр, коммутатор входных сигналов и коммутатор опорных сигналов, причем выход кока утатора входных сигналов подключен ко входу усилителя уровня, выход которого подключен ко входу второго усилителя с регулируемым коэффициентом усиления, к управляющему входу которого подключен выход ко>мутирук>щего элемента, вход коммутирующего элемента подключен к выходу второго запоминающего регистра, выход нторого усилителя с регулируемым коэффициентом усиления подключен ко входу первого усилителя с регулируемым коэффициентом усиления, выход которого является выходом устройства, выход коммутатора опорных сигналов подключен ко входу блока сравнения, выходы блока управления подключены к управляющим входам коммутатора опорных сигналов, коммутатора входных сигналон, блока сравнения, коммутирующего элемента и второго запоминающего регистра.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 504204, кл. G 06 G 7/16, 19 16.

2. Анторское свидетельство СССР

Р 435530, кл G 06 Я 7/16, 1974 (прототип).

763915 ф 1Ф !7

gy 51J1

Тираж Подписное

ВНИИПИ Государственного комитета СССР по делам иэобретений и открытий

113035 Москва Ж-35 Ра окая наб. д. 4 5 акаэ

Филиал ППП Патент, г. Ужгород, ул. Проектная, Составитель Т. Сапунова р акто Н. Каменская Техред Н.Ковалева Ко екто В. Синицкая