Измеритель частоты гармоническогосигнала

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. саид-ву(22) Заявлено 080179 (21) 2731788/18-21

Союз Советских

Социалистичесних

Республик () 813289 З1>М. К .

G 01 R 23/00 с присоединением заявки ¹

Государственный комитет

СССР ио делам. изобретений н открытий (23) Приоритет

Опубликовано 15.0381. Бюллетень Йо 10

Дата опубликования описания 1Ы 381 (53) УДК 621. 317 (088.8) (72) Авторы изобретения

Е. И. Дорохов, Н. A. Иванов, В. Ы. Шеваль, и Е.П. Миронов (71) Заявитель (54) ИЗМЕРИТЕЛЬ ЧАСТОТЫ ГАРМОНИЧЕСКОГО СИГНАЛА

1, Изобретение относится к электроизмерительной технике и может быть использовано в информационно-измерительных системах.

Известны устройства для измерения частоты, содержащие. блок дифференцирования сигнала L1)

Недостатком этих устройств является относительно малый диапазон рабочих частот.

Известно устройство для измерения частоты синусоидального напряжения, содержащее пороговое устройство, ключ, дифференцирующую и интегрирующую цепи, входы которых соединены со входом устройства, а к их выходам через детекторы подключены аналогоцифровой преобразователь и индикатор

У фазосдвигакщую цепь, вход которой соединен со входом устройства, причем к выходу детектора, подключенного на выходе 4азосдвигакщей цепи, подсоединено пороговое устройство, выход которого через ключ связан с раэрешакшим входом аналого-цифрового преобразователя (23.

Однако в данном устройстве при увеличении частоты измеряемого сигнала уменьшается амплитуда сигнала на выходе интегрирукщей цепи, что поз- ЗО воляет измерять частоту только в диа пазоне не более двух декад.

Цель изобретения — расширение диапазона измерения частоты гармонического сигнала.

Поставленная цель достигается твм, что в измеритель частоты гармонического сигнала, содержащий диффервнциатор, пороговый блок и ключ, дополнительно введены усилитель с дискретной регулировкой коэффициента усиления, блок вццеления модуля, диффервнциатор, ковяутатор, ключ, два диода, два элемента памяти, усилитель с плавной регулировкой коэффициента усиления, блок сравнения, указатель диапазонов, при этом усилитель с дискретной регулировкой коэффициента усиления, блок вццеления модуля, основной дифференциатор, пороговый блок и дополнительный дифференциатор соединены последовательно, выход первого элемента памяти соединен со входом коммутатора, выход которого подключен к управляющему входу усилителя с дискретной регулировкой коэффициента усиления и к первому входу . указателя диапазонов, выход дополнительного дифференциатора через диоды соединен с управляющими входаюж клю813289 чей, выход блока выделенйя модуля соединен со входом основного ключа, .выход которого подключен ко входу второго элемента памяти, выход основного дифференциатора соединен со входом дополнительного ключа, выход которого подключен ко входу пер)вого элемента памяти, выход второго элемента памяти соединен со входом усилителя с плавной регулировкой коэффициента усиления, выход которого подключен к первому входу блока сравнения, а второй вход блока сравнения соединен с выходом первого элемента памяти, выход блока сравнения соединен с управляющим входом усилителя с плавной регулировкой коэффициента усиления и со вторым входом указателя диапазонов.

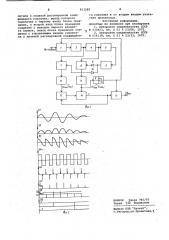

На фиг. 1 показана структурная схема измерителя, на фиг. 2 — эпюры напряжений на выходах соответствующих 20 узлов.

Измеритель содержит усилитель 1 с дискретной регулировкой коэффициента усиления, блок 2- выделения модуля, пороговый блок 3, дифференциаторы 4 и 5, коммутатор б, ключи 7 и 8, диоды 9 и 10, элементы 11 и 12 памяти, усилитель 13 с плавной регулировкой коэффициента усиления, блок 14 сравнения, указатель 15 диапазонов. Благодаря блску 2 измерение частоты происходит два раза за период, что повышает точность измерителя.

Измеритель частоты гармонического сигнала работает следующим образом.

Модуль входного сигнала дифференцируется на дифференциаторе 4, затем определяется з нак продифференцированного сигнала на пороговом блоке 3.

Полученный з накопеременный сигнал вновь дифференцируется на дифферен- 40 циаторе 5. Отрицательные импульсы, соответствующие моменту набора максимального значения входного сигнала

A oòêðûâàþò ключ 7, и это значение

А запоминается на элементе 11 памяти.45

Положительные импульсы, соответствующие моменту набора максимального значения перной производной входного сигнала А»,0 открывают ключ 8, и это значение А»>дзапоминается на эле- о менте 12 памяти. Следящая система, собранная на усилителе 13 с плавной регулировкой коэффициента усиления блока 14 сравнения, обеспечивает выполнение равенства. л 1 I

КиЬиiAwKÄ,(Pvar д 1=0>(<)-я(1) где К„ „- коэффициент усиления усилителя 13 с плавной регулировкой.

Соответственно Й =Kgb а выход" Я) ное напряжение равно КдИ. Так как следящая система состоит иэ малоинврционных звеньев, за счет высокого коэффициента усиления усилителя 13

К можно добиться высокой достовер0 ности выполнения равенства (1) при слежении в линейной зоне. A это соответствует высокой точности и линейности измерения частоты гармонического„сигнала. При пренышении сигналом А>>4) с элемента 12 памяти пороса С1 коммутатора б на усилитель 1 с дискретной регулировкой коэффици>ента усиления подается команда на . переход на новое значение коэффициента усиления; большее предыдущего.

Тем самым обеспечинается измерение частоты гармонического сигнала в широком диапазоне частот с поддержанием высокой точности измерения. Так как выходное напряжение измерителя одинаково в пределах диапазона измерений для всех диапазонов, для отличия диапазонов друг от друга используется указатель 15 диапазонов.

Предлагае1>ый измеритель частоты гармонического сигнала имеет преимущество по сравнению с известным устройством, так как он позволяет расширить диапазон измерения частоты гармонического сигнала, повысить точность и линеиность процесса измерения. .Формула изобретения

Измеритель частоты гармонического сигнала, содержащий дифференциатор, пороговый блок и ключ, о т л и ч а ю щ и и сятем,,что,,с целью расширения диапазона измерения частоты гармонического сигнала, в него дополнительно введены усилитель с дискретной регулировкой коэффициента усиления, блок выделения модуля, дифференциатор, коммутатор, ключ, два диода, два элемента памяти, усилитель с плавной регулировкой коэффициента усиления, блок сравнения, указатель диапазонов, при этом усилитель с дискретной регулировкой коэффициента усиления, блок выделения модуля, оснонной диффврвнциатор, пороговый блок и дополнительный дифференциатор соединены последовате»ьно, выход первого элемента памяти соединен со входом коммутатора, выход КоТ9р01 подключен к управляющему входу усилителя с дискретной регулировкой коэффициента усиления и к первому входу указ ателя диапазонов, выход дополнительного дифференциатора через диоды соединен с управляющими нходами ключей, выход блока выделения модуля соединен со входом основного ключа, выход которого подключен Ко входу второго элемента памяти, выход основ- ного диффервнциатора соединен со входом дополнительного ключа, выход которого подключен ко входу первого элемента памяти, выход второго элемента памяти соединен со входом уси813289

Фл =А

Фиг.1 лителя с плавной регулировкой коэффициента усиления, выход которого подключен к первому входу блока сравнения, а второй вход блока сравнения соединен с выходом первого элемента памяти, выход блока сравнения соединен с управлякщим входом усилителя с плавной регулировкой коэффициента усиления и со вторым входом указателя диапазонов.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 433423, кл. G 01 R 23/06, 1972.

2. Авторское свидетепьство СССР9 524138, кл. G 01 R 23/33, 1975, ВНИИПИ Заказ 765/55

Тираж 732 Подписное

Филиал ППП "Патент", r.Óæãîðîä,óë.Ïðîåêòíàÿ,4