Устройство для сложения п-разрядныхдесятичных чисел

Иллюстрации

Показать всеРеферат

(u>824203

Союз Советскик

Социалистически я

Республик

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. саид-ay— (22) Заявлено 1906 79 (23) 2807633/18-24 (51) м. кл.з

G 06 F 7/49 с присоединением заявки ¹ (23)Приоритет—

Гвсударствеивмй комитет

СССР ав делам извбретеиий и открытий

Опубликовано 2304316юллетень № 15

Дата опубликования описания 230481 (53) УДК 681.325 (088.8) (12) Авторы изобретения ремеэ"У г

Ю.М. Баженов, В.В. Роздобара и Г.В. (11) Заявитель (54) УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ И-РАЗРЯДНЫХ

ДЕСЯТИЧНЫХ ЧИСЕЛ

Изобретение относится к автомати ке и вычислительной технике и может быть использовано в специализированных вычислительных машинах.

Известно устройство для сложения десятичных чисел, содержащее п-последовательно соединенных в кольцо ши- . нами переноса двоично-десятичных декад сумматоров, D-триггеров, элементов ИЛИ, элементов И, элементов задержки (1)..

Одиако в известном устройстве при суммировании двух десятичных цифр, Сумма которых больше десяти, полученный в декаде код необходимо корректировать прибавлением к нему числа шесть. Это ведет к усложнению управления работой сумматора, к уменьшению его быстродействия. Кроме того, в декадах. таких сумматоров используется двоичная системз счисления, обладающая нулевой ошибкообнаруживающей способностью.

Наиболее близким к предлагаемому по технической сущности является уст„ройство для сложения десятичных чисел, в котором количество тактов коррекции результата суммирования равно единице (2).

Недостатками устройства являются необходимость коррекции результата и использование в декадах кода ошибкообнаруживающей способности., 4ель изобретения — упрощение устройства суммирования десятичных чисел, повышение надежности его работы.

Поставленная цель достигается тем, что в устройстве для сложения и-разрядных десятичных чисел, каждый i""é разряд которого содержит (i=1,2,3, ...,n) четыре трехвходовых .одноразрядных двоичных сумматора, первый и второй входы Которых подключены соответственно к входам i-ãî разряда первого и второго операндов, а выходы сумматора подключены к выходам i-ro paspsaa устройства, при20 чем, выход переноса первого трехвходового одноразрядного двоичного сум« матора i-го разряда соединен с третьим входом второго трехвходового одноразрядного двоичного сумматора

1-го разряда, выход переноса которого подключен к третьему входу третьего трехвхсдового одноразрядного двоичного сумматора i-ro разряда, выход переноса которого соединен с третьим

30 входом четвертого трехвходового од824203

4 норазрядного двоичного сумматора !

-го разряда, выход переноса которого подключен к выходу переноса 1-го разряда в (i+1)-й разряд устройства, содержит в каждом i-ом разряде элемент ИЛИ, выход которого подключен к третьему входу первого трехвходового одноразрядного двоичного сумматора

i-ro разряда, а первый и второй sxoды элемента ИЛИ подключены к выходам переноса соответственно второго и третьего трехвходовых одноразрядных двоичных сумматоров i-го разряда, В декадах сумматора для представ-, ления десятичных цифр используются фибоначиевые коды. Веса разрядов в декадах соответственно равны 1,2,3 и 5, причем младших разряд каждой декады соответствует разряду с весом 10 для предыдущей декады. Десятичные цифры в такой системе счисления имеют вид, представленный в таблице. 20

Вес раз ряда а5

0 0 1 0 1 0 0 1

1 0 0 0 0 1 0 0

0 1 1 0 0 0 1 1

0 0 0 1 1 1 1 1

0 1

0 0

0 0

0 0

При представлении используют нормальную форму чисел в фибоначиевой системе счисления: единица заносится в разряд, вес которого максимально близок (но не больше) к числу, затем, то же осуществляют для разности между числом и избранным весом и так далее (3). 40

Из табл. 1 видно, что в первых трех разрядах не могут стоять подряд две единицы, это свой тво используется для койтроля отсутствия искаженной информации.

Наибольшее число, которое можно представить с помощью нормальной формы в одной декаде 9, поэтому перенос из одной декады в другую соответствует десятичному переносу между разрядами, т.е. исключается коррекция

50 результатов сложения в декадах. При-. менение фибоначиевой системы счисления изменяет правила сложения кодов в разрядах декад. Сложение разрядов с весом 1 осуществляется по правилу 55

0 + 0 = 0

0 + 1 = 1

1 + 1 = 0 и формируется перенос в разряд с весом 2.

Сложение разрядов с весом 2 осу- щ ществляется но указанному чравилу и формируются переносы в разряды с весами 1 и 3. Сложение разрядов с весами 3 и 5 осуществляется по указанному правилу и формируются соответ/

Веса

Первая промежуточная сумма

0 0 0 0

Возникшие переносы

Перенос в старшую декаду

1 1 0 1

1 1 0 1

Код суммы

Код суммы после гормализации

0 0 1 1 ственно переносы в разряды с весами

1 и 5 и .10 (в следующую декад„,.

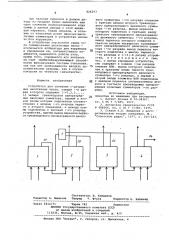

На чертеже приведена функциональная схема одной декады устройства, состоящая иэ четырех трехвходовых одноразрядных двоичных сумматоров

1-4 и элемента ИЛИ 5.

Одноразрядные сумматоры 1-4 представляют собой обычные в классической двоичной арифметике сумматоры, которые соответствуют разрядам с весами

1, 2, 3 и 5 и соединены между собой цепями переносов на основании правил суммирования в разрядах декады, т.е. перенос Р1 подается на вход суггматора 2; перенос Р2 — на вход сумматора 3 и через элемент ИЛИ на вход сумматора 1, перенос РЗ вЂ” на вход сумматора 4 и через элемент ИЛИ на вход сумматора 1, Р4 — перенос в следующую декаду.

Элемент ИЛИ 5 введен для того, чтобы сумматор 1 имел три входа. Он не искажает результата суммирования, так как одновременно переносы Р2 и

РЗ возникнуть не могут вследствие того, что на выходы подаются коды в нормальной форме, т.е. наличие единиц во втором, третьем разрядах декады одновременно невозможно. На схеме не показаны входы установки нуля.

Устройство работает следующим образом.

Одновременно на входы декады устройства поступают суммируемые десятичные цифры А и В в нормальной форме системы Фибоначи, формируются переносы и первая промежуточная сумма, затем осуществляется подсуммирование переносов, образование второй.промежуточной суммы и новых переносов и так до тех пор, пока не прекратится образование переносов и на выходах сумматоров, 1-4 не образуется код суммы. Если код суммы получится в нормализованной форме, то в дальнейшем этот код должен переписываться на норнормализатор, где с помощью операции свертки происходит нормализация кода результата.

Пример суммирования 9 + 9 = 18.

824203

Формула изобретения

Составитель В. Кайданов

Редактор А, Шишкина Техред - Ч. ф нта Корректор Н. Вабинец

Заказ 2112/71 Тираж 745 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

При наличии переноса в данную декаду иэ младшей нужно выполнить еще одно сложение нормализованного кода суммы в данной декаде с этой единицей переноса. Таким образом, в отличие от известных ранее двончно- деся тичных сумматоров в устройстве исклю5 ча этся коррекция.

В устройстве упрощается схема узла суммирования десятичных чисел исключается аппаратура для коррекции и управления ею, соответственно повышается надежность работы узла, кроме того, упрощается его контроль за.счет ошибкообнаруживающей способности фибоначиевой системы счисления, так как нет необходимости вводить до- 15 полнительные разряды, как в случае контроля по четности (нечетности).

Устройство для сложения п-разрядных десятичных чисел, каждый i-й разряд которого содержит (1=1,2,3,..., n) четыре трехвходовых одноразрядных двоичных сумматора, первый и второй входы которых подключены соответственно к входам i-го разряда первого и второго операндов, а выходы суммы подключены к выходам i-ro разряда устройства, причем выход переноса первого трехвходового одноразрядного двоичного сумматора i — ro разряда соединен с третьим входом второго трехвходового одноразрядного двоичного сумматора i-ro разряда, выход переноса которого подключен к третьему входу третьего трехвходового одноразрядного двоичного сумматора i ãî разряда, выход переноса которого соединен с третьим входом четвертого трехвхвдового одноразрядового двоичного сумматора i-ro разряда выход переноса которого подключен к выходу переноса

i-ro разряда в (i+1)-й разряд устройства, о т л и ч а ю щ е е с я тем, что, с целью упрощения устройства, оно содержит в каждом i îì разряде элемент ИЛИ, выход которого подключен к третьему входу первого трехвходового одноразрядного двоичного сумматора 1-го разряда, а первый и второй входы элемента ИЛИ подключены к выходам переноса соответственно второго и третьего трехвходовых одноразрядных двоичных сумматоров i-ro разряда.

Источники информации, принятые во внимание при экспертизе

1. Патент Японии Р 52-38367, кл. G 06 F 7/385, 1977.

2. Авторское свидетельство СССР

Р 488206, кл. G 06 F 7/385, 1975.

3. Стахов А.П. Введение в алгоритмическую теорию измерения. М., "Советское радио", 1977, с. 105-123.