Регистр

Иллюстрации

Показать всеРеферат

(54) РЕГИСТР

Изобретение относится к цифровой вычислительной технике и может явиться составной частью устройств ЭВМ.

Известен регистр, и котором для вы.полнения операций логического сложения и логического умножения требуются отдельные двухвходовые логические элементы типа И в каждом разряде $1), Однако это приводит к неэкономячному использованию оборудования.

Наиболее близким к предпагаемому но ® технической сущности является регистр, содержащий статические триггеры со схемами парафазной записи иэ двух элементов И и первого элемента НЕ, который !

9 по входу соединен с первым входом перваго элемента И, а по выходу — c первым входом второго элемента И, выход первого элемента И соединен с единичным входом триггера, а выход второго элемента И соединен с нулевым входом тригге.ра, причем, второй вход второго элемента

И соединен с выходом первого элемента

ИЛИ, первый вход которого соединен с,шиной установки регистра в ноль, à вто рой вход - с шиной команды эапнси. В известном регистре совмещено выполнение элементарных операций парафазной. запнсн и установки регистра в ноль на одних и тех же логических элементах схемы управления E2).

Недостатком известного регистра являются его ограниченные функциональные возмог ности, например, ье выполняются операции типа логического сложения н логического умножения.

Бель изобретения - расширение функциональных воэможностей регистра эа счет выполнения операций логкческого сложения и умножения и его упрощение.

Поставленная цель достнгается тем,что в регистр, содержащий первый элемент

ИЛИ и ячейки памяти, каждая из которых выполнена на статическом триггере, первом и втором элементах И н нервом эле менте НЕ, вход которого соединен с од ним из входов первого элемента И, а вы ход — с ожим из входов второго эле3 8601 мента И,выходы элементов И подключены ко входам статического. триггера, другие входы вторых элементов И ячеек памяти соединены с выходом первого элемента ИЛИ, один из входов которого соединен с шиной управления записью, другой вход первого элемента ИЛИ подключен к шине установки 0", и числовую шину, введены второй элемент ИЛИ, второй элемент HE и шину управления лот ическим сложением и умножением, а в каждую ячейку памяти введен третий элемент И, выход которого подключен ко входу первого элемента НЕ, один из входов третьего элемента И каждой ячейки памяти соединен с выходам второго элемента НЕ> другой вход третьего элемента И каждой ячейки памяти подсоединен к числовой шине;вход второго элемента HE соединен с шиной установки 0", третий вход первого элемента ИЛИ соеди20 нен с шиной управления логическим умножением, входы второго элемента ИЛИ подключены соответственно к шине управления записью и шине управления логическим сложением, а выходы второго элемента ИЛИ подсоединены к другому входу первого элемента И каждой ячейки памяти.

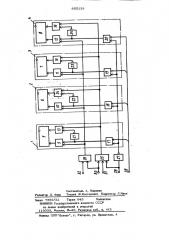

На чертеже изображена функциональная схема предлагаемого регистра.

Регистр содержит ячейки 1-4 памяти (покаэаны только четыре ячейки памяти регистра), которые выполнены на статических триггерах 5-8, первых элементах

И 9-12, вторых элементах И 13-16, третьих элементах И 17-20 и первых элементах HE 21-24, элементы ИЛИ 25 и

26, второй элемент HE 27, числовую шину 28, шину 29 установки «О», шину

30 управления записью и шины управления логическим сложением и умножением 31 к 32.

Как видно из чертежа, в регистре огсутствуют поразрядные логические элементы типа И-ИЛИ для выполнения операций логического сложения и логического умно- 45 жения. В предлагаемом регистре выполнение этих операций совмещено с выполнением элементарных операций парафазной записи и установки в ноль, при этом триггеры не имеют отдельного дополнительного 50 входа установки в ноль.

Регистр функционирует следующим образом.

Злементарная операция установки регистра в ноль осуществляется подачей сигнала на шину 29, в результате чего элементы И 17-20 закрываются и формируют на своем выходе "игнал логиче38 4 ского нуля, который через элементы HE

21-24 записывается в триггеры 5-8, так как команда установки в ноль через элемент ИЛИ 25 поступает на вторые вхо ды элементов И 13-16.

Операция парафаэной записи информации осуществляется подачей команды записи на шину 30, которая через элементы

ИЛИ 25 и 26 поступает на элементы И

9 и 13. При этом элемент HE 27 формируат разрешающий потенциал для элементов И 17-20, поскольку íà его вход по шине 29 установки "0" сигнал не поступает.

При выполнении операции логического сложения необходимо предусмотреть поразрядную запись только единичной информации, à поразрядную нулевую информацию записывать не нужно. Например, предположим, что в регистре находится числоХ„= 0011, а по числовой шине 28 через элементы И 17-20 поступает число

Х1= 1101. После выполнения операции логического сложения (9) должно получиться в регистре число Х =1 t l l, т.е.

Х =- X„V Х0= 0011V 1101 = 1111.

В предлагаемом схемном решении запись нуля в третий разряд не происходит, так как сигнал логического сложения по шине 32 через элемент ИЛИ 26 посту-. пает только на элементы И 9-12 единичных входов триггеров 5-8.

При выполнении операции логического умножения необходимо предусмотреть поразрядную запись только нулевой информации, а поразрядную единичную информацкю записывать не нужно. Например, если

Х.„=0011, а Х =1101, то после въщолнения логического умножения (h,) должно получиться число Х3 0001, т.е. Xg=

=Х„Л Хп-- 0011 Л 1101=0001. При формировании числа Х первую, вторую и четвертую ячейки памятк (разряды) у числа

Х должны остаться беэ изменения, а тре« ткй разряд необходимо переключить в нулевое состояние, поскольку у Х третий разряд равен нулю, Операция логического умножения выколняется подачей сигнала иа шину 31, которая через элемент ИЛИ 25 поступает на элементы И 13-16 нулевых входов триггеров 5-8 и устанавливает кх в ноль, если в соответствующем разряде числа Х имеется ноль. При выполнении операции логического сложения и умножения элемент НЕ 27 формирует разрешающий потенциал для элементов И 17-20.

Расширение функциональных возможностей устройства осуществляется дополнительным выполнением двух логических опе5 8601 раций, а именно: логического сложения и логического умножения. В известных регистрах на выполнение одной операции типа логического сложения к умножения используется один двухвходовой элемент И, объединенный по выходу элементом ИЛИ, т.е. на одну операцию требуется 1,S двухвходового элемента И,.а на две операции требуется 3 двухвходовых элемента типа

И-ИЛИ. В предлагаемом регистре опера« цкк логического сложения и умножения реализованы на элементах И схемы парафазной записи, т.е.,пля их реализации в каждом разряде не требуются дополнительные элементы, и экономия оборудования равняется 3-м элементам И на один разряд. Olaaao для совмещенного выполнения четырех операций: параллельной записи, установки в ноль, логического сложения и логического умножения требуется один дополнительный двухвходовый элемент И, поэтому общая экономия оборудования равна двум двухвходовым элементам И на

ollHH paapill регистра.

Формула изобретения

Регистр, содержащий первый элемент

ИЛИ и ячейки памяти, каждая из которых выполнена на статическом тратере, нервом и втором элементах И и первом элементе НЕ, вход которого соединен с одним иэ входов первого элемента И, а выхоа - с одним из входов второго элемента

И, выходы элементов И подключены ко входам статического триггера, другие входы вторых элементов И ячеек памяти сое38 6 динены с выходом первого элемента ИЛИ, один иэ входов которого соединен с шиной управления записью, другой вход кервого элемента ИЛИ подключен к шине установки

О, и числовую шину, о г л и ч а юшийся тем, что, с целью расширения функциональных воэможностей регистра за счет выпоааения операции логического сложения и умножения и его упрощения, в него введены второй элемент ИЛИ, второй элемент НЕ и шины управления логическим сложением и умножением, а в каждую ячейку памяти введен третий элемент И, выход которого подключен ко входу перва о элемента НЕ, один из входов гоетьего эле» мента И каждой ячейки памяти соединен с выходом второго элемента НЕ, другой . вход третьего элемента И каждой ячейки памяти подсоединен к числовой шине, вход второго элемента HE соединен с шиной установки О, третий вход первого элемента ИЛИ соединен с шиной управления логическим умножением, входы, второго элемента ИЛИ подключены соответственно к шине управления записью и шине управления логическим сложением, а выход второго элемента ИЛИ подсоединен к другому входу первого элемента И каждой ячейки памяти.

Источники информации, принятые во внимание при экспертизе

1. Папернов А. А. Логические основы

HBT. - М., Советское радио, 1972, с. 265.

2. Автсрское свидетельство СССР по эаавке М 2176032/18-24 ,кл, Q 11 С 19/00, 1975 (прототип).

Составитель А. Воронин

Редактор Л, Филь Текреи Ж.Кастелевич Корректор Л.Иван

Заказ 7556/32 Тираж 645 Подписное

ВНИИПИ Государственного комитета СССР ио делам изобретений и открытий

113035, Москва, Ж35, Раушская наб„д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4