Запоминающее устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВ ИТЕЛЬСТВУ оц875461

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. саид-ву (22) Заявлено 19028 0 (21) 2888652/18-24 с присоединением заявки Но (23) Приоритет

Опубликовано 231081, Бюллетень 89 39 (51)PA Клэ

G 11 С 19/00

ГосударстаениыЯ комитет

СССР по делам изобретенмЯ н открытяЯ (53) УДК 681.327 ° 66 (088.8) Дата опубликования описания 231081! .Ю.М. Баженов, Г,В, Кремоз и В. В. Роэдобара

I (72) Авторы изобретения! г

4 ( (71) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к вычисли тельной технике и может быть исполь зовано s вычислительных системах обработки данных.

Известен регистр, содержащий цепочку триггеров и выходной клапан, предназначенные для хранения и передачи информации (13 .

Недостатками известного устройства 1О является малая достоверность хранимой информации и невозможность обнаруживать ошибки, возникающие s процессе хранения, as-эа нулевой ошибкообнаруживающей способности кодов в классической двоичной системе счисления, с помощью которых представля ется информация в регистрах.

Наиболее близким к предЛагаемому по технической сущности является запоминающее устройство, которое содер- 26 ,жит цейочку триггеров и выходной клапан Г2) .

Недостатком данного регистра является малая достоверность хранимой информации и невозможность обнаружения ошибки.

Цель изобретения — расширение об-, ласти применения устройства за счет нормализации двоичного. кода Фибоиач» чи. 30

Поставленная цель достигается тем, что в запоминающее устройство, содержащее накопитель, блок управления и элемент И, выходы которого являют- ся выходами устройства, введены преобразователь кодов, блок контроля, триггер

:и элемант ИЛИ,первая группа входов которого соединена с информационными вхо,!дами устройства, вторая группа входов

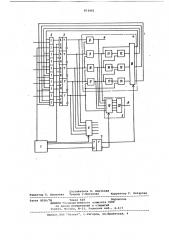

1 лемента ИЛИ подключена к первому выходу блока управления, второй выход которого соединен с первой группой входов накопителн, третья группа входов эле ивнта ИЛИ соединена с первой группой . выходов преобразователя кода, вторая группа выходов которого подключена к первой группе входов блока контроля, второй вход блока контроля соедийей с первым выходом триггера, вы . ходы накопителя соединены с первой группой входов преобразователя кодов, второй вход которого соединен со вторым выходом триггера, первая группа входов элемента И соединена с выходами накопителя, вторая группа входов соединена с третьим выходом блока управления,четвертый и пятый выходы которого подключены ко входам триггера. на чертеже изображена функцибналь- . ная схема устройства, 87 5461

Устройство содержит блок 1 управле ния, эл емен т ИЛИ 2, накопитель 3, преобразователь 4 кодов, блоу 5 контроля, элемент И 6, триггер 7.

Преобразователь 4 кода выполнен на

7-ми элементах И 8-14, трех элементах HE 15-17 и многовходовом элементе И 18.

Блок 5 контроля содержит многовходовой элемент И 19 и элемент ИЛИ 20.

Устройство работает следующим образом.

По сигналу от блока 1 управления все триггеры накопителя 3 обнуляются. По следующему сигналу блока 1 в накопитель 3 записывается через элемент HJIH 2 двоичный фибо- 15 наччиевый код. Следующим сигналом блока 1 триггер 7, находящийся в нулевом состоянии, переводится в единичное состояние, элемент И 8 открывается и устройство переводится в режим щ нормализации, в котором осуществляется приведение двоичного фибоначчиевого кода к нормальной форме, при которой в двух соседних разрядах кода не могут быть сразу две единицы.

Принцип работы преобразователя 4 кодов состоит в последовательном просмотре двоичного кода, начиная со старших разрядов. При .наличии единиц в двух соседних разрядах производится операция свертки, вид которой следующий

01011 . †.ненормализованный код

01011-01011-01100-10000

10600 — ненормализованный код.

Если единица находится в крайнем младшем разряде, то по свойству нормальных кодов эта единица заносится в предпоследний младший разряд, а крайний разряд обнуляется.

При наличии единицы в двух стар- 4р ших разрядах выдается сигнал переполнения . После того, как все возможные свертки осуществлены по сигналу блока 1, триггер 7 переходит в нулевое состояние, и закрывает пре- 4 .образователь 4, и устройство переходит в режим хранения.

В этом режиме осуществляется контроль двоичного кода, хранящегося в накопителе 3. При наличии одновременно двух единиц в соседних разрядах кода или при наличии единицы .в последнем младшем разряде на выходе блока 5 контроля появляется сигнал (Ь ошибки.

Таким образом, предлагаемое устройство позволяет расширить область ирименениМ, заключающуюся в хранении и передаче двоичной информации, нормализации двоичных кодов Фибонач-. чи и контроле хранимой информации.

Устройство позволяет значительно повысить достоверность хранимой информации по сравнению с известными устройствами. Если вероятность обнаружения ошибки типа 01, возникающей в процессе хранения информации, представленной в классической двоичной системе счисления в известных устройствах равна О, то, например, при хранении 40-разрядного кода Фибоначчи в предложенном устройстве вероятность ошибки, т.е. отношение числа обнаруживаемых ошибочных комбинаций к объему числа возможных двоичных комбинаций, равна 0,9999, т.е. обнаруживаются 99,99% переходов из разрешенной (нормальной) кодовой комбинации в любую возможную.

Формула изобретения !

Запоминающее устройство, содержащее накопитель, блок управления и элемент И, выходы которого являются выходами устройства, о т л и ч а ю щ е е с я тем, что, с целью расширения области применения устройства за счет нормализации двоичного кода

° Фибоначчи, в него введены преобразо ватель кодов, блок контроля, триггер и элемент ИЛЙ, первая группа входов которого соединена с информационными входами устройства, вторая группа входов элемента ИЛЙ подключена к первому выходу блока управления, второй выход которого соединен с первой группой входов накопителя, третья группа входов элемента ИЛЙ соединена с первой группой выходов преобразователя кода, вторая группа выходов которого подключена к первой группе входов блока контроля, второй вход блока контроля соединен с первым выходом триггера, выходы накопителя соединены с первой группой входов преобразователя кодов, второй вход которого соединен со вторым выходом триггера, первая группа входов элемента И соединена с выходами накопителя, вторая группа входов соединена с третьим выходом блока управления, четвертый и пятый выходы которого подключены ко входам триггера.

Источники информации, принятые во внимание при экспертизе

1. Каган Б.М. Электронные вычислительные машины и системы. М., "Энергия", 1979, с. 87.

2. Соловьев Г. И. Арифметические устройства, ЭБМ. М., "Энергия", 1978 с. 77 (прототип} .

87 5461

Составитель Л. Амусьева

Техред С.Мигунова Корректор Г. Назарова

Редактор Т. Киселева

Филиал,ППП "Патент", г.Ужгород, ул.Проектная, 4

Заказ 9356/78 Тираж 64 8 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5