Преобразователь двоично-десятичного кода в двоичный

Иллюстрации

Показать всеРеферат

Союэ Советскик

Социалистыческии

Республик

ОП ИСАНИЕ 888104

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6l ) Дополнительное к авт. свил-ву (22)-заявлено 280380 (21) 2900442/18-24 с присоединением заявки М (23) Приоритет

Опубликовано 0 7.1281. Бюллетень № 45 дата опубликования описания 07-1281 (51)М. Кл.

G 06 F 5/(1? твщдарстаанный комитет по делам нзабретеннй (53) УДК681. 325 (088, 8) N открытнй гВ.Ф. E вдокимов, И. Ф. Зубенко, P.

l0.A. Плющ и А. П. Стекан (72) Авторы изобретения.Институт электродинамики AH Ук (7l ) Заявитель (54 ) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОГО КОДА

В ДВОИЧНЫЙ

Изобретение относится к автоматике и вычи слител ьной техни ке и может быт ь использовано при построении двоичнодесятичных преобразователей.

Известен преобразователь двоичнодесятичных чисел в двоичные (1), содержащий двоичные полные сумматоры, включенные последовательно по нарастанию двоичных разрядов.

Недостаток известного устройства

10 состоит в большом обьеме аппаратуры.

Наиболее близким решением по технической сущности и достигаемому результату к изобретению является преобразователь двоично-десятичного ко15 да в двоичны" (2), содержащий блок суммирования, выполненный на многовходовых одноразрядных сумматорах, инФормационные выходы которых являются разрядными выходами преобразователя, н 20 а выход переноса i-го многовходового одноразрядного су лматора (i =1- (и-1) ), где и - число разрядов двоичного кода, соединен с входом переноса (1+1)— го многовходового одноразрядного сумматора, вход j- ro разряда (j =1+4) - ro десятичного разряда преобразователя (k=1+3) соединен с входами многовходовых одноразрядных сумматоров, в соответствии с весами единичных значений двоичного представления числа

2)-л 10к-4

Недостаток данного преобразователя состоит в относительно большой сложности, связанной с большим числом входов суммирующего блока.

Целью изобретения являются упрощение преобразователя и уменьшение его аппаратурных затрат.

Поставленная цель достигаетсп тем, что преобразователь двоично-десятичного кода в двоичный, содержащий блок суммирования, выполненный на многовходовых одноразрядных сумматорах, информационные выходы которых являются разрядными выходами преобразователя, а выход переноса I- ãî многовходового одноразрядного суюлатора (i =1 (и -1) ), 8104

88 4 разом, чтобы избыток над значением десятичного числа также был равен весу двоичного разряда. Например, десятичный вес 1000 заменяется на 1024+8=

=1000+32, Гашение избыточных чисел, введенных в суммирующий блок, осуществляется путем прибавления константы, вызывающей переполнение суммирующего блока.

Работу устройства проиллюстрируем на следующем примере

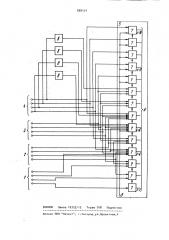

При поступлении на входы десятичного числа 1000, представленного в двоично-десятичном коде, на левый вход четвертой декады подается значение, равное 1. Левый вход четвертой декады соединен с входами многовходовых одноразрядных сумматоров 7 с номерами i--4 и 1 11, а также с одним из входов блока элементов НЕ 9, вход которого соединен с многовходовым одноразрядным сумматором с номером 1=6.

45

SS где n - число разрядов двоичного кода, соединен с входом переноса (i+1)го многовходового одноразрядного сумматора, вход j -ro разряда (j =1+4) k-го десятичного разряда преобразователя (k=1+3) соединен с входами многовходовых одноразрядных сумматоров, в соответствии с весами единичных значений двоичного представления числа

21 ".10" ", дополнительно содержит группу элементов НЕ, входы которых соединены соответственно с входами

q-го десятичного разряда преобразова- т еля (3< q . 10 t . +1+j) и входами мно го входовых одноразрядных сумматоров в соответствии с единичными значениями р младших разрядов двоичного представления числа 2 10 (где р " л номер старшего нулевого разряда), выход j-го элемента НЕ q-ãî десятичного разряда группы соединен с входом мн о го входо во го однор аз рядно го сумматора, s соот ветст вии с весом (р+1) -го разряда двоичного представления числа 2 "- 1 0 ", дополнител ьный вход введения константы преобразователя соединен с входом многовходового одноразрядного сумматора в соответствии с весом (р+1)-го разряда двоичного представления числа 10 à и с входами многовходовых одноразрядных сумматоров, с весами, большими веса (р+1)-го разряда, кроме многовходовых одноразрядных сумматоров, подключенных входами к выходам элементов НЕ группы.

На чертеже представлена блок-схема предлагаемого устройства на примере преобразования четырехраэрядного двоично-десятичного числа.

Преобразователь содержит входы 1-4, разделенные по тетрадам, соответствую щим разрядам десятичного числа, причем нулевым входам соответствуют ве,са 1, 10, 100, 1000, суммирующий блок 5, информационные выходы 6 преобразователя, многовходовые одноразрядные сумматоры 7, группу элементов

НЕ 8 и дополнительный вход 9 введения константы.

Алгоритм преобразования основан на замене десятичных весов, начиная с четвертой тетрады ближайшими большими значениями двоичных разрядов, причем последние дополняются таким о6В рассматриваемом случае на входы блока суммирования поступают следующие коды:

С вЂ” константа, поступающая с дополнительного входа 9 и равна:

С = 11111000100000, а - код, поступающий с входом 1-4 устройства и равный: а = 0001 00 0000 1000;

b - код, поступающий с выхода группы элементов НЕ 8 и равный

b = 00006111000000.

Результат на выходах 6 преобразователя равен сумме перечисленных выше кодов беэ учета переноса со старшего разряда

С + а + Ь = 1111l000100000

+ 00010000001000

00000111000000

00001111101000, который представляет входное число

1000 в двоичной системе счисления.

4исло, добавляемое к значению старшего двоичного разряда, равно младшим разрядам двоичного представления веса десятичного разряда. Причем эта группа разрядов ограничивается разрядом, имеющим нулевое значение в старшей группе разрядов. Действительно, для того чтобы получить число 1032 из числа 1000

1111101000 - 1000 1 32

10000001000 1032

8881

Необходимо вызвать переполнение при сложении. Для этого необходимо прибавить единицу в разряд, содержащий младшую единицу в группе, состоящую из одних единиц. Младшая группа разрядов числа 1000 и 1032 совпадает.

Квадратом выделен разряд, ограничивающий младшую группу разрядов.

Использование группы элементов НЕ и новых связей между компонентами вы- 10 годно отличает предлагаемое устройство от указанного прототипа, так как позволяет сократить общие аппаратурные затраты. Для приведенной на чертеже схеме устройства, предназна- 1$ ченного в качестве примера, для преобразования - четырехразрядного двоично-десятичного числа в двоичный код

:количество входов для многовходовых одноразрядных сумматоров сократилось. 2ф

Так, например, в многовходовом одноразрядном сумматоре с номером i=11 по схеме прототипа необходимо, без учета количества входов для организации многоуровневого переноса с много- 2$ входового одноразрядного сумматора с номером i=10, четыре входа. В предлагаемом устройстве, как видно из схемы, задействовано всего два входа.

Аналогично, в схеме прототипа для 30 многовходового одноразрядного сумматора с номером i=9 необходимо шесть входов, а в предла гаемом устрой ст ве задействовано три входа, Общая экономия коли чест ва входов в предлагаемом устройстве без учета многоуровневого переноса составляет шесть входов.

Формула изобретения

Преобразователь двоично-десятичного кода в двоичный, содержащий блок суммирования, выполненный на многовходовых одноразрядных сумматорах, ин- $ формационные выходы которых являются разрядными выходами преобразователя, а выход переноса I го многовходового одноразрядного сумматора (i=1 (п-l)), где n - число разрядов двоичного кода

04 Ь соединен с входом переноса (i+1)-го многовходового одноразрядного сумматора, вход j — го разряда (1= I+4) I,— го десятичного разряда преобразователя, (к=1-;3) соединен с входами многовходовых одноразрядных сумматоров в соответствии с весами единичных значений двоичного представления числа

:2 1. 101 ", отличающийся тем, что, с целью упрощения преобразователя и уменьшения его аппаратурных затрат, он содержит группу элементов НЕ, входы которых соединены соответственно с входами q-го десятичного разряда преобразователя (3

<в) где m - число десятичных разрядов преобразователя, 1-й вход q-ro десятичного разряда преобразователя соединен с входом m-го многовходового одноразрядного сумматора (m=-gl og >

101 " (+1+) ) и входами многовходовых одноразрядных сумматоров, в соответствии с единичными значениями р младших разрядов двоичного представления числа 23 ". 10 т " (где р — номер стаьшего нулевого разряда), выход j-ro элемента НЕ q-го десятичного разряда группы соединен. с входом многовходового одноразрядного сумматора в соответствии с весом (р+1)-го разряда двоичного представления числа

21 ". 10 ., дополнительный вход введения константы преобразователя соединен с входом многовходового одноразрядного сумматора в соответствии с весом (р+1)-го разряда двоичного представления числа 10т-" и с входами многовходовых одноразрядных суммато" ров с весами, большими веса (р+1)-го разряда, кроме многовходовых одноразрядных сумматоров, подключенных входами к выходам элементов НЕ группы.

Источники информации, принятые во внимание при экспертизе

1. Патент США N 3705299, кл. 235-155, опубли к. 1975.

2. Авторское свидетельство СССР

У 451991 кл. G 06 F 5/02 1973 (прототип).